## Accurate Simulation of EV/HEV Power Electronics Switching Events for HIL Testing

Joel Van Sickel Application Engineer

#### **Overview**

- 1. Hardware-in-the-loop (HIL) overview

- 2. Review of a system level model of a motor and inverter in Simulink

- 3. Use of HDL Coder to generate floating-point HDL from the Simulink model to achieve 1 MHz simulation (1 µs time-step)

- 4. HIL simulation using Simulink Real-Time and Speedgoat target hardware

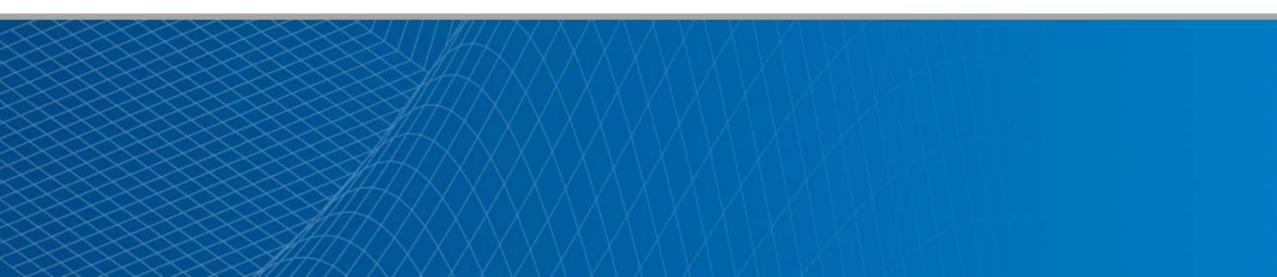

#### What is HIL

#### Demo

#### Demo

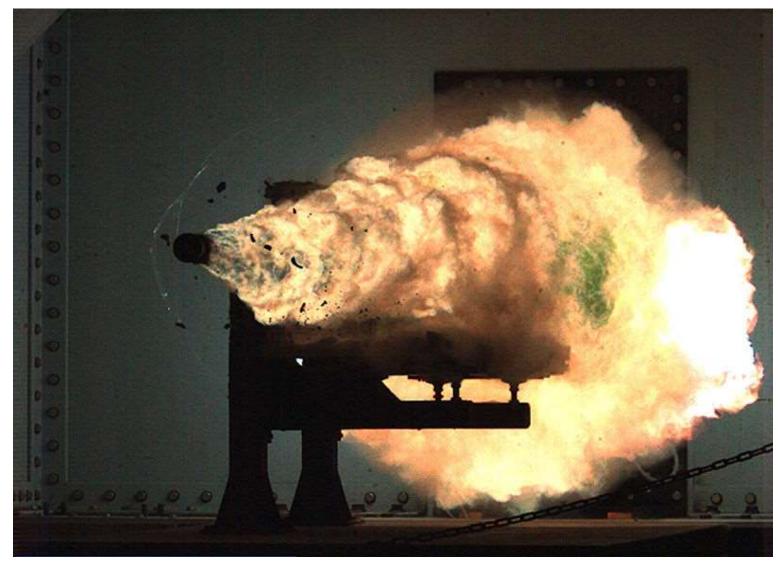

### Why HIL?

#### Why HIL?

By Marshelec - Own work, CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=16585159

### Why HIL?

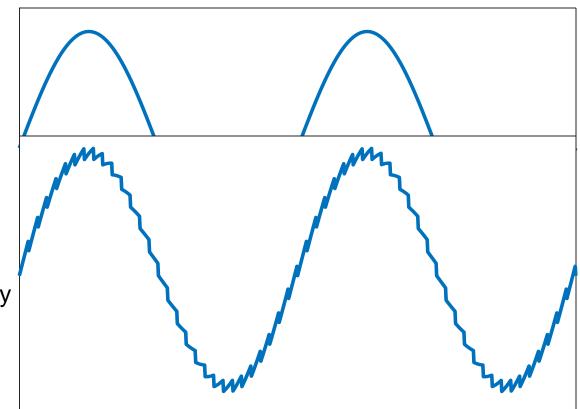

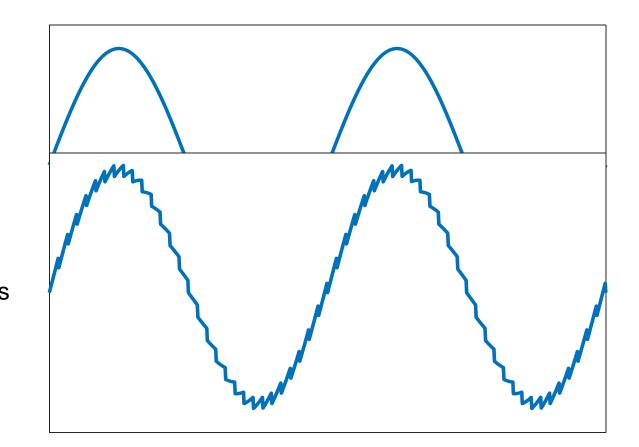

#### **Power Electronics and Motor Control - Switching**

2 ways to simulate power electronics

- Average

- Easy to implement in real time

- Ignores dynamics of switching devices

- Good enough for some types of analysis

- Switching

- Captures switching events

- Model faults and analyze switching efficiency

- Requires simulation 100 times faster than switching frequency

- Motor at 10 kHz requires 1 MHz simulation

MathWorks **speedgoat**

#### **CPU vs FPGA Simulations**

2 ways to simulate power electronics

- CPU

- Cheaper hardware

- Can run continuous domain simulation

- **FPGA** any code gen compatible block

- Woltiplierotoeksløfsimagattode faster

- Bequires discretis do maions interlation

# Review of a System Level Model of a Motor and Inverter in Simulink

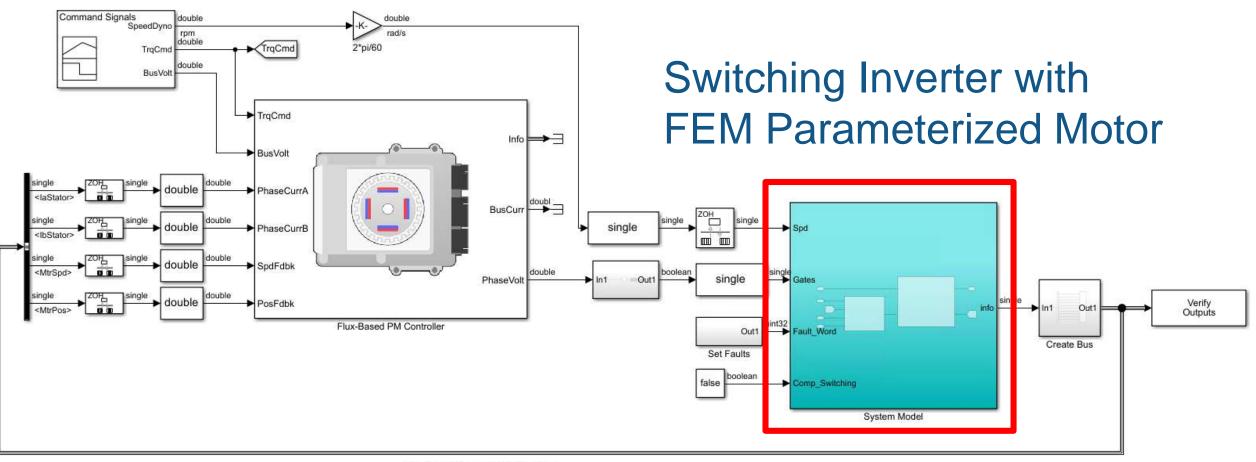

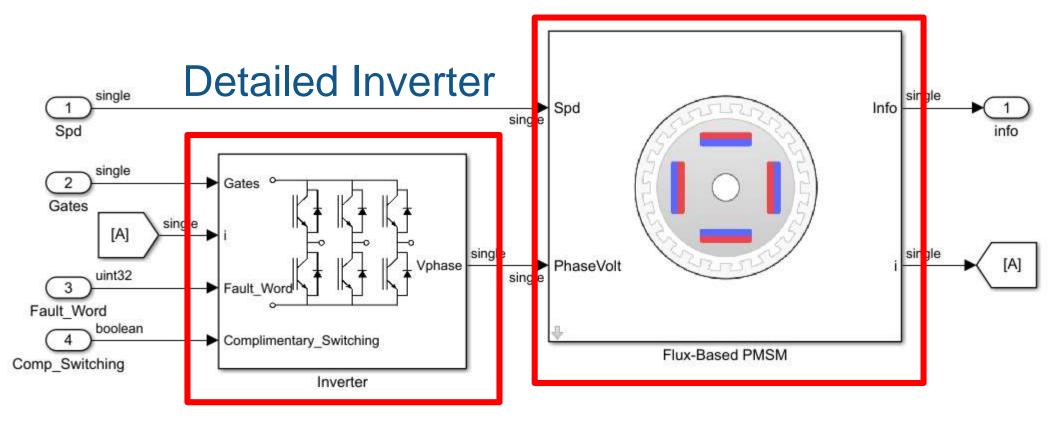

## Review of a System Level Model of a Motor and Inverter in Simulink FEM Based

## **Motor Model**

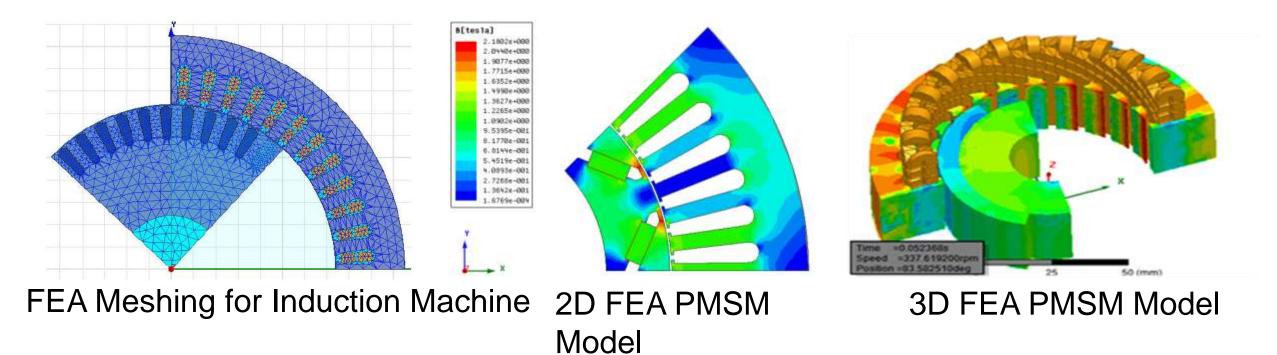

#### **Can Extract Lookup Table from FEM Tool**

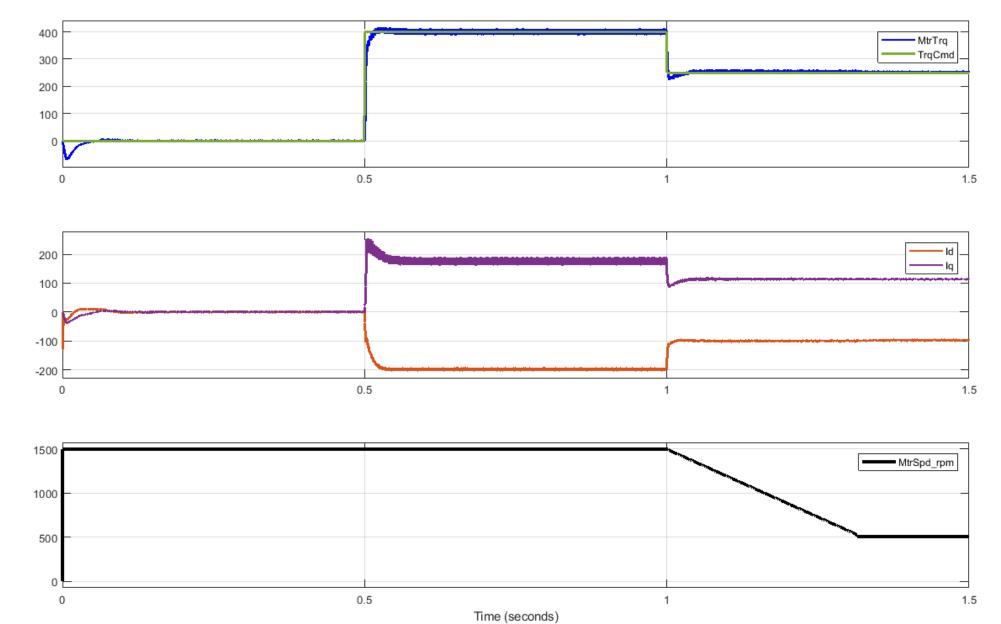

#### **Simulation Results**

14

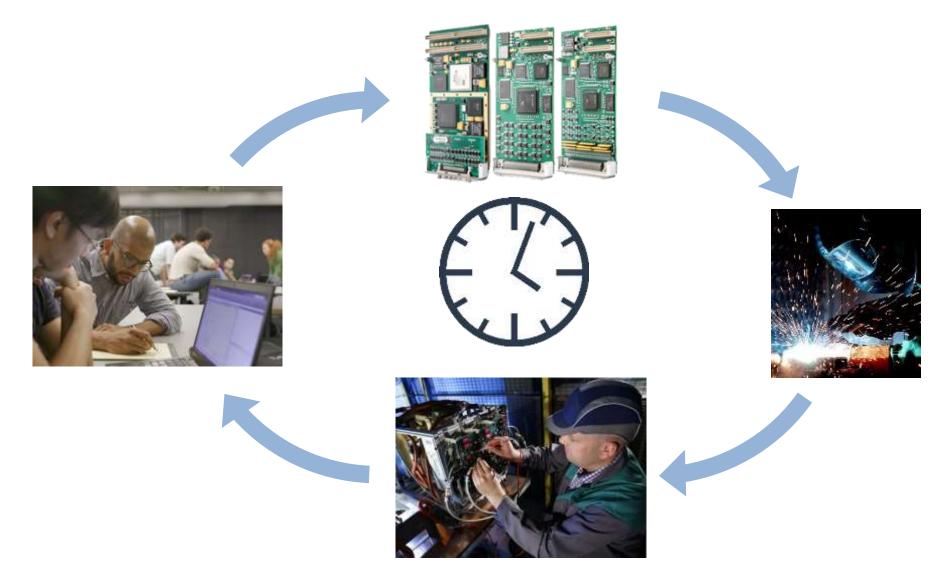

#### **High Level Process for Deploying Model to FPGA**

- 1. Create high level subsystem for defining I/O

- 2. Convert model to discrete time

- 3. Convert to single precision

- 4. Use HDL workflow advisor to setup model settings

- 5. Deploy model to the Speedgoat real-time machine

# HIL Simulation Using Simulink Real-Time and Speedgoat Target Hardware

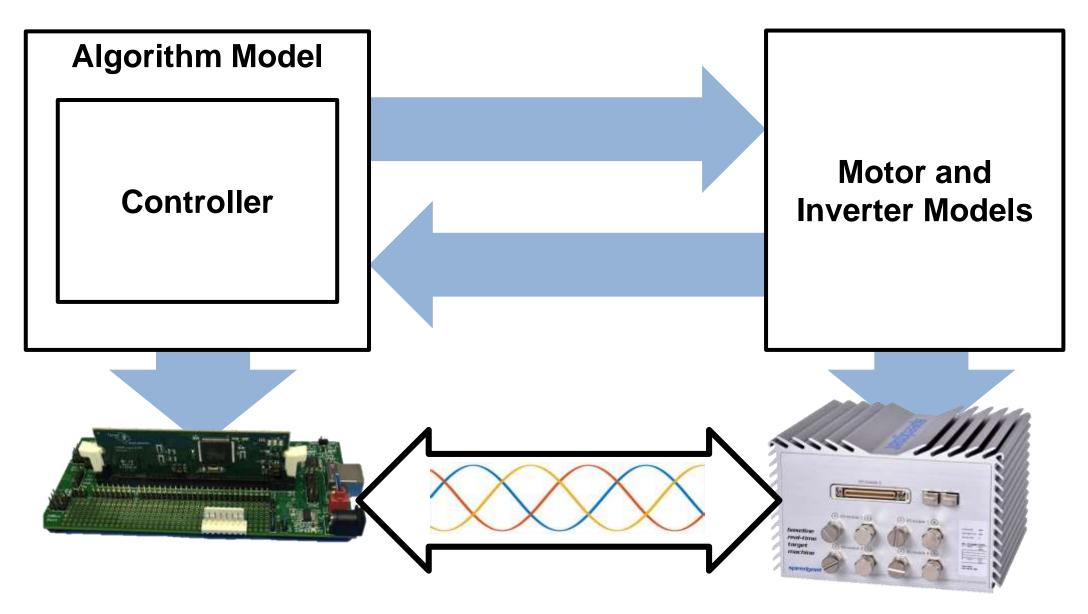

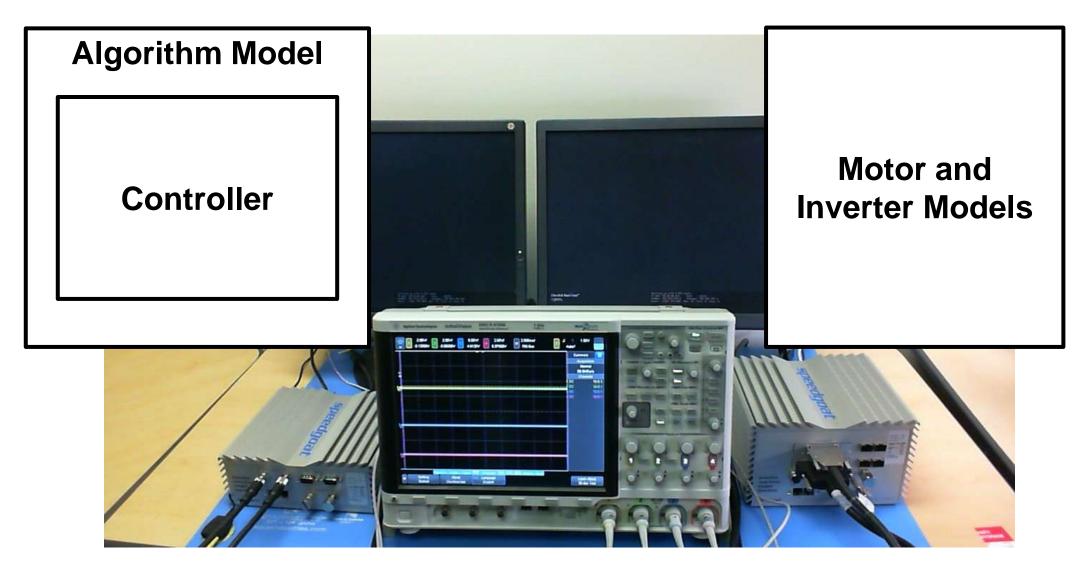

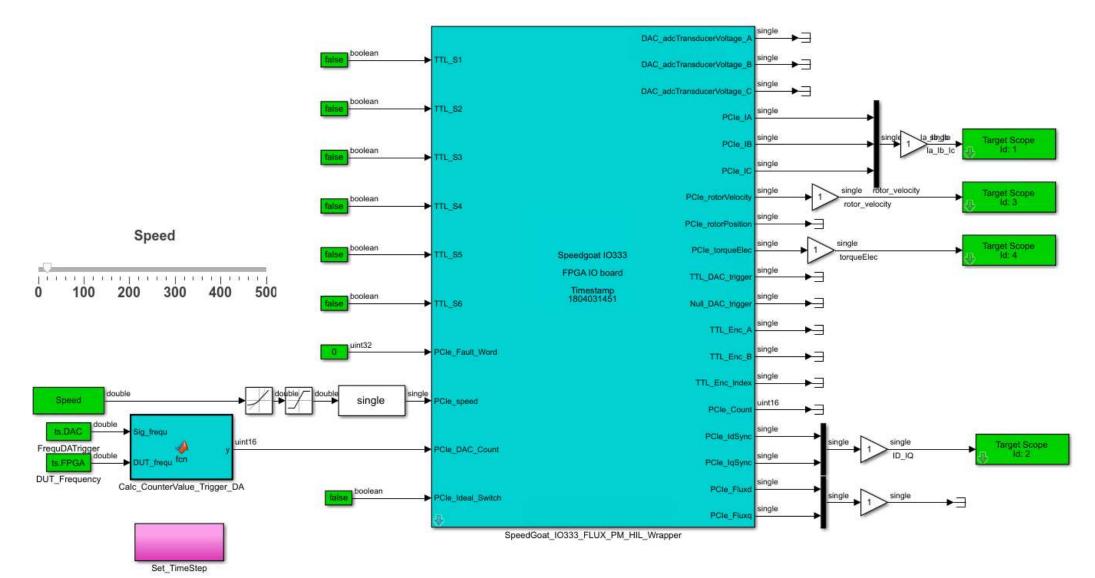

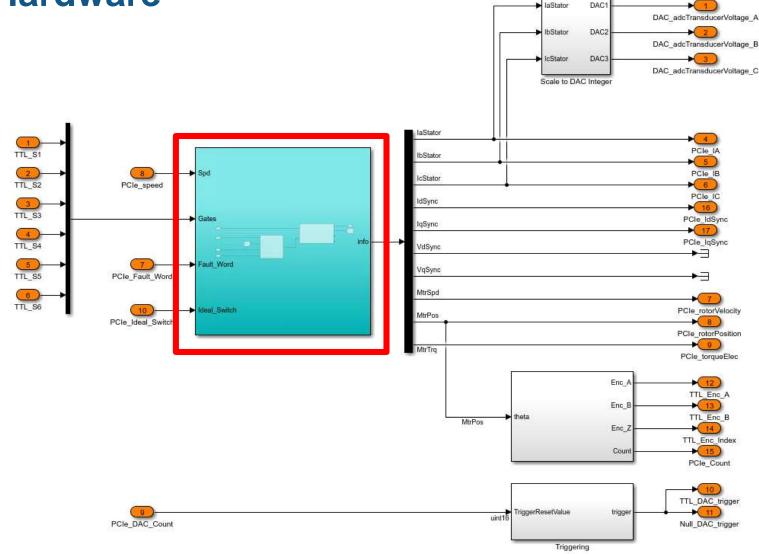

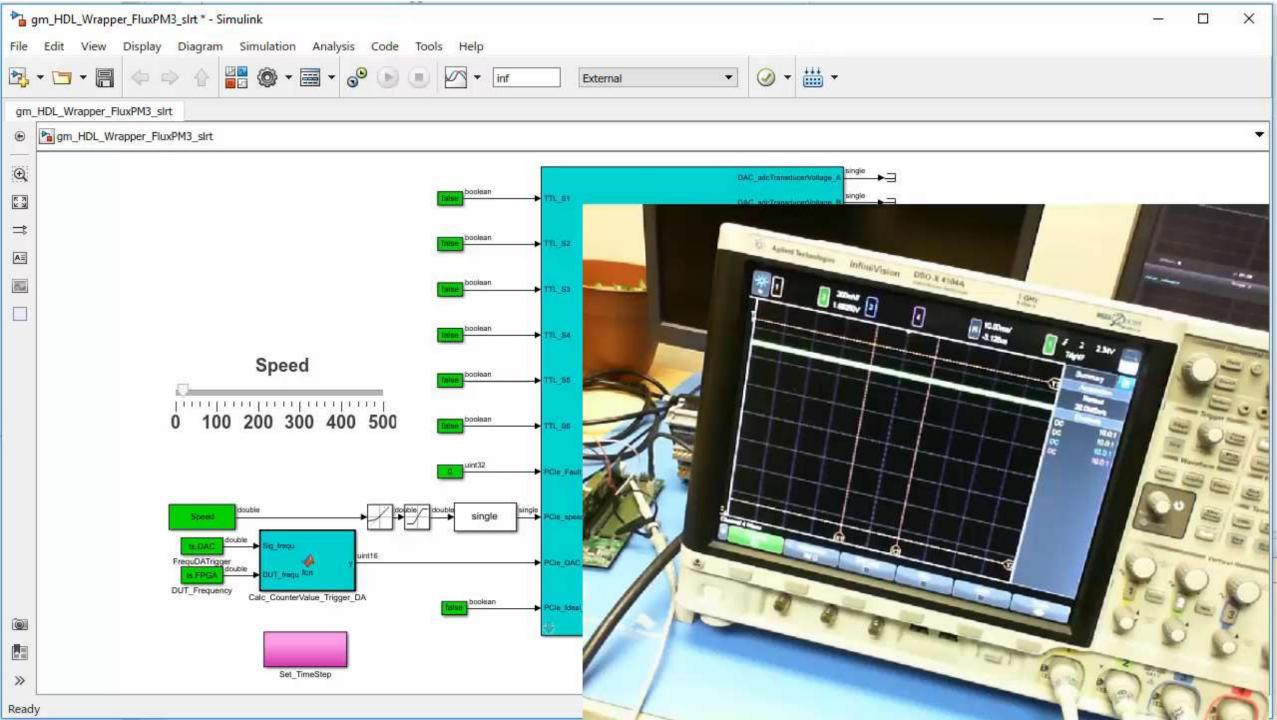

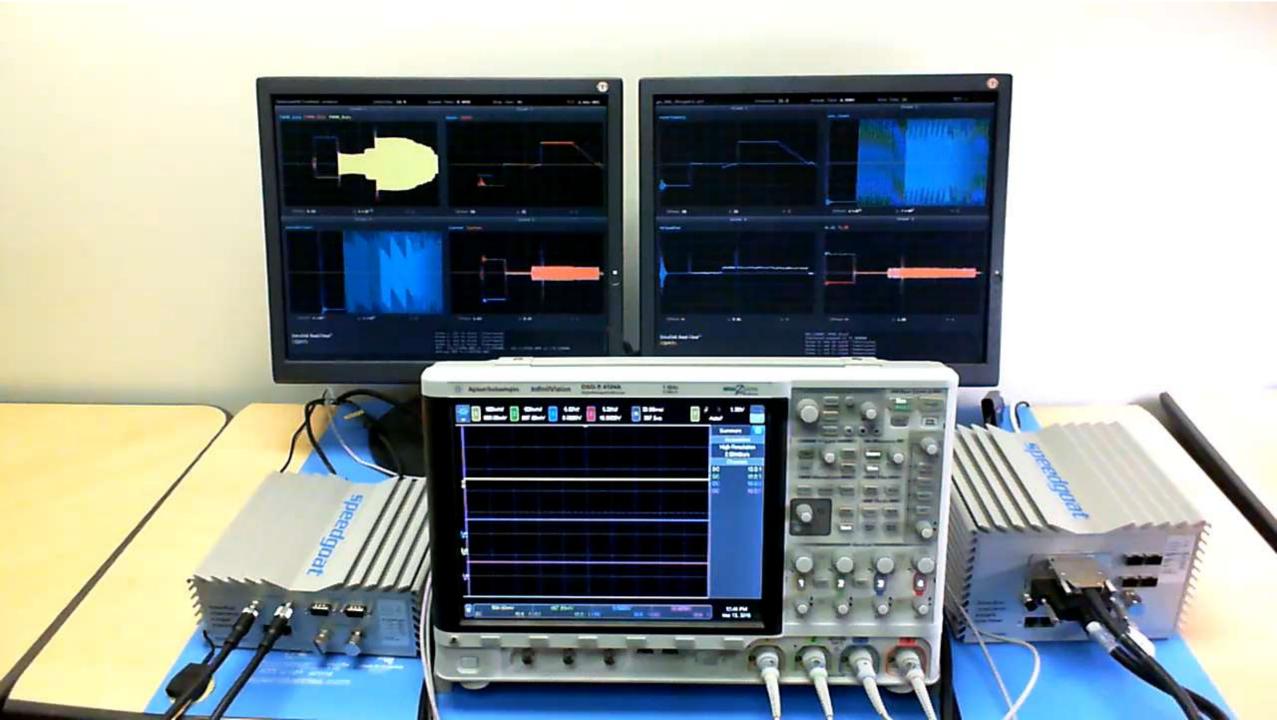

#### HIL Simulation Using Simulink Real-Time and Speedgoat Target Hardware

#### Use of HDL Coder to Generate Floating-Point HDL From the Simulink Model to Achieve 1 MHz Time-Steps

Example walkthrough available through webinar: <u>https://www.mathworks.com/videos/hardware-in-the-loop-hil-testing-for-</u> power-electronics-systems-modeled-in-simulink-1522417541924.html

| <ul> <li>HDL Workflow Advisor</li> <li>1. Set Target</li> <li>^1.1. Set Target Device and Synthesis Tool</li> <li>^1.2. Set Target Reference Design</li> <li>^1.3. Set Target Interface</li> <li>1.4. Set Target Frequency</li> </ul> | 5.1. Generate Simulink Real-Time interface Analysis Generate Simulink Real-Time interface Run This Task                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>2. Prepare Model For HDL Code Generation</li> <li>2.1. Check Global Settings</li> <li>^2.2. Check Algebraic Loops</li> <li>^2.3. Check Block Compatibility</li> <li>^2.4. Check Sample Times</li> </ul>                      | Result:       Passed         Passed Generate Simulink Real-Time Interface.         Generating new Simulink Real-Time Interface model:       gm_SpeedGoat_attempt_slrt         Simulink Real-Time Interface model generation complete. |

| <ul> <li>3. HDL Code Generation</li> <li>3.1. Set Code Generation Options</li> <li>3.2. Generate RTL Code and IP Core</li> </ul>                                                                                                      |                                                                                                                                                                                                                                       |

| <ul> <li>4. Embedded System Integration</li> <li>4.1. Create Project</li> <li>4.2. Build FPGA Bitstream</li> <li>5. Download to Target</li> <li>5.1. Generate Simulink Real-Time interface</li> </ul>                                 |                                                                                                                                                                                                                                       |

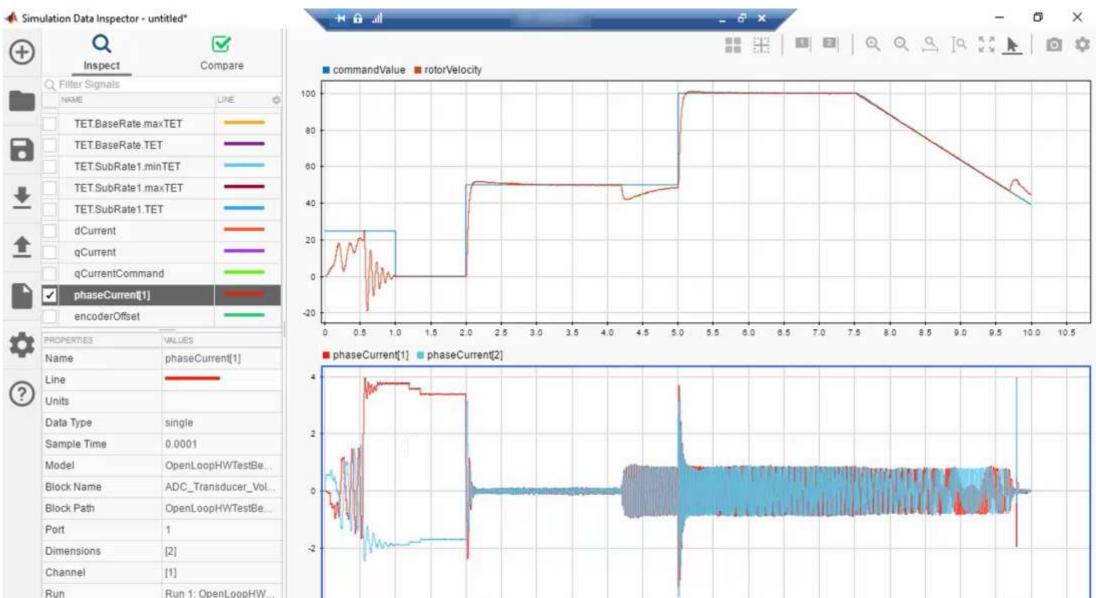

#### **SDI**

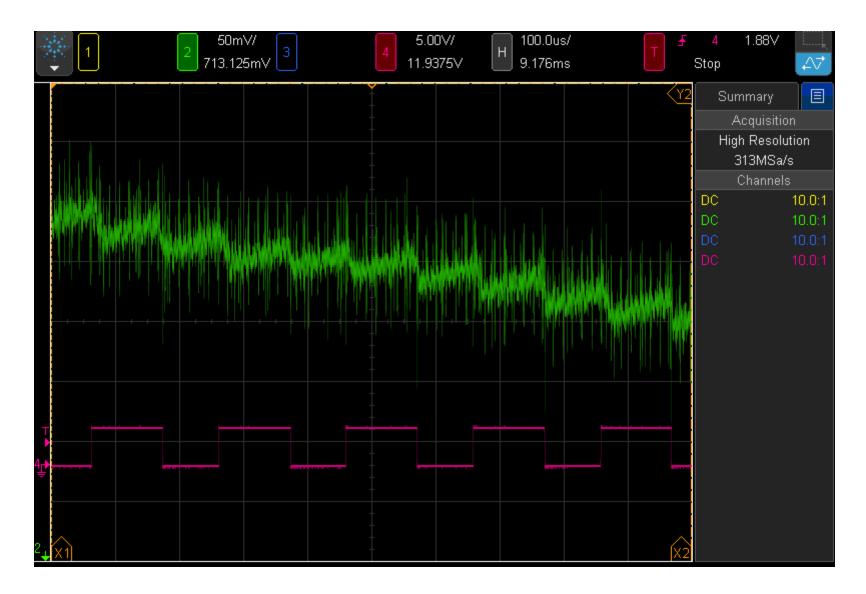

#### **Current Waveforms**

#### **High Level Process for Deploying Model to FPGA**

- 1. Create high level subsystem for defining I/O

- 2. Convert model to discrete time

- 3. Convert to single precision

- 4. Use HDL workflow advisor to setup model settings

- 5. Deploy model to the Speedgoat real-time machine

#### Conclusion

- 1. Integrate desktop simulation with HIL simulation

- 2. Native Floating Point support for FPGA

- 3. Workflow advisor creates a seamless transition from desktop simulation to FPGA implementation

For more Information:

Joel Van Sickel Joel.Vansickel@MathWorks.com 248-596-7939

## Want to know more? Visit us at the booth.

For more Information:

Joel Van Sickel Joel.Vansickel@MathWorks.com 248-596-7939

#### Simulink Programmable FPGA I/O modules Optimized for Power Electronics HIL and RCP

The IO334 I/O module is optimized for HIL simulation of real power stages. The card combines fast, low-latency analog and digital I/O capabilities, and is optimized for use with HDL Coder Workflow Advisor from MathWorks.

Analog connectivity: 16 x 5 MHz ADC, +/-10V, ENOB > 13-bit at 5 MHz 16 x 2 MHz DAC, +/-10V, settling time <1us

Multi-Gigabit Transceivers: 4 x MGT for inter-board communication Enables scalability - I/O and computational resources

Selectable rear plug-ins add: Digital TTL/RS422 I/O support for PWM / Encoder Front SFP cages to access MGT at the out side of the enclosure