验证手写和生成的HDL代码的组合

本例使用HDL联合仿真和fpga在环(FIL)仿真来验证由生成的和遗留的HDL代码组成的HDL设计。术语“遗留”在这里是用来表示那些可能是手写的、从第三方购买的或为另一个项目生成的并保存在本设计中以供重用的代码。

本例中的遗留代码实现了有限状态机(FSM),它是用于无线通信系统的多输入多输出(MIMO)解码器的子模块。大多数MIMO解码器都是在Simulink中开发的,其HDL代码将由HDL编码器生成。金宝appFSM属于那个Simulink设计。金宝appFSM的遗留代码将与Simulink模型集成,并通过代码生成过程集成到FPGA实现中。金宝app

该示例将展示设计师或验证工程师如何使用HDL Verifier协同仿真向导将遗留的FSM与Simulink模型集成并验证它。金宝appHDL协同仿真提供了完整的可见性和控制,使代码能够调试和验证。

在成功集成传统FSM之后,当从Simulink模型生成HDL代码时,Cyimulation块会自动包含传统代码,从而产生了MIMO解码器的完整FPGA实现。金宝app最后,使用FPGA-In--in-in-in循环在实际FPGA上验证整个设计。

示例概要

使用联合仿真向导将遗留的HDL代码导入Simulink模型金宝app

通过对遗留HDL代码进行共同模拟并将结果与行为模型进行比较来验证它

使用BlackBox中的Cosimulation块生成整个MIMO解码器的HDL代码

用fpga在环验证MIMO解码器

需求和先决条件

对于联合仿真和fpga在环,您将需要以下软件和硬件:

支持的HDL模拟器之一金宝app。有关支持金宝app的模拟器,请参阅Cosimulation需求.

FPGA设计软件

支持的FPGA开发板之金宝app一。有关支持金宝app的硬件,请参见金宝app支持的FPGA设备用于FPGA验证.

有关使用以太网的连接:主计算机上安装了千兆以太网适配器,千兆以太网交叉电缆

有关使用JTAG的连接:USB Blaster I或II电缆和用于英特尔FPGA板的驱动器。DigIlent®JTAG电缆和Xilinx FPGA板的驱动器。

MATLAB®和FPGA设计软件可以在您的计算机上或网络可访问设备上本地安装。如果您使用从网络中使用软件,您需要在计算机中安装第二个网络适配器,为FPGA开发板提供专用网络。请参阅计算机的硬件和网络指南,以了解如何安装网络适配器。

注意:该示例包括代码生成。如果您不能访问HDL Coder软件,您可以跳过本例中的代码生成步骤,并使用为您提供的HDL文件和FIL向导一起使用fpga在环中模拟它们。

为有限状态机创建参考模型

参考模型是实现所期望的行为的模拟模型。它通常在HDL验证中使用,方法是将它与RTL实现一起实例化,为两者提供相同的输入并比较它们的输出。在验证中引用模型的优点是,它们可以独立于实现(通常由不同的人)进行开发,提供对预期行为的独立验证,它们比实际实现更容易创建(不需要合成或实际设备定时),并且在模拟中通常运行得很快。

在本例中,验证遗留HDL代码的第一步是为设计的那一部分创建一个参考模型。FSM已经这样做了。打开behavioral_mimo。基金模式。双击进入MIMO Decoder子系统,您将看到FSM子系统包含实现FSM行为的MATLAB函数块。该参考模型将用于验证FSM的遗留HDL代码。

1.使用协同仿真向导导入遗留HDL代码

通过在MATLAB命令提示符中输入以下命令调用协同仿真向导:

CosimWizard.

从下拉列表中选择与Simulink的HDL联合仿真和您首选金宝app的HDL模拟器。如果HDL模拟器不在您的系统路径上,请提供路径并单击Next。

添加FSMSubsystem。FSMSubsystem_pkg vhd。vhd, Embedded_Controller。vhd文件(位于"verify_legacy_hdlsrc"文件夹)使用cosimWizard的Add按钮,并重新排序列表来放置fsm子系统。“FSMSubsystem_pkg. vhd”。VHD在列表的顶端,为正确的编译顺序。然后单击Next。

在以下2个面板上单击Next接受默认值并到达输入/输出端口面板。在“输入端口”列表中,从下拉列表中选择前3个端口的“端口类型”值:

CLK:端口类型=时钟复位:端口类型= RESET CLK_ENABLE:端口类型=重置

该端口类型的这种识别使得CISimulation块强制在HDL模拟器中强制这些信号,而不是要求它们在Simulink图中被驱动。金宝app在此示例中,我们将CLK_ENABLE端口视为其他重置以进行化妆。在继续下一步之前,同样选择CE_OUT选择“未使用”,导致它从CYSimulation块中省略,因为它在Simulink中不需要。金宝app

协同仿真向导自动识别HDL代码中的输入和输出,并根据它在那里找到的端口为Simulink创建协同仿真块。金宝app有一些输出端口的细节是它无法从HDL代码中了解的。在HDL代码中,输出只是位的集合,没有任何迹象表明您想在Simulink中如何解释这些位。金宝app您必须告诉协同模拟向导,您希望这些位被看作是有符号的值还是无符号的值,如果它们被解释为定点数字,那么小数点应该放在哪里。

在“输出端口详细信息”面板中,优化每个输出的数据类型。在这种设计的情况下,输出端口将被解释为如下。请注意,矢量端口的HDL代码中有多个标量端口(OUT_1,OUT_6,OUT_9,OUT_10,OUT_11,OUT_12):

out_1:签订,部分长度= 0(4标量港口)out_2:无符号,分数长度= 0 out_3:无符号,分数长度= 0 out_4:无符号,分数长度= 0 out_5:签订,部分长度= 10 out_6:签订,部分长度= 10(3标量港口)out_7:签订,部分长度= 2 out_8:无符号,分数= 0 out_9长度:签订,部分长度= 0(4标量港口)out_10:签订,部分长度= 0(4标量港口)out_11:签订,部分长度= 10(4标量港口)out_12:签订,部分长度= 10(4标量港口)out_13:无符号,分数长度= 0 out_14:签订,部分长度= 0

在时钟/复位详细信息面板中设置以下值:

clk Period = 10ns, Active Edge = Rising reset初始值= 1,Duration = 27 ns clk_enable初始值= 0,Duration = 37 ns

单击“下一步”以进入“开始时对齐面板”,并将“HDL时间设置为启动Cosimulation(NS)”到40。

继续到最后一步,取消“在模拟开始时自动确定时间刻度”的复选框。对于这个例子,我们知道联合仿真的时间尺度在Simulink中应该是1秒,对应于HDL模拟器中的10纳秒。金宝app有关在其他设计中使用自动时间刻度设置功能的信息,请参阅HDL验证器文档。设置上述时间刻度并单击Finish。

为了将遗留的HDL代码导入到Simulink模型中,将生成协同仿真块。金宝app您可以将新生成的协同仿真块和2个方便的命令块拖放到Simulink模型中,在fsm子系统块中,并将其连接到fsm子系统的输出端口。金宝app本例提供了一个在MIMO解码器子系统中带有比较器和断言块的协同仿真模型。添加了比较器和断言块,以提醒您嵌入式控制器参考模型的输出和遗留HDL实现之间的任何不匹配。

使用以下命令调整生成的cosimulation块的大小以使其更轻松地将其插入Cosimulation Model:

set_param (“untitled / fsmsubsystem”,“位置”, [0 0 16552]);

打开cosim_mimo.slx模型。将CosimWizard创建的新块和便利命令块拖到Cosimulation模型中,替换MimoDecoder子系统内的占位符子系统。

2.模拟验证遗留HDL代码

在您的协同仿真模型中,双击“Launch HDL Simulator”块来启动您所选择的HDL模拟器。在Simulink中单击Play按钮,启动协同仿真金宝app,观察MATLAB窗口中会显示警告消息。这些是由于参考FSM模型和HDL实现之间的差异而导致的输出信号的不匹配。

现在您可以使用Simulink和金宝appHDL模拟器调试特性来隔离问题并修复bug。在这种情况下,会出现错误,因为在HDL实现中错过了状态转换弧。注意,在HDL模拟器的波形显示中,FSM状态在仿真中很早就被卡住了。

修复手写HDL代码并重新运行协同仿真

已经为这个示例提供了更正的HDL代码。使用以下命令将新代码复制到你的工作目录,覆盖坏版本的Embedded_Controller.vhd:

COPYFILE(FullFile(“verify_legacy_hdlsrc”,“fixed_hdl”,“Embedded_Controller.vhd”),“verify_legacy_hdlsrc”,'F');

通过双击“Compile HDL Design”块重新编译遗留HDL代码。如果在上次执行联合仿真之后HDL模拟器仍然打开,则退出HDL模拟器,并重新启动HDL模拟器,然后重播联合仿真。这次你不应该看到错配。

现在,您已经调试和验证了嵌入式控制器的遗留HDL代码,您可以继续使用fpga在环验证整个MIMODecoder。

设置FPGA设计软件环境

在使用FPGA在环之前,请确保您的系统环境已正确设置,以便访问FPGA设计软件。你可以使用这个函数hdlsetuptoolpath将FPGA设计软件添加到当前MATLAB会话的系统路径中。

为HDL代码生成准备模型

为了准备FPGA在环模型,合并了遗留的HDL代码,并为MIMO解码器的其余部分生成新的HDL代码,您需要做两件事来完成FPGA实现:

编辑Cosimulation模型以删除FSM参考设计

使用HDL Coder Blackbox将遗留HDL合并到模型中以进行代码生成

如果您想按照使用HDL Blackbox为HDL代码生成准备模型的所有步骤,请使用不同的名称保存协同仿真模型,并按如下步骤继续模型准备的其余部分:

1.编辑Cosimulation模型以删除FSM参考设计

在MIMO Decoder子系统中删除Embedded_Controller函数块

删除驱动嵌入式_Controller输入的“来自”块,除了EnableCoder输入之外

删除输出上的比较器和断言块

将协同仿真块输出重新连接到DelaySubsystem1的输入

2.使用HDL Coder Blackbox将遗留HDL合并到模型中以进行代码生成

选择联合仿真块和类型control-G来创建一个子系统

右键单击新的Cyimulation子系统,然后选择HDL代码和HDL块属性

选择架构= BlackBox

在EntityName参数中输入fsmsubsystem

在ImplementationLatency参数中输入0

确定HDL块属性对话框

3.重新运行模拟以更新图表。

双击“启动HDL模拟器”块以启动HDL模拟器

在Simulink中点击Play按钮来启动协同模拟金宝app

保存模型

3.生成HDL代码和fpga在环

这一步需要HDL编码器。如果您没有这个软件,您可以使用预生成的HDL文件进行FIL模拟。直接跳到步骤5。使用filWizard进行模拟。

如果您想按照生成HDL文件的过程返回到模型的顶层,右键单击MIMODecoder子系统并在“HDL Code”下启动HDL Coder Workflow Advisor。

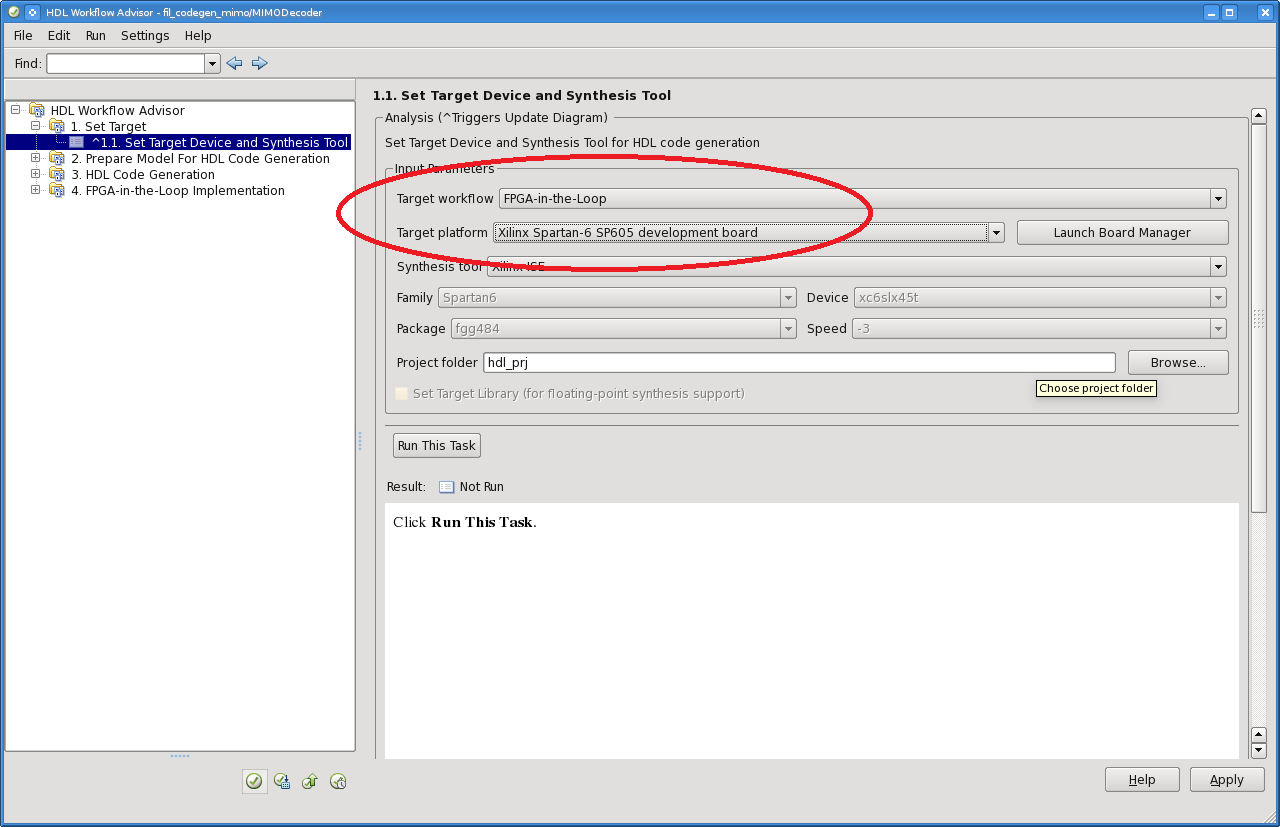

步骤1.1:选择FPGA-in- loop Target Workflow,从下拉列表中选择首选的FPGA开发板,并标识一个可写目录来保存生成的HDL代码。

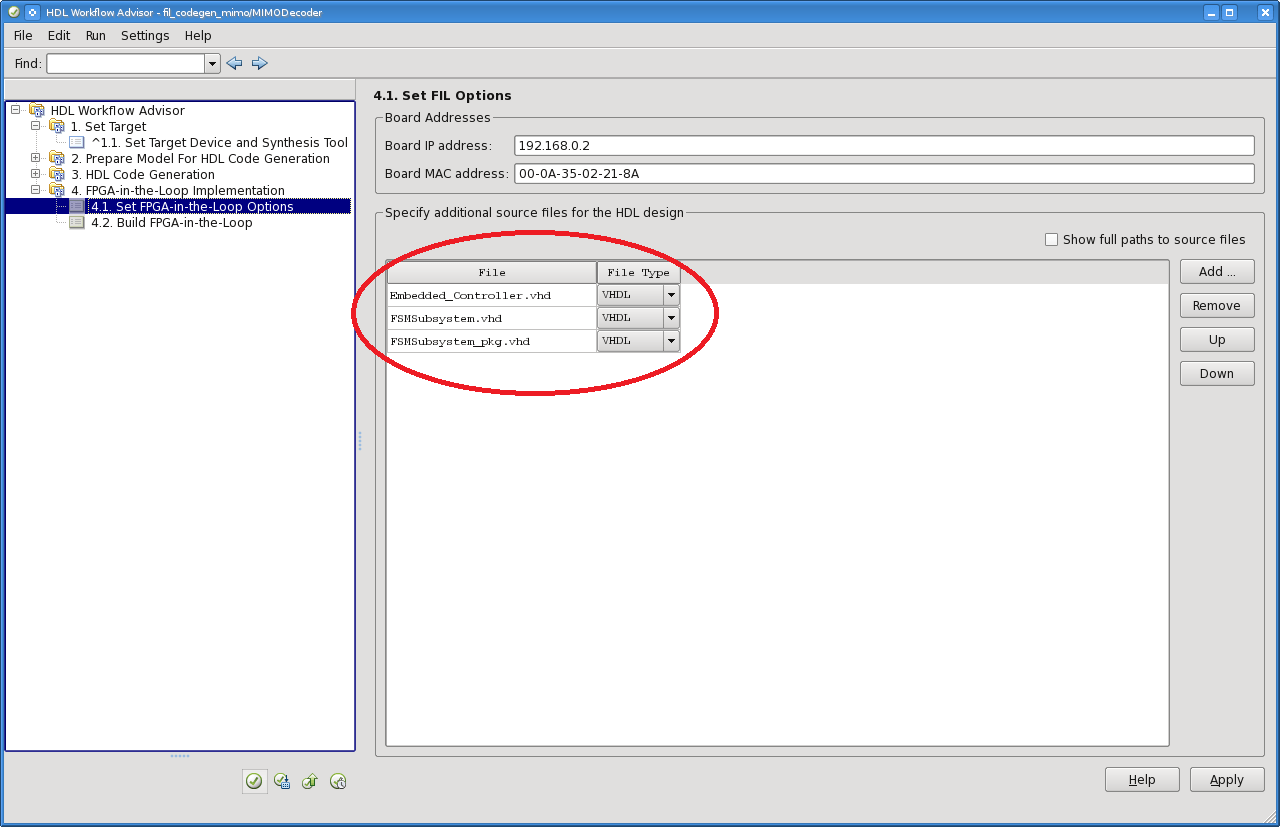

步骤4.1:在设置FPGA选项中选择“添加”,并使用浏览器导航到EmbeddedController HDL文件,您在步骤1中复制到您的工作文件夹,并在步骤3中使用固定的HDL代码进行修改。

步骤4.2:在左侧导航树中右键单击工作流的步骤4.2,选择“Run to this task”。这个步骤可能需要几分钟,因为它包括合成、映射和为FPGA设备设计路由的步骤。

结果将是用于MIMO解码器子系统的FPGA-in-in-Loop仿真的FPGA编程文件,以及包含原始模型(包括FSM的遗留HDL的FSM的传统HDL)的新模型以及与FPGA-IN一起 -循环块。它还将具有具有断言块的比较器,以识别与我们在Cosimulation模型中看到的信号类似的错配信号。

4.用fpga在环仿真验证设计

由于生成的验证模型包含了FSMSubsystem的联合仿真,您将需要使用HDL模拟器来运行整个FIL模型。请确保从您以前的联合模拟中关闭HDL模拟器并重新启动HDL模拟器。

在步骤3生成的fpga在环模型中,打开FIL块。

选择“Load”将FPGA编程文件下载到您的板上的设备上。

在Simulink模型中单击Play金宝app运行fpga在环仿真。

观察比较范围内的结果和模型中的错误率计算。你的FIL模拟结果应该与参考模型完全匹配。

5.使用FIL向导进行仿真

对于那些没有HDL Coder软件的人来说,这个步骤是步骤4的替代方法。如果你已经完成了第4步,你就不需要继续这个步骤了。

预生成的HDL文件位于“verify_legacy_gen_hdlsrc”文件夹中。您可以使用FIL向导创建用于在环FPGA的FPGA编程文件。FIL向导还将创建一个可以丢弃的FIL块,因为为本示例提供的FIL模型已经包含了这个FIL块。

输入以下命令打开FIL向导:

filwizard.

在费尔选项从列表中选择您的FPGA开发板。

在源文件选择添加并选择文件夹Verify_LEGACY_GEN_HDLSRC中的所有文件并识别MIMODecoder.vhd作为顶级文件。

接受FilWizard选项剩余选项的默认值

等待fild块和FPGA编程文件被创建。由于合成和路由FPGA实现所需的时间,这可能需要几分钟。

打开gm_fil_codegen_mimo_fil。slx模型,并将新生成的FIL块拖动到模型中指定的位置。

打开FIL块掩码,单击Signal Attributes选项卡。将每个rx_decoded输出的数据类型更改为fixdt(1,6,0),以匹配行为块的数据类型。

打开FIL块掩码,单击主选项卡,选择“加载”并等待将FPGA编程文件下载到设备。

在Simulink模型中按Play来金宝app运行fpga在环。

观察比较范围内的结果和模型中的错误率计算。你的FIL模拟结果应该与参考模型完全匹配。

最后给出了利用HDL协同仿真和fpga在环验证HDL设计的实例。