用fpga在环验证数字上变频器

这个例子向您展示了如何使用fpga在环仿真验证Filter design HDL Coder™生成的数字上变频器设计。

需求

本示例所需的工具:

FPGA设计软件

支持的FPGA开发板和金宝app附件之一(本示例不支持ML403板)。有关受支持的硬件的详细信息,请参见金宝app金宝app支持的FPGA设备用于FPGA验证.

使用以太网连接:主机上安装的千兆以太网适配器、千兆以太网交叉网线

使用JTAG连接:JTAG电缆与USB Blaster I或II, USB Blaster驱动程序

PCI Express®连接:安装在上位机PCI Express槽位的FPGA板。

创建DUC的Cascade Filter

数字上变频器(DUC)是将数字基带信号转换为通带信号的数字电路。DUC由三个滤波阶段组成;每个阶段用低通插值滤波器对输入信号进行滤波,然后是采样率变化。在本例中,DUC是由两个FIR插值滤波器和一个CIC插值滤波器组成的级联,如示例HDL数字上变频器(DUC)所述。

1.创建两个FIR和CIC过滤器。

Pfir = [0.0007 0.0021 -0.0002 -0.0025 -0.0027 0.0013 0.0049 0.0032...-0.0034 -0.0074 -0.0031 0.0060 0.0099 0.0029 -0.0089 -0.0129...-0.0032 0.0124 0.0177 0.0040 -0.0182 -0.0255 -0.0047 0.0287...0.0390 0.0049 -0.0509 -0.0699 -0.0046 0.1349 0.2776 0.3378...0.2776 0.1349 -0.0046 -0.0699 -0.0509 0.0049 0.0390 0.0287...-0.0047 -0.0255 -0.0182 0.0040 0.0177 0.0124 -0.0032 -0.0129...-0.0089 0.0029 0.0099 0.0060 -0.0031 -0.0074 -0.0034 0.0032...0.0049 0.0013 -0.0027 -0.0025 -0.0002 0.0021 0.0007];

hpfir = dsp。FIRInterpolator (2 pfir);hpfir。FullPrecisionOverride = false;hpfir。CoefficientsDataType =“自定义”;hpfir。CustomCoefficientsDataType = numerictype ([], 16);hpfir。ProductDataType =“自定义”;hpfir。CustomProductDataType = numerictype(31)[], 31日;hpfir。AccumulatorDataType =“自定义”;hpfir。CustomAccumulatorDataType = numerictype(15)[], 16日;hpfir。OutputDataType =“自定义”;hpfir。CustomOutputDataType = numerictype(15)[], 16日;hpfir。RoundingMethod =“最近的”;

cir = [-0.0007 -0.0009 0.0039 0.0120 0.0063 -0.0267 -0.0592 -0.0237...0.1147 0.2895 0.3701 0.2895 0.1147 -0.0237 -0.0592 -0.0267...0.0063 0.0120 0.0039 -0.0009 -0.0007];

hcfir = dsp。cfir FIRInterpolator (2);hcfir。FullPrecisionOverride = false;hcfir。CoefficientsDataType =“自定义”;hcfir。CustomCoefficientsDataType = numerictype ([], 16);hcfir。ProductDataType =“自定义”;hcfir。CustomProductDataType = numerictype(31)[], 31日;hcfir。AccumulatorDataType =“自定义”;hcfir。CustomAccumulatorDataType = numerictype(15)[], 16日;hcfir。OutputDataType =“自定义”;hcfir。CustomOutputDataType = numerictype(15)[], 16日;hcfir。RoundingMethod =“最近的”;

hcic = dsp。CICInterpolator (32 1 5);hcic。FixedPointDataType =“最小节字长”;hcic。OutputWordLength = 20;

2.使用这些过滤器创建一个级联过滤器。

hduc = dsp。FilterCascade (hpfir hcfir hcic);

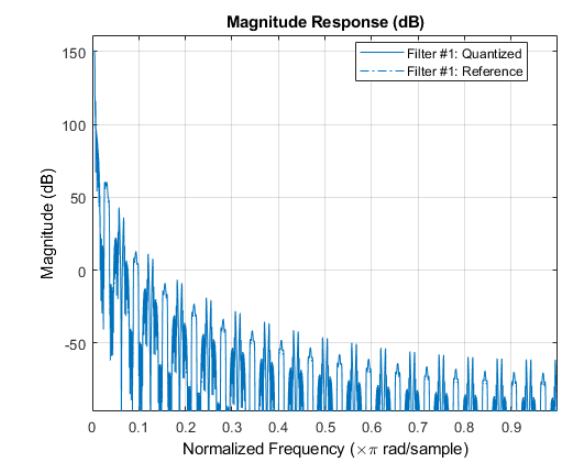

级联滤波器的频率响应如下图所示。

fvtool (hduc“算术”,“固定”);

生成HDL代码

当级联滤波器准备好后,使用filter Design HDL Coder函数为DUC生成HDL代码generatehdl,并将属性' addpipelinerregisters '设置为'on'。

generatehdl (hduc“名字”,“hdlduc”,“AddPipelineRegisters”,“上”,“InputDataType”15) numerictype(16日);

该选项在滤波器阶段之间插入管道寄存器,并允许生成的滤波器以更高的时钟频率合成。

如果您没有Filter Design HDL Coder,您可以使用当前目录中预生成的HDL文件。

建立FPGA设计软件

在使用FPGA in-the- loop之前,请确保您的系统环境已正确设置,以便访问FPGA设计软件。你可以使用这个函数hdlsetuptoolpath将FPGA设计软件添加到当前MATLAB会话的系统路径中。

配置和构建fpga在环

FIL向导指导您配置构建fpga在环中所必需的设置。使用以下命令启动向导:

filWizard

1.在“硬件选项”中,选择连接到主机的FPGA开发板。如果需要,也可以在“高级选项”中自定义“单板IP地址”和“MAC地址”。单击*Next”继续。

2.在源文件中,使用下列方法将为DUC生成的HDL文件添加到源文件表中浏览.

hdlduc.vhdhdlduc_stage1.vhd hdlduc_stage2.vhd hdlduc_stage3.vhd

选择旁边的顶级复选框hdlduc.vhd.单击*Next”继续。

3.在DUT I/O Ports中,输入和输出端口信息,如端口名称、方向、宽度和端口类型,是由HDL文件自动生成的。端口类型,如Clock和Data,是基于端口名生成的;您可以根据需要更改选择。对于本例,生成的端口类型是正确的,您可以单击下一个.

4.在“生成选项”中,指定用于FIL输出文件的文件夹。在这个示例中,您可以使用默认值。点击构建.点击构建导致FIL向导生成所有必要的文件用于fpga -in- loop模拟并执行以下操作:

在新的Simulink®模型中生成一个FIL块金宝app

打开命令行窗口编译FPGA项目,生成FPGA编程文件

FPGA项目编译耗时数分钟。当该过程完成时,会提示您关闭命令行窗口。现在关闭这个窗口。

配置费尔块

为了准备fpga在环模拟,按照下面的步骤配置FIL块。

1.打开开放模式按钮以打开测试台模型并将生成的FIL块复制到模型中。

2.双击FIL块以打开块掩码。点击负载使用生成的编程文件对FPGA进行编程。

3.在“运行时选项”下更改超频的因素到128年。这指定一个输入值在输入改变值之前被FPGA时钟采样128次。

4.在FIL块掩码上,单击Signal Attributes选项卡。将filter_out的数据类型更改为1) fixdt(20日匹配行为过滤块的数据类型。

5.点击好吧关闭块掩码。

验证生成过滤器

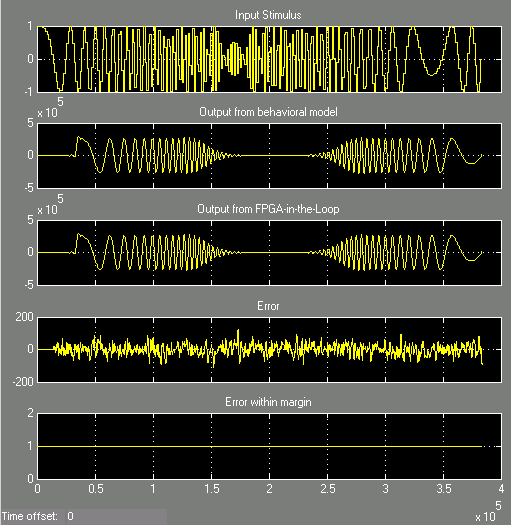

在本例中,将在FPGA上运行生成的滤波器与行为滤波器块进行比较。延迟被添加到行为过滤器的输出,以匹配生成过滤器的HDL延迟。

模拟运行。观察行为滤波器块、FIL块和误差范围的输出波形。因为行为过滤块没有管道寄存器,所以行为过滤块输出和FIL块输出之间有很小的差异。这些误差在误差范围内。

这个例子到此结束。