分析MCDC级联逻辑块

这个例子说明了仿真软件®覆盖™记录MCDC规为一连串的逻辑金宝app操作符。

示例模型

在仿真金宝app软件中,有不同的方法来实现布尔逻辑,比如通过使用一个如果声明一个MATLAB函数块,Stateflow图条件转换,或多个逻辑算子的组合块级联连接在一起。

模型的例子slvnvdemo_cv_logic_cascade实现相同的布尔表达式在MATLAB中通过使用MATLAB代码功能块以及一连串的逻辑算符块。

使用以下命令打开模型slvnvdemo_cv_logic_cascade:

open_system (“slvnvdemo_cv_logic_cascade”);

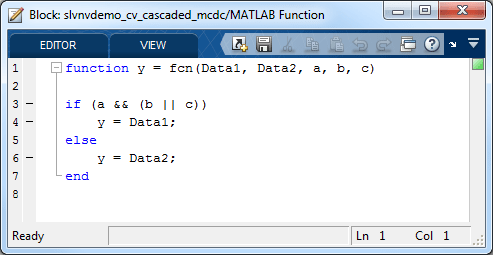

打开MATLAB功能块相关的函数。

open_system (“slvnvdemo_cv_logic_cascade / MATLAB函数”)

在MATLAB功能块,如果(& & (b | | c))是真的,那么这个信号Data1将输出;否则,信号Data2是输出。

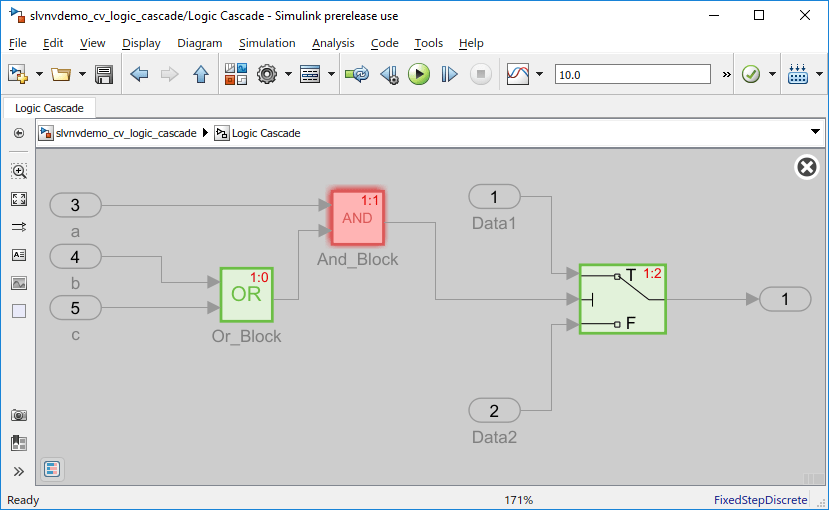

打开子系统的逻辑级联使用以下命令,注意,这个子系统实现相同逻辑使用逻辑操作符块和一个开关。

open_system (“slvnvdemo_cv_logic_cascade /逻辑级联”);

最后,打开信号编辑器和注意,有三个组合给出了布尔的输入一个,b,c。这些组合FFF,TFT,到达目标时间。

open_system (“slvnvdemo_cv_logic_cascade /信号编辑器”);

关闭信号编辑器。

close_system (“slvnvdemo_cv_logic_cascade /信号编辑器”,0);

比较MCDC覆盖率报告结果

模拟模型和生成覆盖报告。

testObj = cvt (“slvnvdemo_cv_logic_cascade”);testObj.settings.decision = 1;testObj.settings。条件= 1;testObj.settings。mcdc = 1;covdata = cvsim (testObj);%的模拟覆盖cvhtml (“exampleReport.html”,covdata);%生成覆盖率报告

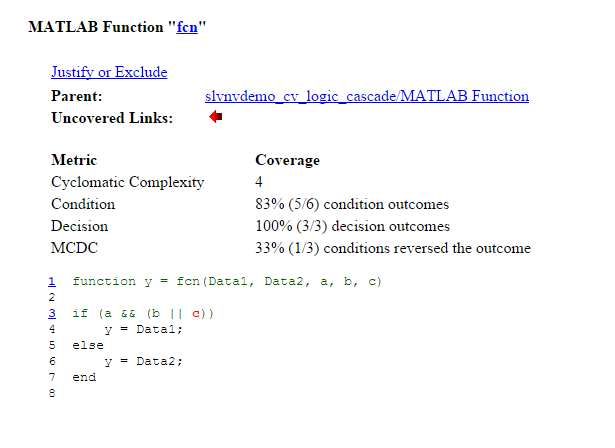

MCDC MATLAB功能块的结果

在生成的报告中,导航到MATLAB功能块的详细信息。

MCDC结果如果语句在MATLAB函数块预期,给指定的输入。

MCDC结果逻辑级联

下一个逻辑级联的检查结果。回想一下,这个组合块实现了MATLAB中的MATLAB代码相同的逻辑功能块;因此,我们期望MCDC结果会是一样的,。

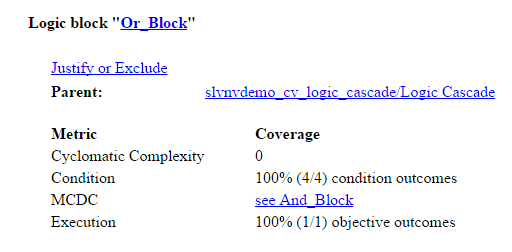

让我们先看看上游Or_Block。

注意,MCDC总结这一个链接的文本块“看到And_Block”,他指的是逻辑算符在级联的根源。点击此链接以报告显示结果的部分这一块。

逻辑算符块的根源(在这种情况下And_Block)报告MCDC结果整个级联。

MCDC分析级联的细节首先显示一个链接说明有多少块级联。点击这个链接”包括两个街区”将模型,突出了两个街区包括级联(Or_Block和And_Block)。

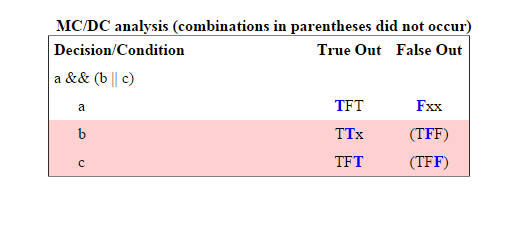

报告的这一部分然后显示了布尔表达式由级联,在这种情况下C1 & & (C2 | | C3),在那里C1,C2,C3是条件对应于三个输入级联。表为每个条件,说明了相关的块和它的输入(括号所示)以及MCDC结果。这些结果表明,输入组合TTx,Fxx,TFT都是锻炼,但TFF还没有。这匹配给定的期望产生的输入信号编辑器(到达目标时间,FFF,TFT)。

此外,正如所料,布尔表达式和MCDC结果显示这种级联匹配显示的是什么如果声明在MATLAB中实现相同逻辑功能块。

覆盖告密者和模型着色

使用以下命令显示覆盖率结果对模型:

cvmodelview (covdata);

就像覆盖报告所示,MCDC目标不记录单个逻辑算符块级联;相反,MCDC目标被记录为代表的布尔表达式的组合块级联,并报告结果的最后一块级联。模型的突出反映了这一点,。考虑到输入组合FFF,TFT,到达目标时间的三个输入一个,b,c,Or_Block收到完整的覆盖,因为所有的覆盖目标块的条件已经满足。然而,因为有MCDC目标与级联这没有被满足,And_block(最后一个块级联中)用红色突出显示。

上空盘旋And_block为更多的信息。

工具提示正确地报告说这个块不接受完全覆盖,因为一些MCDC目标级联并不满意。

命令行

你也可以检索MCDC结果的逻辑块级联从MATLAB命令行mcdcinfo。再次,MCDC目标级联将最后一块级联中被发现。

[coverage_casc, description_casc] = mcdcinfo (covdata,“级联slvnvdemo_cv_logic_cascade /逻辑/ And_Block”)description_casc.condition (1) description_casc.condition (2) description_casc.condition (3)

coverage_casc = 1 3 description_casc =结构体字段:文字:“C1 & & (C2 | | C3)的条件:[1 x3 struct] isFiltered: 0 filterRationale:“justifiedCoverage: 0 ans =结构体字段:文字:“C1 (And_Block In1)”实现:1 trueRslt:“TFT”falseRslt:的Fxx isFiltered: 0 isJustified: 0 filterRationale:“trueExecutedIn: [] falseExecutedIn: [] ans =结构体字段:文字:“C2 (Or_Block In1)”实现:0 trueRslt:“TTx”falseRslt:“(TFF)”isFiltered: 0 isJustified: 0 filterRationale:“trueExecutedIn: [] falseExecutedIn: [] ans =结构体字段:文字:“C3 (Or_Block In2)”实现:0 trueRslt:“TFT”falseRslt:“(TFF)”isFiltered: 0 isJustified: 0 filterRationale:“trueExecutedIn: [] falseExecutedIn: []

其他块级联的成员不会展览MCDC目标。

[coverage_or, description_or] = mcdcinfo (covdata,“级联slvnvdemo_cv_logic_cascade /逻辑/ Or_Block”)

coverage_or = [] description_or = []

短路MCDC的布尔表达式

在模型示例slvnvdemo_cv_logic_cascade,覆盖设置设置逻辑算符块被视为短路。

由于此设置,分析一连串的逻辑操作符块时,运营商在相应的布尔表达式被视为短路MCDC的目的。说明了上面所示的结果,这意味着MCDC识别短路发生内和跨块逻辑运算符。因此,MCDC结果的级联逻辑算符块匹配的如果语句在MATLAB函数块,后者总是视为短路。

短路在一块

请注意,在上面的示例中,真正的MCDC客观的结果C2是TTx,这表明当C1和C2都是真的,C3无关紧要的是由于内部短路吗Or_Block。

跨多个块短路

此外,考虑假MCDC客观的结果C1,Fxx。这一结果说明MCDC分析识别跨块短路。因为第一次输入And_Block是假的,第二个输入短路。随后,为了MCDC,这可以终止Or_Block(和它的输入)。MCDC短路行为的逻辑块级联基于优先级的操作发生在相应的布尔表达式(不管逻辑算子的执行顺序块在模拟)。

Non-short-circuiting布尔表达式

你也可以把布尔表达式由一连串的逻辑操作符块期间non-short-circuiting MCDC分析,提供使用掩蔽MCDC的定义。为此,设置参数CovLogicBlockShortCircuit来“关闭”并确保CovMcdcMode被设置为“屏蔽”。事实上,这些都是默认设置这些参数,当创建一个新的模型。

注意,如果CovLogicBlockShortCircuit是“关闭”和CovMcdcMode被设置为“UniqueCause”然后一连串的逻辑操作符块将被单独分析MCDC的目的,和布尔表达式由MCDC整个级联不会计算。

注意,当此示例中的级联不是作为短路,一些MCDC目标不再是满足给定的输入。

set_param (“slvnvdemo_cv_logic_cascade”,“CovLogicBlockShortCircuit”,“关闭”);set_param (“slvnvdemo_cv_logic_cascade”,“CovMcdcMode”,“屏蔽”);covdata_non_sc = cvsim (“slvnvdemo_cv_logic_cascade”);%模拟覆盖逻辑块短路了cvhtml (“exampleReport_non_sc.html”,covdata_non_sc);%生成覆盖率报告