使用FPGA数据捕获从英特尔FPGA板读取音频信号

此示例显示了如何使用现有的HDL代码使用FPGA数据捕获来读取FPGA内部信号。我们从现有的FPGA设计开始,将片上模数变为数字转换器(ADC)进行示例音频信号。ADC IP公开了用于控制的Avalon Memory映射(MM)从接口,以及用于数据输出的Avalon流界面。此FPGA设计已包含一个简单的Avalon MM主站以启动ADC。我们将使用FPGA数据捕获功能将ADC输出数据从Avalon Streaming接口收集到MATLAB工作区。

需求和先决条件

马铃薯

高密度脂蛋白验证器

英特尔FPGA板的HDL验金宝app证机支持包

固定点设计师

英特尔®Quartus Prime软件

arrow®deca max 10 fpga开发板

设置FPGA开发板

1.确保电源开关保持关闭状态。

2.将JTAG下载电缆连接到FPGA开发板和主机之间。

3.(可选)通过3.5 mm音频电缆将FPGA板的线路连接到FPGA电路板的线路端口。如果跳过此步骤,则捕获的数据将是随机噪声。

准备示例资源

设置工作文件夹,并提供MATLAB,可以访问您的FPGA设计软件。

1.在可以复制示例文件的MATLAB安装文件夹范围之外创建一个文件夹。文件夹必须可写。此示例假定该文件夹位于C:\ MyTests。

2.启动MATLAB并将MATLAB中的当前目录设置为刚才创建的文件夹。例如:

cd C: \ mytest

3.要将示例FPGA设计文件复制到工作目录中,请输入此MATLAB命令:

CopyAlterafpgaExamplefiles('ADC')

4.建立英特尔Quartus。在这里,我们假设Intel Quartus可执行文件位于C: altera\18.0\ Quartus \bin\ Quartus .exe中。如果可执行文件的位置不同,则使用路径。

hdlsetuptoolpath(“ToolName”、“阿尔特拉第四的二世”、“路径”,“C: \ \ 18.0 \负责第四的\ bin \ quartus.exe ');

生成FPGA数据捕获组件

在MATLAB命令提示符处,输入:

generateFPGADataCaptureIP

此命令启动FPGA数据捕获组件生成应用程序。此示例监视来自现有HDL设计的两个信号,用于音频系统。信号是12位“ADC_OUT”和8位“计数器”。“ADC_OUT”是音频线路信号的数字样本。下一个信号“计数器”是一个8位自由运行的计数器。要配置数据捕获组件以在这两个信号上运行,请进行以下更改:

1.单击“添加”按钮一次将一行添加到端口表。

2.将第一个信号命名为“adc_out”,将第二个信号命名为“counter”。

3.将两个信号的比特宽度分别更改为12和8。

4.确保FPGA供应商设置为Altera。

5.确保选择的语言是Verilog。

6.设置“采样深度”为1024。这是每次检测到触发器时,数据捕获工具返回到MATLAB的每个信号的样本数。

7.将MAX触发阶段设置为2.这是您在数据捕获期间可以添加的最大触发阶段数,以提供多个触发条件。

应用程序设置将如下图所示:

最后,单击“生成”按钮以生成FPGA数据捕获组件。报告显示了这一代的结果。

集成FPGA数据捕获HDL IP

您必须将生成的HDL IP核包含到示例FPGA设计中。您可以从生成的报告中复制模块实例代码。在本例中,我们将把生成的HDL IP与ADC输出和8位自由运行计数器连接起来。

打开此示例提供的Top.v文件。取消注释以下代码行。

数据捕获u0 (.clk(adc_clk), .clk_enable(adc_valid), .ready_to_capture(), .adc_out(adc_out), .counter(counter[7:0]));

保存Top.v,编译已修改的FPGA设计,并使用以下TCL脚本创建FPGA编程文件。

系统(“quartus_sh - t adc_deca_max10。tcl &”)

本例中包含的tcl脚本执行以下步骤:

1.创建一个新的Quartus项目。

2.将示例HDL文件和生成的FPGA数据捕获HDL文件添加到项目中。

3.编制设计。

4.编程FPGA。

等到Quartus过程之前在下一步之前成功完成。这个过程大约需要5到10分钟。

捕获数据

首先,进入生成FPGA数据捕获组件的目录。

CD HDLSRC.

启动FPGA数据捕获应用程序。这个应用程序是为您的数据捕获信号定制的。

launchdatacuptureapp.

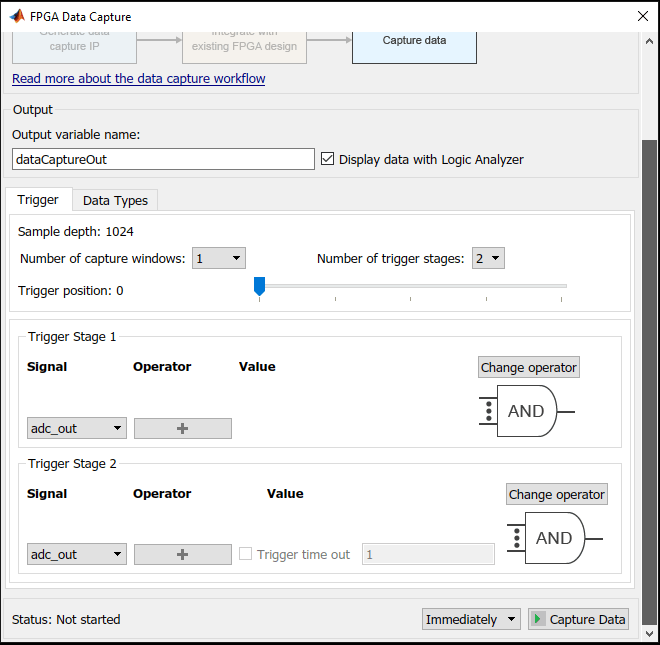

单击“捕获数据”按钮以启动数据捕获。这请求来自FPGA的一个缓冲区捕获的数据。默认值是立即捕获,无需等待触发条件。

捕获的数据被保存到MATLAB工作区中的一个结构体dataCaptureOut中。如果您有DSP系统工具箱,捕获的数据也显示为信号波形在逻辑分析仪。

使用触发器缩小数据捕获的范围

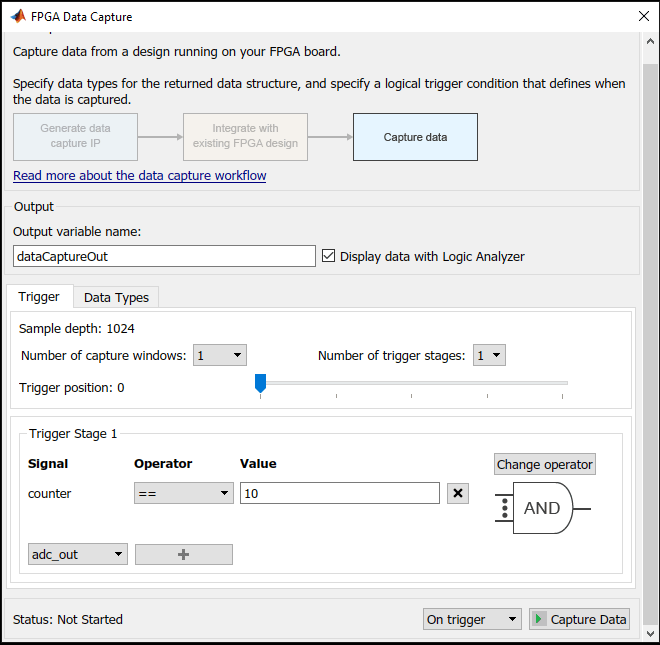

要从FPGA中捕获特定事件的数据,可以在FPGA data capture App中配置触发条件。例如,只在计数器达到一定值后捕获音频数据。

设置“触发阶段数量”为1。在触发阶段1中,从触发信号下拉菜单中选择“计数器”,然后点击“+”按钮启用该触发信号。然后将相应的触发条件值设置为10。触发模式将自动切换为“触发”。这告诉FPGA在捕获和返回数据之前等待触发条件。应用程序设置如下所示:

再次单击“捕获数据”。这次数据捕获IP返回1024个样本,当检测到计数器等于10时捕获。

要在触发值中捕获来自FPGA的数据,而且无论其他位如何,都可以使用位屏蔽值配置触发条件。

例如,仅在计数器第7位为1时捕获音频数据,则将触发条件设置为0bX1XXXXXX,如下图所示:

单击捕获数据。

数据捕获IP触发捕获[64,127]和[192,255]中的计数器值的音频数据。

捕获一个事件的多次发生

要从FPGA捕获重复事件,请在FPGA数据捕获应用程序中配置捕获窗口数。

例如,要捕获8个不同时间段的音频数据,选择“捕获窗口数量”为“8”。配置如下图所示:

单击捕获数据。数据捕获IP返回8个窗口,每个窗口包含128个样本,总计样本深度为1024。

窗口深度=采样深度/捕获窗口数量;

结果在逻辑分析仪中看到为触发器的八个出现,音频数据记录为128个样本:

信号“捕获窗口”和“触发位置”表示相应的窗口数和触发位置。

在多个触发阶段捕获数据

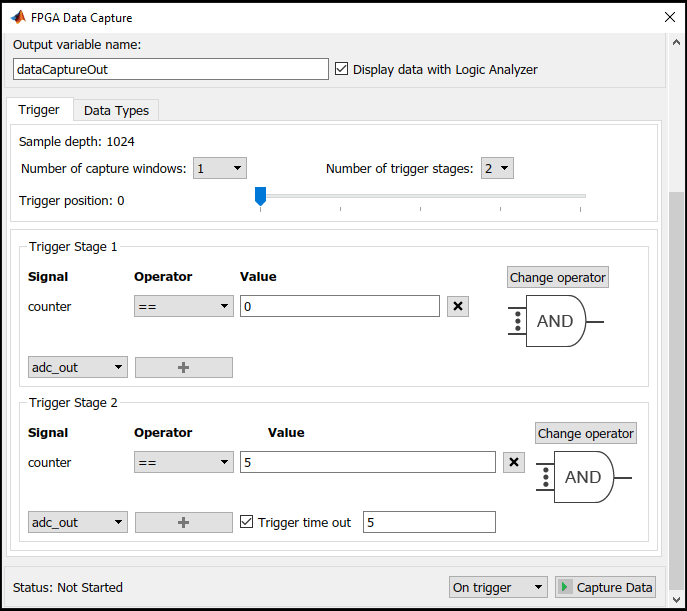

这个场景解释了如何通过在多个触发阶段中提供一系列触发条件来捕获数据。为此,您必须在FPGA Data Capture App中将触发器stage的Number设置为大于1的值。

例如,当计数器值达到0到5时捕获音频数据,在5个时钟周期中达到0到5:

1.将触发阶段的数量设置为2。

2.在触发阶段1中,从触发信号中选择“计数器”,然后单击“+”按钮以启用触发信号。将相应的触发条件值设置为0。

3.在触发阶段2中,从触发信号中选择“计数器”,点击“+”按钮启动触发信号。将相应的触发条件值设置为5。启用触发超时,并将其设置为5。

应用程序设置如下所示:

%单击Capture Data。当数据捕获IP在5个时钟周期内检测到触发器阶段2中的触发条件时,将捕获1024个样本,在此之前检测到触发器阶段1中的触发条件。