使用系统级协同仿真的数字模拟设计的早期验证

作者:汉斯-维尔纳·格罗,阿特梅尔和托马斯·扬茨,阿特梅尔

负责开发嵌入式电子系统的数字基带和模拟射频部分的团队通常是两个截然不同的世界。在爱特梅尔公司®例如,我们的数字团队位于乌尔姆,而模拟团队位于150公里外的海尔布隆。

在我们之前的设计过程中,这种分离不仅仅是地理上的。射频前端和数字基带分别独立开发和仿真。这意味着,在我们真正制造出芯片之前,我们没有办法验证整个系统。修复后硅调试过程中发现的问题需要一段时间,通常会增加几个月的时间和数万欧元的生产成本。解决这个问题的唯一可靠的方法是改进我们的第一次正确的硅工艺。

为了实现这一目标,我们实施了一个设计过程cosimulate数字基带组件的MATLAB®和仿真软金宝app件®用Cadence中的模拟组件®艺术大师®自动对盘及成交系统设计师。这种方法使我们能够在设计阶段验证系统性能,在我们承诺硅之前。

开发模拟和数字组件

Atmel设计流程的目的是使用MATLAB模型作为系统基带和数据处理部分的可执行规范。这个可执行规范指导更详细的VHDL实现,并最终指导晶体管级实现。

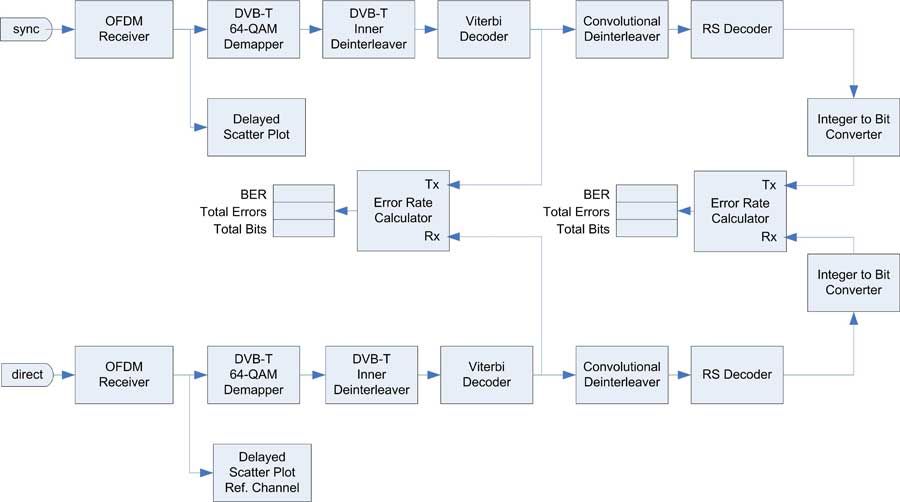

Atmel工程师有多年使用MATLAB开发复杂基带组件的经验,从图1所示的DVB-T解调器开始,其中OFDM解调器、64-QAM解调器、内解交织器、Viterbi解码器、卷积解交织器和Reed-Solomon解码器都是在MATLAB和Simulink中设计和建模的。金宝app对于系统验证,现有的块由一个同步块补充。

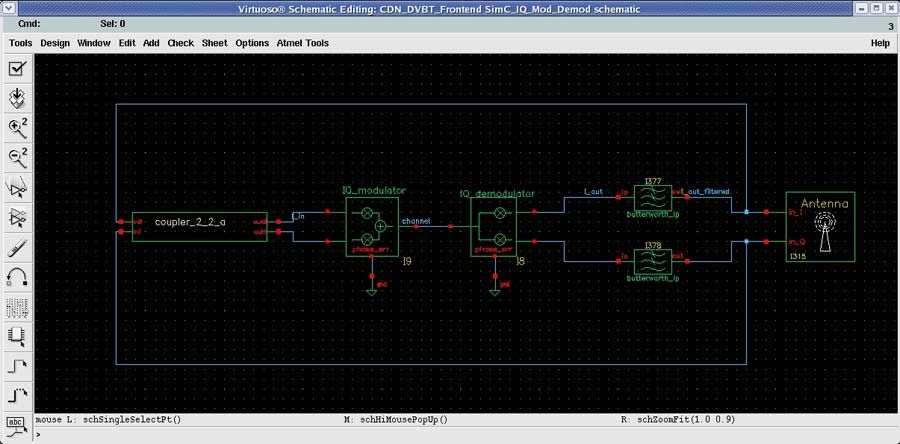

在模拟端,Atmel工程师使用Cadence Virtuoso AMS Designer来设计、模拟和验证模拟和混合信号组件。首先利用行为块对DVB-T系统的射频前端进行建模,以实现快速仿真。随后,这些块被依次替换,首先是通带行为模型,然后是晶体管级模型,以提高模型的精度(图2)。

开发系统级模型

我们的设计通常包括部分由数字逻辑控制的模拟块。例如,模拟设计可以包括自动增益控制与数字组件产生的增益因子。因此,我们的系统级模拟必须包括这个从数字域到模拟域的反馈循环。如果不共同模拟完整的混合信号系统,就不可能验证这些循环是否按预期工作。

Cadence Virtuoso AMS Designer Simulator提供了Simulink和Cadence Virtuoso AMS Design金宝apper之间的双向链接,支持联合仿真和早期验证结合模拟和数字组件的复杂芯片设计。

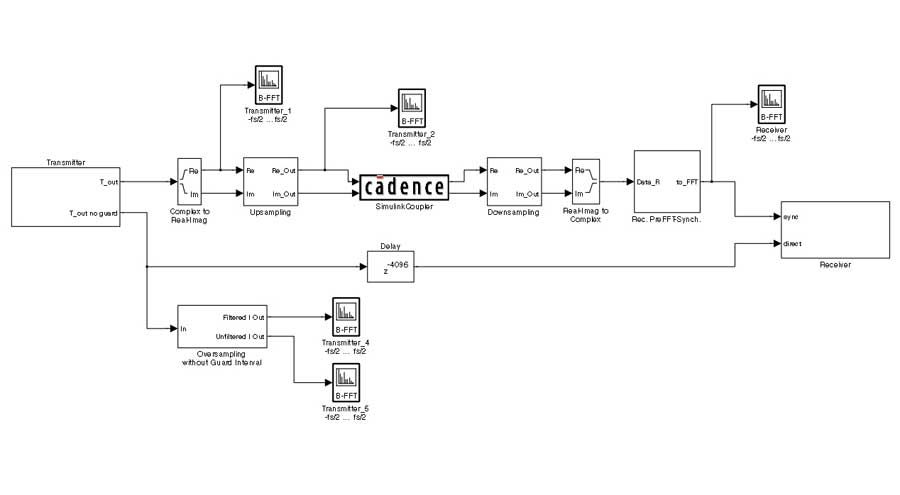

协同仿真接口通过耦合器块实现。我们放置金宝app在Simulink模型中的Simulink耦合器块(图3)表示射频前端的Virtuoso AMS Designer模型。

类似地,我们在Virtuoso AMS Designer原理图编辑器中放置AMS耦合器块,以表示Simulink模型。金宝app这两个耦合器模块相互通信,使协同仿真能够在一台计算机上或在不同的主机上进行(例如,位于Ulm和Heilbronn),甚至在不同的操作系统上进行。耦合器模块提供了一个用户界面,用于配置输入输出参数、采样模式和网络连接设置。

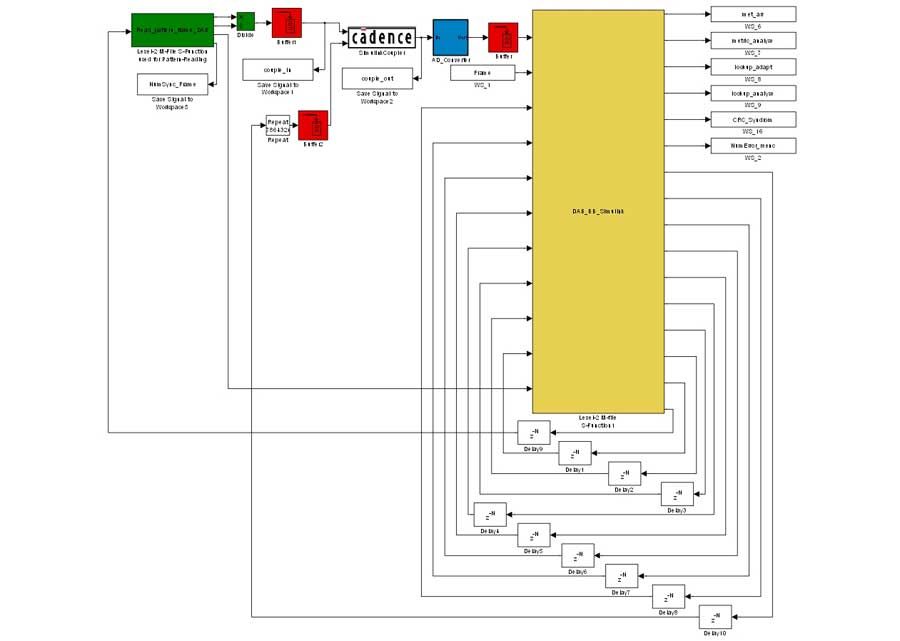

在接下来的步骤中,我们使用了在基于MATLAB的DAB系统中获得的经验。为了在Simulink中创建系统级图,我们考虑将调制、编码等的MATLAB算金宝app法重新实现为Simulink块。但是MATLAB实现已经经过了多年的改进和优化,工程团队希望利用这些时间和精力的投资,尽可能保持原始的MATLAB设计流不被修改。因此,我们使用S-function API来创建一个名为DAB_BB_Simulink的自定义Simulink块金宝app,它集成了这些MATLAB算法(图4)。

这种方法为我们提供了经过验证的MATLAB块的可重用模块,Atmel工程师可以使用这些模块在Simulink环境中组装和验证数字设计。金宝app

同步域

在联合仿真环境中同步两个仿真域是一个至关重要的步骤。在使用Cadence Virtuoso AMS Designer Simulator时,Simulink金宝app作为联合仿真的主控制器,确定耦合信号的数量和数据类型以及同步时间间隔的长度。当联合仿真启动时,Simulink计算耦合器块的输入数据,并通过金宝app耦合接口将该数据与下一个采样点的时间戳一起发送到Virtuoso AMS Designer。Virtuoso AMS Designer在此时间戳之前模拟设计的模拟部分,然后再次通过耦合接口将结果数据发送回Simulink。金宝app

抽样率的选择涉及到工程上的权衡。随着采样率的增加,模拟时间也会增加,得到结果的时间也会变长。然而,设置过低的采样率会导致快速的信号变化被错过。

Cadence Virtuoso AMS Designer Simulator联合仿真接口支持Simulink和Signal Proc金宝appessing Blockset™中可用的不同采样模式,包括固定步长、可变步长、单采样和基于帧的采样。金宝app基于帧的信号将多个样本组成一个单帧,可以同时传输。这通常会提高模拟性能,因为连接块之间的通信较少。在尝试了基于样本和基于框架的同步之后,由于这种性能优势,我们选择了基于框架的方法。

以适当的细节水平进行模拟

对于我们在阿特梅尔设计的那种复杂soc来说,在晶体管级别进行模拟花费的时间太长了。另一方面,只使用更高级别的块来模拟整个系统并不能提供识别问题所需的精确程度。

与MATLAB、Simulink和Virtuoso 金宝appAMS设计器的联合仿真使我们能够在系统级仿真的上下文中验证较低级别的块,同时保持可接受的仿真时间。事实上,我们可以通过用更详细的晶体管级块替换系统级模型的选定部分来轻松地权衡精确度和性能。

此外,联合仿真方法使我们能够在下游设计活动中使用我们的MATLAB算法,弥合早期开发和实现之间的差距。通过将我们现有的MATLAB算法合并为Simulink块,我们享受到将Simulink作为混合信号设计金宝app测试平台的许多好处,包括复杂刺激生成、信号可视化和后处理。

我们已经在Atmel的DAB和DVB-T项目中演示了这种方法的优势。我们可以在任何结合了模拟前端和数字处理的项目中使用相同的工作流。使用MATLAB和Simulink金宝app作为多领域集成、开发和验证平台,是我们朝着第一次正确的硅和无衍生产品的目标迈出的一大步。

发布于2010 - 91808v00