在传统的VHDL®或Verilog®测试台,HDL代码用于刺激描述为逻辑设计和检查设计的输出是否规范相匹配。许多工程师,但是,使用MATLAB®和Sim金宝appulink®帮助创建VHDL或Verilog测试平台,因为该软件提供了高效和紧凑的符号来描述算法,以及用于检查算法行为的可视化工具。

谁以这种方式使用MATLAB和Simulink工程师有多种金宝app选择,用于验证算法的实现HDL是正确的。

验证使用HDL联合仿真

使用组合的MATLAB或Simu金宝applink的测试台与HDL仿真以验证被测设备(DUT)的设计。HDL验证™自动完成此协同仿真过程和执行通信和同步MATLAB或Simulink和所述HDL仿真之间。金宝app在MATLAB或Simuli金宝appnk的试验台可以与来自实况模型和报告的错误比较预期值比较从HDL仿真器的输出值。

验证使用FPGA,在半实物仿真

使用MATLAB或Simulin金宝appk的测试平台与已编程到一个DUT赛灵思®,英特尔®, 要么Microsemi®FPGA开发板FPGA-在半实物仿真。HDL验证可以与FPGA厂商工具组合使用,以编译HDL,建立一个编程文件,将其加载到开发板,和MATLAB或Simulink的会话和电路板之间进行通信。金宝app随着FPGA的在半实物仿真,没有必要产生一个Verilog或VHDL测试台,因为MATLAB或Simulink中起到这个作用。金宝app

验证使用HDL测试台生成使用HDL编码器

什么时候HDL编码器用于从MATLAB代码和Simulink模型生成可合成的HDL代码,您可以选择生成一个独立的Verilog或VHDL测试平台,可金宝app以与几乎任何Verilog HDL模拟器、FPGA开发板或硬件仿真器一起使用。

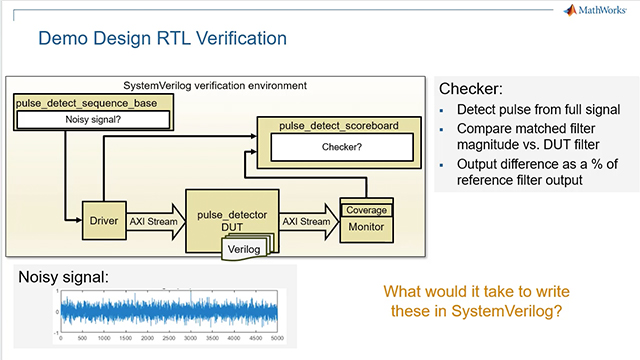

使用SystemVerilog DPI测试台进行验证

SystemVerilog的,用于测试平台开发的Verilog的延伸,是由所有流行的HDL仿真器的支持。金宝app通过SystemVerilog的直接编程接口(DPI),你可以用仿真器,如Synopsys的集成C / C ++代码®VCS®Cadence公司®尖锐®或Xcelium™和Mentor Graphics公司®ModelSim®或奎斯塔®。与MATLAB编码器™或Simulink的编码器组合使用HDL验证™,你可以金宝app生成的SystemVerilog DPI测试台用于生产验证环境。

HDL验证可以产生两种不同的形式的SystemVerilog DPI测试平台:

- 组件测试平台:如果您从Simulink子系统中生成一个C组件作为DPI组件使用,那么您可金宝app以选择生成一个SystemVerilog测试工作台。测试台将对生成的DPI组件进行验证数据向量从Simulink模金宝app型。

- HDL代码测试平台:如果您使用HDL编码器Simulink的子系统生成HDL代码,您金宝app可以选择生成SystemVerilog的测试平台。该试验台比较在HDL实现的输出根据Simulink模型的结果。金宝app