处理器和FPGA同步

在HDL工作流顾问中,您可以选择一个处理器/FPGA同步模式对于处理器和FPGA,当您生成自定义IP核心以在嵌入式系统集成项目中使用时。可用以下同步模式:

自由奔跑(默认)协调性 - 阻止协调性 - 延迟非块

免费运行模式

在自由运行模式下,处理器和FPGA各连续运行,连续和并联。

选择自由奔跑作为处理器/FPGA同步模式当您不希望处理器和FPGA自动同步时。

下图显示了处理器和FPGA如何在免费运行模式下进行通信。阴影区域表明处理器和FPGA正在连续运行。

协调 - 阻止模式

在阻止协调器模式下,HDL Coder™自动为FPGA生成同步逻辑,因此处理器和FPGA串联运行。

选择协调性 - 阻止作为处理器/FPGA同步模式当FPGA执行时间相对于处理器示例时间短时,您希望FPGA在处理器继续之前完成。

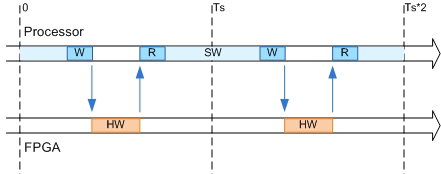

下图显示了处理器和FPGA如何以阻止协调模式运行。

阴影区域表示处理器和FPGA何时运行。在每个示例时间内,处理器都会写入FPGA,然后停止并等待FPGA在继续运行之前完成处理。每次FPGA运行时,它都会在一个DUT子系统样本时间内执行生成的逻辑。