内存和寄存器数据传输

一个SoC应用程序由一个或多个算法组成。当一个算法将数据传输到另一个算法时,该数据在Simulink中表示为信号线金宝app®.对于行为模型,数据传输是即时的。

此图表显示了两种算法之间数据路径的行为模型。

在物理世界中,算法可以在两个独立的设备上,数据传输不会立即发生。此外,算法可以以不同的速率运行,因此握手需要缓冲和控制逻辑。例如,简单的握手,例如来自数据生产者的“数据是有效的”和来自消费者的“准备接受数据”,可以作为控制逻辑。

如果一个处理元素在FPGA或ASIC中执行,而下一个处理元素在嵌入式处理器中执行,那么一个简单的信号线就不仅仅代表一个复杂的硬件数据路径。数据传输还表示一个处理器中断处理程序、一个操作系统任务调度程序和一个软件驱动程序堆栈。

在SoC Blockset™中,通过共享内存建模数据传输和握手协议。使用一个内存通道块的外部内存或注册通道寄存器的块。

用内存通道块建模数据路径

的内存通道块表示通过外部内存对复杂数据路径的抽象,并支持不同的握手协议。金宝app它有助于改进处理元素之间的通信,从即时的、无协议的电线到处理器和FPGA之间的完全直接内存访问(DMA)连接。

通过添加内存通道块,您可以建模数据从算法的一个部分移动到另一个部分。

该块提供了通信管道的模型。该通道还提供了一个信令接口。

接口协议取决于执行处理的位置。FPGA或ASIC算法可以使用标准协议(如AXI4- stream或AXI4)执行数据传输。嵌入式CPU算法可以使用导出到用户空间的驱动程序接口。

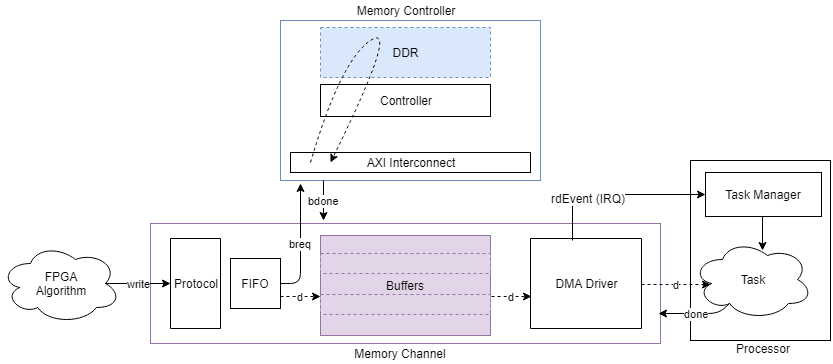

此图显示了从FPGA算法流数据到处理器算法的数据路径模型。

其他内存通道类型选择通过外部内存对其他公共数据路径建模。有关内存通道配置,请参阅内存通道.

写入器和读取器连接到存储器并请求从存储器控制器访问外部存储器。有关的更多信息内存控制器块,看内存控制器.

用寄存器通道块建模数据路径

的注册通道块表示处理器通过公共配置总线(如axis - lite)进行读写的序列化。

的注册通道Block为通过公共配置总线在处理器和硬件算法之间传输寄存器值提供了一个定时模型。当处理器写入命令或配置寄存器或处理器读取状态寄存器时使用此块。