随机访问外部存储器

这个例子展示了如何从FPGA为旋转模型外部存储器访问一个ASCII艺术形象。许多应用程序需要FPGA在随机存取存储器/算法的要求。您将学习如何设计内存地址代以及其他AXI4主信号读取和写入特定区域的内存使用SoC Blockset。你会模拟,设计硬件实现和验证。

金宝app支持硬件平台:

Artix®7 35 t附庸风雅的FPGA评估工具

Xilinx®Kintex®7 KC705发展局

Xilinx Zynq®ZC706评估工具

Xilinx Zynq UltraScale™+ MPSoC ZCU102评估工具

Xilinx Zynq UltraScale™+ RFSoC ZCU111评估工具

阿尔特拉®气旋®V SoC开发工具包

阿尔特拉Arria®10 SoC开发工具包

设计任务

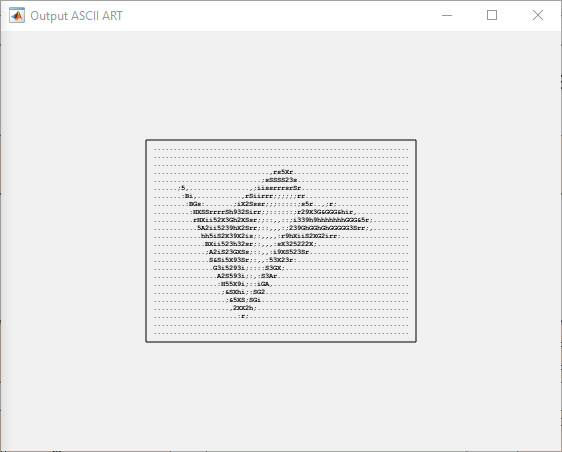

ASCII艺术图像编码为24 -到- 64矩阵uint8字符。设计任务是旋转图像建模AXI4主接口的FPGA逻辑外部内存访问。通过模拟设计与外部内存模型和AXI4协议,你验证在设计应用程序时的行为。这节省了时间,否则在调试硬件设计实现阶段。

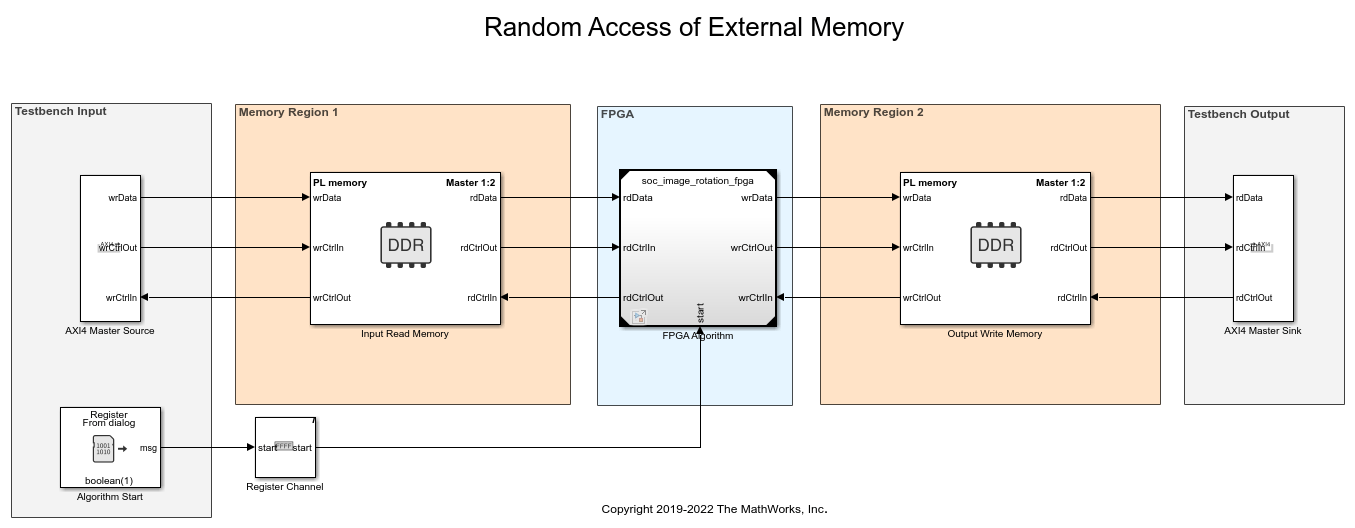

整个数据流如下图中描述。图像存储在外部存储在内存区域从地址0 x00000000 0 x000017ff。FPGA算法从本地区和读取图像旋转通过编写它按照相反的顺序从0 x00001800到内存区域。最后,从内存中读取数据。

模型结构

使用模型引用的模型结构。顶级模特的soc_image_rotation“包括FPGA模式”soc_image_rotation_fpga使用模型块”模型参考。

顶部模型包括以下方面:

Testbench输入:它刺激建立模型仿真的设计。的

AXI4主源初始化输入图像数据块到外部内存。的算法开始阻止发送起始信号通过注册通道块FPGA算法。打开预加载功能soc_image_rotation_init.m看看模型参数和输入数据初始化。Testbench输出:

AXI4大师沉模型输出图像的读取数据块从外部内存。输出数据是保存在变量AXI4MasterSinkContent工作区。打开停止功能soc_image_rotation_post.m看到输入数据和输出数据是如何绘制的。内存:内存系统建模使用两个AXI4随机存取内存块。

输入读取内存块模型1,输入图像存储和内存区域输出写入内存块模型旋转图像存储内存区域2。FPGA:这方面实例化FPGA模型参考模型的逻辑AXI4主接口和数据旋转。

FPGA在三个子系统模型实现了算法,AXI4MasterRead,ReverseDataOrder和AXI4MasterWrite。开放的FPGA图像旋转的子系统:

积极的边缘开始检测到信号时,AXIMasterRead读取一行数据,并将其形象ReverseDataOrder改变数据的顺序。然后反向数据写入外部存储器AXIMasterWrite子系统。一旦写一行的数据,它发送一个信号request_next_line触发读下一行的AXIMasterRead。这个循环过程一直持续到所有的图像处理。

开放AXI4MasterReadController和AXI4MasterWriteController块检查的MATLAB®代码AXI4主接口。这些块设计解决逻辑读和写操作按AXI4协议。SoC Blockset支金宝app持AXI4主协议和AXI4信号的时序图,请参考模型设计AXI4主界面的一代(高密度脂蛋白编码器)。

模拟

运行模型和开放的FPGA逻辑分析仪的模型。请注意以下要点:

一行数据写入/读取硕士学位一个破裂。因为每一行是64字符;突发长度是64 (0 x40)。注意这个值在信号

rd_len和wr_len。每个角色都有4个字节是扩展到uint32数据类型,使线的长度64 x4 = 256 (0 x100)字节。因此,地址0 x100递增/递减。请注意这个

rd_addr和wr_addr信号。一个读破裂是紧随其后的是一个写破裂。观察

rd_dvalid和wr_dvalid或者切换。request_next_line断言每个写破灭后,触发下一个读取破裂。

输入和输出图像绘制仿真结束时:

实现

以下产品需要这部分:下载188bet金宝搏

高密度脂蛋白编码器™

SoC Blockset 金宝appXilinx设备支持包,或

SoC Blockset为金宝app英特尔®设备支持包

实现模型支持的FPGA板上,使用金宝appSoC建设者应用程序。确保您已经安装了所需的产品和FPGA供应商之前软件实现。下载188bet金宝搏

开放SoC建设者通过点击“配置、构建和部署”按钮在将来发布和遵循这些步骤:

选择“设置”屏幕上建立模型。单击“Next”。

点击“查看/编辑内存映射”查看屏幕上查看内存映射的内存映射。注意,基地址0 x00000000分配

输入读取内存块,基地址0 x00001800分配输出写入内存块。AXI4地址基地址的总和和地址从FPGA的算法。例如,wr_addr从FPGA算法从0 x1700开始。输出数据将被写入到外部存储器从地址0 x00001800 + 0 x1700 x00002f00 = 0。指模型设计AXI4主界面的一代(高密度脂蛋白编码器)关于基地址寄存器的更多信息计算。单击“Next”。指定屏幕上选择项目文件夹的项目文件夹。单击“Next”。

选择“建立、加载并运行”屏幕上的选择构建操作。单击“Next”。

点击“验证”检查的兼容性模型验证模型的屏幕上实现。单击“Next”。

点击“建立”开始构建模型的构建模型的屏幕上。外部壳FPGA合成开始时将打开。单击“Next”“负载比特流”屏幕。

FPGA合成可能需要超过30分钟才能完成。为了节省时间,你可能想要使用提供的预生成的比特流通过以下步骤:

关闭外部shell终止合成。

预生成的比特流复制到项目文件夹通过运行下面的命令,然后

单击“加载”按钮加载预生成的比特流。

拷贝文件(fullfile (matlabshared.sup金宝appportpkg.getSupportPackageRoot,“工具箱”,“soc”,“金宝appsupportpackages”,“xilinxsoc”,“xilinxsocexamples”,“比特流”,“soc_image_rotation-zc706.bit”),”。/ soc_prj ');

运行这个例子,试验台的示例复制到项目文件夹中。

拷贝文件(fullfile (matlabroot,“工具箱”,“soc”,“socexamples”,“soc_image_rotation_aximaster.m”),”。/ soc_prj ',“f”);

输入以下命令运行试验台:

soc_image_rotation_aximaster

试验台执行以下操作:

初始化图像旋转的IP

将输入图像数据写入外部存储器

图像旋转操作开始

读取和显示输出图像数据从外部内存

如果你的FPGA板不是Xilinx Zynq ZC706评估设备你需要做以下设置配置参数的模型前启动SoC建设者。

选择“硬件实现”下的“硬件板”面板来匹配你的董事会。

取消“包括处理系统”下的硬件实现硬件资源- > - >目标FPGA设计(顶级)”面板。

可用的预生成的比特流:

“soc_image_rotation-zc706.bit”

“soc_image_rotation-arty.bit”

“soc_image_rotation-zcu102.bit”

“soc_image_rotation-XilinxZynqUltraScale_RFSoCZCU111EvaluationKit.bit”

“soc_image_rotation-kc705.bit”

“soc_image_rotation-a10soc.sof”

修改拷贝文件命令和例子试验台来匹配你的董事会和选择适当的项目文件夹。在阿尔特拉Arria®10 SoC开发工具包,阿尔特拉气旋®V SoC开发工具包使用下面拷贝文件命令对应你的董事会。

拷贝文件(fullfile (matlabshared.sup金宝appportpkg.getSupportPackageRoot,“工具箱”,“soc”,“金宝appsupportpackages”,“intelsoc”,“intelsocexamples”,“比特流”,“soc_image_rotation-a10soc.sof”),”。/ soc_prj ');

注意,预生成的比特流可能不工作如果你定制内存映射。

结论

这个例子展示了建模AXI4主接口来访问外部存储器以随机的方式使用SoC Blockset旋转一个ASCII艺术形象。你可以使用这个为指导来设计自己的算法来直接访问内存使用AXI4主协议。