。

プログラミング可能なFPGA用途冷杉フィルター

この可例は,プログラミング可能な用枞フィルターの装备方法をホストを使ししててててててて応答ででことでででプログラムことができことことでするする目ことで応答することができことができことができことができことができことができことができことができ

この例では,1つのチップ上にそれぞれ応答异なる异なるののででされるをを形式のますののフィルターすべてに直接直接直接形式形式直接形式直接直接直接直接ががががががががありありありありありありありありありありありありありありありありあり同じありありあり同じインターフェイスインターフェイスを使て,各応答のの数をレジスタに読み込むことができます。

この设计により,入力サンプルを読み込まれたでで前ようよう前前にただしただしれれただしただしただしれれますますただしれれれれますハードウェアれれでしして系ででししててれでプログラムしてててのプログラムししてての応答により,チップ领域がさ。そうでないと,チップと,チップことになりことになり。

プログラミング可能冷却フィルターフィルターモデルモデル化

2つの冷却フィルターについてについて検讨します。关键initfcn([モデルプロパティ],[in],[in],[in],[in],[in],[in],[in],[in]使しててを指定します。

通过寄存器的可编程FIRブロックが,主机行为模型次からチャープサンプル最初にます,に,ハイパスハイパスを読み込み,同じチャープサンプルを読み込み,同じチャープサンプルを読み込み,同じ同じチャープサンプルを再度読み込みし。

with_enable.信号が高度综合,Coeffs_Registers.ブロックブロック分数を内部レジスタに読み込みます。write_done.信号が高度综合,シャドウレジスタががレジスタから新闻さます。シャドウシャドウにより,フィルターエンティティによるデータの読み込み読み込みブロックががなります。これらのブロックはますますますのは,最后のいくつかののサンプルのいくつとと时に,2组目のの数を読み込み。

このモデルは,完全に并列なアーキテクチャを离散冷冻滤波器ブロックブロック使使使にするようにににいいいいいいいいいいいいいいいいい。[HDL块属性]メニューメニューから直列アーキテクチャアーキテクチャを选択こともできできすることもでき

金宝appSimulink®のシミュレーションシミュレーション

テスト対象设计(DUT)と参照フィルターを比较するは,スコープを开放てモデル例実行します。

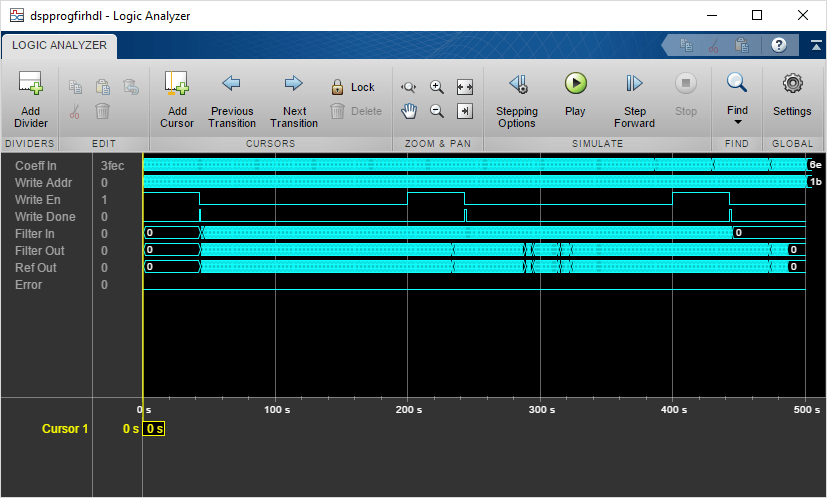

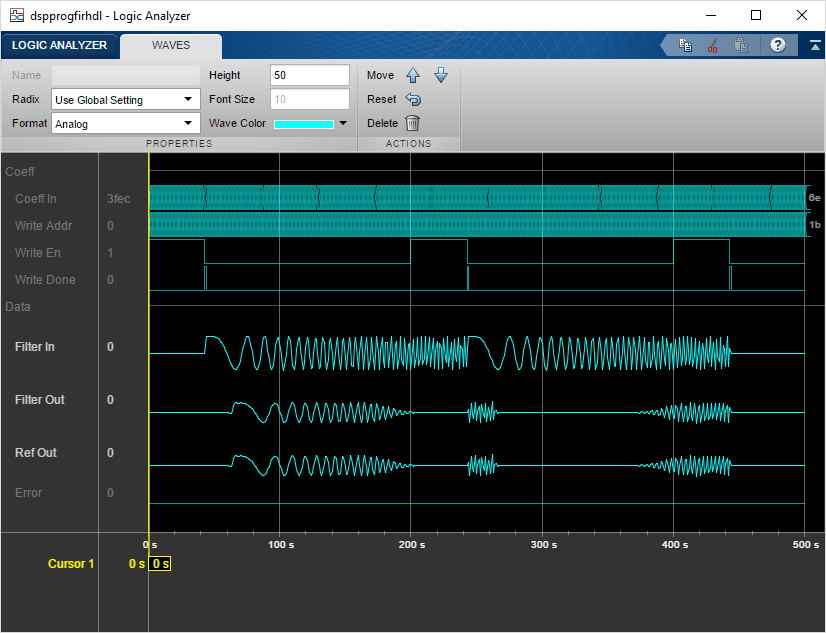

ロジックアナライザーの使用

信号ははアナライザーアナライザーも表示できロジックロジックアナライザーでははウィンドウウィンドウででまたまたまたまたことができ表示できでき信またことができ表示できを信ことができ表示でき単単见つけることができことができことができ

モデルモデルのツールバーからからロジックをを起しし

対象対象信号输入系数,写入地址,写入启用,写入,过滤,过滤滤网,参考および错误が,観测のためロジックアナライザーアナライザー加值されいます。

ロジックアナライザーの表示波形ごとデバイダーデバイダーごと制御すること波形できますをするするにはやデバイダーをにはははははははにはははてててててててててててててててをクリッククリックしロジックロジックにををクリッククリックしますロジックににをクリッククリックししロジックににををクリッククリックしますロジックロジックにおけるをクリッククリックします可使モードて,アナログ形式の表示があり。

ロジックアナライザーの详细については,ロジックアナライザードキュメンテーションを参照してください。

HDLコードコードとテストテストの生成

このモデル例のHDLコードを生成するは,HDL编码器™ののが必要です。このこのを使使してhdlコードを生成します。

systemname = [modelname'/可编程FIR通过寄存器'];makehdl(systemname);

このこのを使使使ててhdlシミュレーションの结果とsimu金宝applinkシミュレーションの动作をするテストベンチ生成し.makehdltb(systemname);

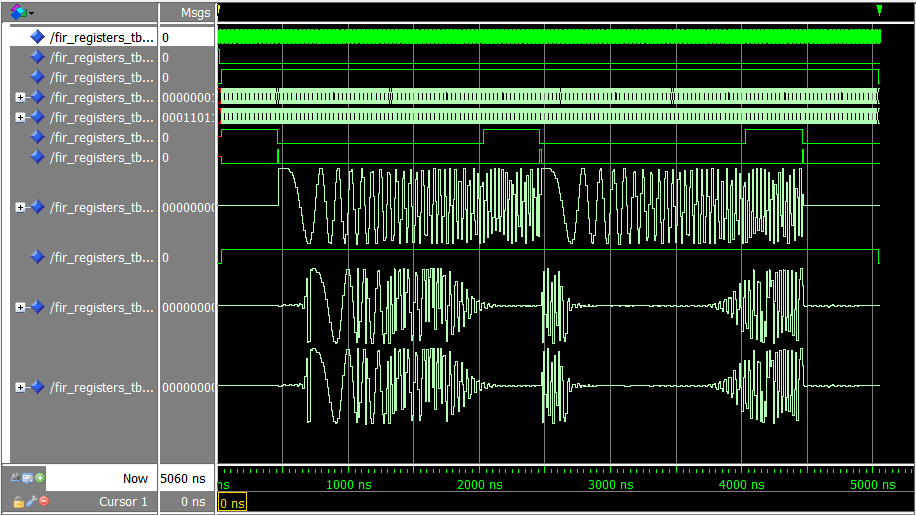

modelsim™のシミュレーション结果

生成した。DOファイルスクリプトをテストベンチ実し后の模特ししを以の図示しますます。以前にプロットしに,mepenterim结果とsimulink结果を比较ます。金宝app