基于COM的ADC IBIS-AMI模型

此示例演示如何使用SerDes工具箱中的库块创建基于IEEE 802.3ck规范ADC的发射机和接收机IBIS-AMI模型™ 库和自定义块,用于为时间无关ADC建模。生成的模型符合IBIS-AMI标准。虚拟采样节点存在于基于切片器的SerDes系统中,但不存在于基于ADC的SerDes系统中,仿真该节点以允许在Simulink®和IBIS-AMI模拟器中生成虚拟眼图,用于评估通道。金宝app

使用MATLAB脚本设置SerDes IBIS-AMI模型

本例使用MATLAB®脚本首先构建一个SerDes系统,表示ADC体系结构的发射机和接收机,然后导出到SerDes Simulink模型。在MATLAB命令窗口中键入此命令以运行脚本:金宝app

buildSerDesADC

SerDes系统在导出到Simulink之前配置了以下属性。请注意,在应用本示例稍后讨论的Simulink自定义设置之前,自定义块将用作传递。金宝app

配置设置

符号时间设置为18.8235ps,因为允许的最大802.3ck工作数据速率为106.25Gb/s。

目标误码率设置为1e-4。

每个符号的样本数设置为32。

调制设置为PAM4。

信号设置为差分。

发射机型号设置

Tx FFE块通过包括5个抽头重量为3个预抽头和1个后抽头设置。

Tx VGA模块用于控制发射振幅。

Tx AnalogOut模型是这样设置的电压是1V,上升时间6.161 ps,R(输出电阻)为50欧姆C(电容)根据802.3ck规范为5fF。

通道模型设置

频道损失设置为15dB。

目标频率设置为奈奎斯特频率。

微分阻抗默认值保持在100欧姆。

接收器模型设置

Rx AnalogIn模型是这样建立的R(输入电阻)为50欧姆C(电容)根据802.3ck规范为5 fF。

噪声自定义块将高斯噪声注入时域波形。

分别为7、21和1配置设置3个Rx CTLE块的级联。这个GPZ(增益极点零)矩阵数据从802.3ck行为CTLE规范中给出的传递函数中得到。

Rx VGA自定义块应用自适应增益。

饱和放大器模块采用无记忆非线性。

ADC自定义块对时域信号进行量化。

Rx FFE自定义有21次点击(3次前光标和17次后光标点击),其权重将在Rx全局适应期间自动计算。

为一个DFE抽头设置Rx DFECDR块。DFE抽头的振幅限制为+/-0.5V。

在Simulink中建立基于adc的SerDes Tx/Rx IBIS-AMI模型金宝app

本例的第二部分采用脚本导出的SerDes系统,并根据Simulink中基于adc的SerDes的需要对其进行定制。金宝app

查看Simul金宝appink模型设置

导出到Simulink中的SerDes系统由配置、刺激、Tx、模金宝app拟通道和Rx块组成。

推入Tx子系统。

推入Rx子系统。

为基于ADC的SERDE定制模型

从SerDes应用程序导出的模型首先需要通过定制额外的Rx块和修改Rx初始块代码来定制,以表示基于ADC的SerDes Rx。

配置输入参考Rx噪声块

Rx子系统中的噪声可以在输出或输入处建模。输入参考噪声源由随后的均衡阶段(CTLE和FFE)塑造,因此更好地反映了噪声是如何被真实系统塑造的。另一方面,输出参考噪声是不成形的,并且没有捕捉到改变CTLE和FFE上的设置对噪声的影响。

单击块上的向下箭头,进入名为Noise的直通块。

将现有的系统对象指向Noise。M系统对象。看到在SerDes工具箱传递块中实现自定义CTLE.

在系统对象掩码中,使用系统变量配置“符号时间”、“采样间隔”和“调制”。

在IBIS-AMI管理器中为名为的噪波块创建IBIS-AMI参数NoisePSD使用图中的属性。值8.2e-9来自COM标准。看见管理AMI参数.

将生成的常量块连接到Noise输入端口。

配置VGA块

进入名为VGA的直通块。

将现有系统对象指向serdes工具箱中包含的serdes.VGA系统对象。

在系统对象掩码中,关闭模式端口以强制打开块。

在IBIS-AMI管理器中为名为的VGA块创建IBIS-AMI参数获得使用图中的属性。

连接生成的数据存储读取以获得输入端口。删除数据存储写入,因为它将不被使用,因为该值仅在Init中更新,而不是在时域中更新。

VGA适配

VGA自适应很简单,所需增益在Init中计算为目标脉冲振幅与输入脉冲响应的最大峰值的比值。然而,对于不同的CTLE设置,所需的VGA增益可能是不同的,因此需要在前面描述的通用算法的每次迭代中评估VGA增益。

配置ADC块

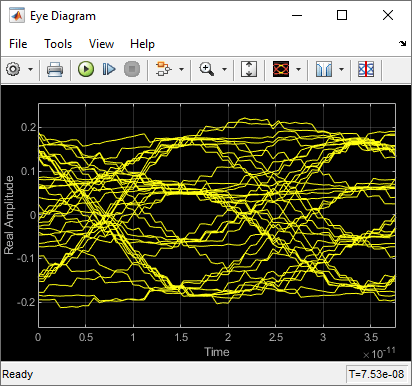

使用的ADC模型是一个时间无关的ADC,这意味着模拟中的每个点都是量化的,而不仅仅是在采样瞬间。然而,DFE和时钟恢复仍然只在采样瞬间使用ADC采样。一个不确定时间的ADC允许生成一个等效波形,如图所示在DFE求和节点:允许构建具有代表性高度和宽度的信号眼图。

下行到名为ADC的直通块

将现有系统对象指向示例目录中的ADC.m系统对象。

在系统对象掩码中,使用系统变量配置“符号时间”、“采样间隔”和“调制”。

配置接收FFE

下降到名为Rx_FFE的直通块

将现有系统对象指向serdes工具箱中包含的serdes.FFE系统对象。

在系统对象掩码的主选项卡中,关闭模式端口并关闭规格化抽头。在“高级”选项卡中,使用系统变量配置符号时间和采样间隔。

在IBIS-AMI Manager中为Rx_FFE块创建一个tap结构,包括3次前光标点击、17次后光标点击和如图所示的属性。

[零(1,3)1零(1,17)]

连接生成的数据存储读取轻按权重输入端口。当数据存储不再使用时,删除该数据存储的写操作。

企业适应

Rx FFE在ADC采样数据上运行,而不是在连续波形上运行。然而,在统计自适应期间,假设所有波形点(即使在数据样本之间)都可用。Rx FFE仅适用于自定义用户初始化代码;自适应由提供的adaptFFE功能辅助。Rx FFE自适应目标是在给定输入脉冲响应的情况下驱动输出脉冲响应,从而将光标前和光标后数据样本驱动至零。这并不意味着除光标点外,脉冲响应为零。相反,与同步波形非常相似,ISI仅在数据采样点被驱动为零。

由于Rx FFE对采样数据进行操作,自适应过程中的第一步,在adaptFFE中,是假设输入脉冲响应的数据采样相位。所使用的方法是贪婪地假设我们可以强制采样,以便光标落在传入脉冲响应的峰值上。

由于在Rx子系统中,Rx FFE之后是一个1-tap DFE,因此Rx FFE不需要强制第一个后光标为零。相反,Rx FFE需要确保第一个后光标落在1-点击DFE的均衡范围内。注意,如果没有使用后Rx DFE,那么目标将是零强迫所有前光标和后光标ISI。

给定现在采样的输入脉冲响应,目标是找到一个过滤器响应,使光标前和后数据样本为零,或者在第一个后光标样本的情况下,进入DFE的范围。这个优化问题与求解一组线性方程组密切相关,我们需要找到矩阵的逆。这个需要反求的矩阵是由循环移位的输入采样脉冲响应组成的矩阵。这个反矩阵然后乘以期望的输出目标脉冲响应:[0,0,0,1,bmax, 0,0…]对于3-tap前驱Rx FFE的情况,其中1表示光标位置,bmax表示DFE的最大范围。所需的Rx FFE FIR滤波器系数是反向的、循环移位的输入脉冲响应矩阵和所需的输出脉冲响应的乘积。

DFECDR适配

DFECDR自适应遵循Rx FFE自适应。DFECDR是SerDes工具箱中的标准块,请参阅DFECDR块的联机文档。

此示例使用Alexander(bang-bang)相位检测器,而不是基于ADC的SerDes系统中通常使用的波特率相位检测器。这种建模选择简化了示例,因为波特率相位检测器将与自适应收敛相互作用。基于ADC的SerDes系统需要处理CDR锁定点与Rx FFE和DFE自适应之间的交互。

自定义Rx子系统初始化代码块

在此示例中,在统计域中执行Rx子系统自适应:涉及CTLE、FFE和DFE的共同自适应,以在给定所使用的信道和Tx FFE设置的情况下实现最佳可能的BER。在时域仿真期间,CTLE和FFE的优化设置将保持不变,而DFE和CDR将在时域仿真期间继续适应。

使用示例提供的代码修改Init的自定义用户代码区域。看见使用脉冲响应度量对接收机组件进行全局调整,以提高SerDes性能.

单击“初始化掩码”对话框上的“刷新初始化”,根据前面的步骤更新代码。

单击“初始化掩码”对话框上的“显示初始化”打开初始化代码。

将代码复制到

adcInitCustomUserCode.m在示例目录中。

编辑adcInitCustomUserCode.m

将复制的代码粘贴到自定义用户代码区域的末尾之前。确保保留自定义用户区域顶部的AMI参数。不要修改超出自定义用户区域末尾的代码。

统计适应算法

统计自适应算法通过每个Rx子系统块处理脉冲响应,并测量得到的脉冲响应优值。由于这是一个基于adc的系统,使用的优点是信噪比(SNR),其中噪声项还包括残留的前光标和后光标ISI。

一般而言,统计接收自适应将按如下方式进行:

选择了一个初始的CTLE设置

选择VGA设置使脉冲振幅落在目标范围内

Rx FFE自动调整,以使数据采样点的ISI最小化。

DFE适用于移除光标后ISI。

计算了数据采样点的信噪比。

对每个可能的CTLE设置重复上述步骤,跟踪每个设置的SNR值。选择具有最高信噪比的设置作为全局自适应点。

运行Simuli金宝appnk模型

访问“刺激块遮罩”对话框,将符号数更改为4000。

访问IBIS-AMI Manager的导出选项卡并将Rx忽略位更新为2000。这和之前的修改将确保时域自适应有足够的时间收敛。更多的符号和忽略时间将产生更现实的结果。

运行该模型对基于adc的SerDes系统进行仿真。

更新ADC量化

在该示例中,默认情况下,ADC量化设置为6b。尝试将ADC量化更改为较低的量,观察降低的ADC精度对时域眼睛形状的影响。

生成基于ADC的SerDes IBIS-AMI模型

本示例的最后一部分采用定制的基于adc的SerDes Simulink模型,然后生成一个符合IBIS-AMI的模型:包括模型可执行文件、I金宝appBIS和AMI文件。

当前的IBIS AMI标准不支持基于ADC的SERDE。当前标准是为基于切片器的SERDE编写的,该S金宝appERDE包含观察均衡信号波形的信号节点。在基于切片器的SERDE中,该节点存在于DFE内部,就在决策采样器之前。在该节点处可观察到连续模拟波形,其包括所有上游均衡器(例如CTLE)的效果以及由于DFE而产生的均衡,作为抽头加权和反馈的先前判决。由于系统中的ADC,在基于ADC的SERDE中不存在这样的求和节点。在实际的基于ADC的SerDes系统中,ADC在采样瞬间证明了通过眼睛的垂直切片。为了模拟虚拟节点,使用时间无关的ADC。该ADC以模拟时间步长速率对输入模拟波形中的每个点进行量化:即1/fB/SPS,其中SPS是每个符号的采样数,fB是波特率。Rx FFE还将输入信号处理为连续波形,而不是采样。但是,Rx FFE对SPS模拟时间步长应用单个抽头值。DFE是SerDes工具箱中的库存DFE,是为基于切片器的SerDes编写的。该信号链允许信号完整性模拟器能够在基于ADC的系统中观察虚拟眼睛。

出口IBIS-AMI模型

打开出口选项卡。

验证二元模型为Tx和Rx AMI型号设置选择。这将创建同时支持统计(Init)和时域(GetWave)分析的模型可执行文件。金宝app

设定Tx模型忽略值的比特到5,因为在Tx FFE有三次点击。

设定Rx模型忽略值的比特数到20,000,以便有足够的时间让Rx DFE接头在时域模拟期间稳定下来。

设置模型出口作为Tx和Rx都有以便选择要生成的所有文件(IBIS文件、AMI文件和DLL文件)。

按下出口按钮在目标目录中生成模型。

另见

CTLE|DFECDR|固定资产|SaturatingAmplifier|VGA