SoC Blockset

设计、评估和实现SoC硬件和软件体系结构

SoC块集™提供Simulink金宝app®块和可视化工具建模,仿真和分析的硬件和软件架构ASIC产品,FPGA和一个芯片(SoC)上的系统。您可以使用的内存模型,总线模型和I / O模型建立自己的系统架构,并与算法一起模拟架构。

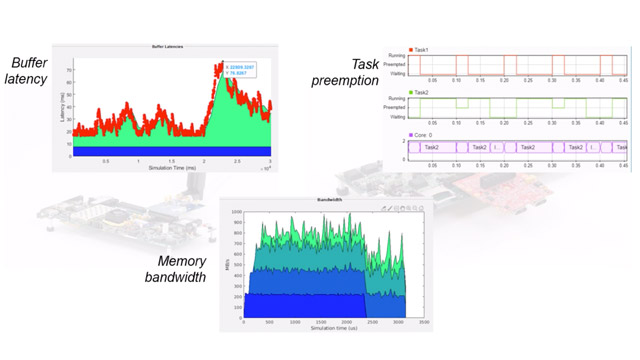

SoC块集允许您使用生成的测试流量或真实的I/O数据模拟内存、内部和外部连接,以及调度和操作系统效果。您可以快速探索不同的系统体系结构,评估硬件和软件分区的接口复杂性,并评估软件性能和硬件利用率。

SoC的模块库出口的参考设计针对Xilinx®和英特尔®FPGA设备和SoC平台,包括Zynq®-7000,UltraScale架构+™和英特尔的SoC FPGA的。这些参考设计可与赛灵思和英特尔的设计工具来使用。

入门:

分析算法的资源使用情况

分析Simuli金宝appnk模型或MATLAB函数,生成报告,总结实现所需的算术运算符数量。使用这些报告来比较不同的体系结构,执行设计权衡,并探索硬件/软件分区。

SoC模型模板

使用逐步的方法从头开始构建完整的SoC应用程序模型,或者从用于软硬件协同处理的预定义模板(包括用于视觉和通信应用程序的模板)开始。

任务执行分析

通过运行包含时间驱动和事件驱动任务的Simulink模型来模拟SoC应用程序的软件系统。金宝app可视化任务执行时间、抢占、速率溢出、下降和核心利用率。使用从以前的模拟中捕获的或直接从SoC设备中捕获的任务定时数据,在模拟中重新执行任务。

设备上的存储性能监控和任务执行剖析

衡量内存性能和SoC的设备上执行任务,然后可视化这些测量分析调整的SOC模型,以满足您的系统性能要求。在互动与MATLAB或从您的Simulink测试平台SoC器件的实时性。金宝app

生成参考设计

为可编程逻辑生成参考设计。参考设计是通过数据和控制路径配置的IP核心网络,这些数据和控制路径可以连接到外部存储器和软件应用程序。SoC块集连接到Xilinx和Intel设计工具来产生比特流,然后对FPGA和SoC板进行编程。

生成算法IP

生成与目标优化算法IP高密度脂蛋白编码器™。整合产生的IP到设计,从系统芯片模块库导出的基准,并使用FPGA供应商的工具来生成完整的比特流。

生成应用软件

采用嵌入式编码,生成软件应用程序代码并将其部署到一个SoC的硬件板卡。SoC的模块库自动创建任务;它们分配给线程;和链接中断,消息和系统事件,生成的代码。

目标胶辊板和定制板

在支持的硬件包上实现硬件/软件应用,包括Xilinx Zynq UltraScale+ 金宝appMPSoCs和RFSoCs, Zynq-7000 SoCs和Intel Cyclone和Arria SoC fpga。目标板使用硬件支持包或构建自定义板的支持。金宝app

参考设计

从你的SoC块集Simulink模型导出自定义参考设计金宝app

算法分析

在设计过程的早期,分析MATLAB函数或Simulink模型的计算复杂度金宝app

代理任务块增强

为不知道实现的任务组件建模异步任务执行

IP内核寄存器读块

从处理器到硬件逻辑的模型写操作

I2C主座增强

将配置支持扩展到其他从设备,并与运行缓慢的金宝appI2C从设备进行同步

Xilinx UltraScale+ RFSoC支金宝app持

模拟赛灵思RFSoC设备的硬件/软件架构,那么应用程序部署到ZYNQ的UltraScale + RFSoC ZCU111评估套件

看到发行说明有关这些功能和相应功能的详细信息。

MATLAB的FPGA,ASIC和SoC开发

领域专家和硬件工程师使用MATLAB®和Sim金宝appulink®开发原型和生产应用对FPGA,ASIC和SoC设备的部署。