与第三方EDA工具集成

生成默认脚本

编码员生成脚本作为代码和测试台生成过程的一部分。脚本文件在目标文件夹中生成。

当为过滤器生成HDL代码时,filt,编码器编写以下脚本文件:

filt_compile.do:导师图形®ModelSim®编译脚本。这个脚本包含编译生成的过滤器代码的命令,但不包含模拟它的命令。

当为筛选器生成测试台代码时filt,编码器编写以下脚本文件:

filt_tb_compile.do:导师图形ModelSim编译脚本。这个脚本包含编译生成的过滤器和测试台代码的命令。filt_tb_sim.do:导师图形ModelSim仿真脚本。这个脚本包含一些命令,用于运行生成的过滤器和测试台代码的模拟。

您可以启用或禁用脚本生成,并自定义生成的脚本文件的名称和内容:

传递特性

“名字”,价值的参数generatehdl函数。看到HDL合成和工作流自动化特性.在Generate HDL对话框中设置相应的选项。选择EDA工具脚本选项卡,并单击编译脚本或仿真脚本从左边栏的菜单中。看到自定义编译和模拟脚本.

生成脚本文件的结构

生成的EDA脚本由三个部分组成,它们的生成和执行顺序如下:

一个初始化(

初始化)阶段。的初始化阶段执行所需的设置操作,例如创建设计库或项目文件。每个文件的命令阶段(

Cmd).脚本的这个阶段是迭代调用的,每个生成的HDL文件调用一次。终止阶段(

术语).这个阶段是脚本的最后执行阶段。该阶段的一个应用程序是执行在Cmd阶段。

对象的格式字符向量生成脚本流函数。使用UI选项(或generatehdl属性),您可以将定制的格式字符向量传递给脚本生成器。其中一些格式字符向量接受参数,如顶级实体或模块名。

你可以使用valid流格式化字符。例如,' \ n '在脚本文件中插入换行符。

自定义编译和模拟脚本

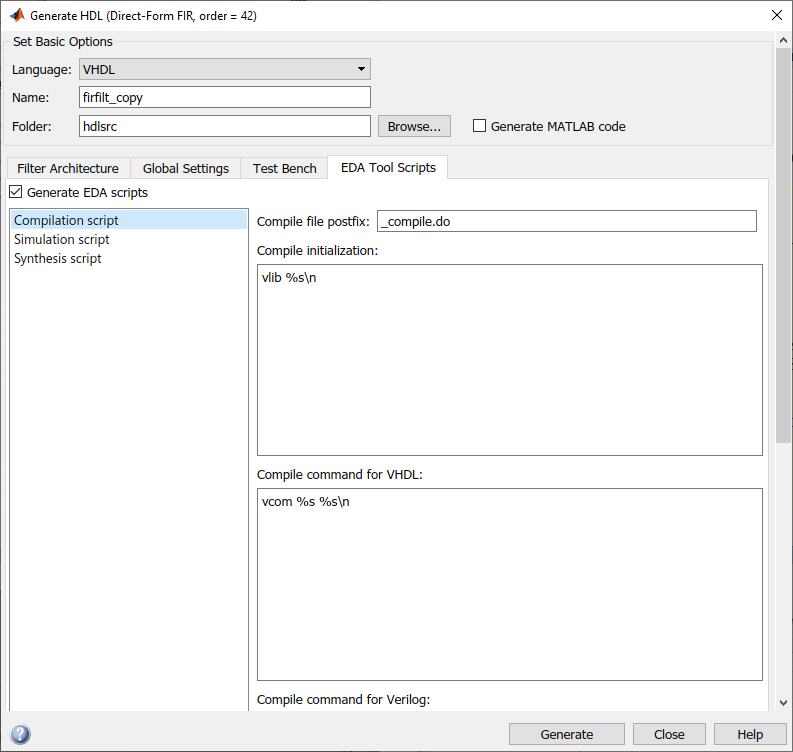

中查看和设置选项EDA工具脚本对话框:

打开Generate HDL对话框。

单击EDA工具脚本选项卡。

的编译脚本选项组被选中,如图所示。

的生成EDA脚本选项控制脚本文件的生成。默认情况下,选择此选项,如上图所示。

如果要禁用脚本生成,请清除此复选框。

对话框左侧的列表允许您从几个类别中进行选择。选择一个类别并根据需要设置选项。类别:

编译脚本:自定义脚本,用于编译生成的VHDL或Verilog代码。看到编译脚本选项.

仿真脚本:为HDL模拟器定制脚本。看到仿真脚本选项.

合成的脚本:为合成工具定制脚本。看到第三方合成工具的自动化脚本.

每个部分的自定义字符向量被传递给

流编写所选脚本的每个部分。控件支持的格式字符向量金宝app流函数。一些字符向量包含隐式参数。选项 隐式参数 编译初始化 库名称 为VHDL编译命令和Verilog的编译命令 的内容模拟器的旗帜选项(空字符向量,

''默认情况下)当前模块的文件名

编译终止 没有隐式参数 编译初始化 没有隐式参数 仿真命令 库名称

顶级模块或实体名称

仿真终止 没有隐式参数

编译脚本选项

图中显示了编译脚本窗格中,选项设置为默认值。

编码器生成一个名为firfilt_copy_compile.do:

Vlib工作vcom firfilt_copy.vhd

firfilt_copy_tb_compile.do

Vlib工作vcom firfilt_copy.vhdvcom firfilt_copy_tb.vhd

为编译脚本设置模拟器标志。您可以选择在生成的编译脚本中插入模拟器标志。这个选项包含在独立过滤器和测试台的编译脚本中。例如,您可以指定编译器版本。指定标志:

点击试验台在“生成HDL”对话框中。

属性中输入感兴趣的标志模拟器的旗帜字段。在图中,对话框指定导师图形ModelSim模拟器使用

-93年编译器选项。

选择命令行:属性指定模拟器标志SimulatorFlags财产的generatehdl函数。

仿真脚本选项

当您生成一个测试台时,编码器会生成一个模拟脚本。图中显示了仿真脚本窗格中,选项设置为默认值。

编码器生成一个名为firfilt_copy_tb_sim.do:

vsim -voptargs=+acc工作。firfilt_copy_tb添加波sim: / firfilt_copy_tb / u_firfilt_copy / clk添加波sim: / firfilt_copy_tb / u_firfilt_copy / clk_enable添加波sim: / firfilt_copy_tb / u_firfilt_copy /复位加波sim: / firfilt_copy_tb / u_firfilt_copy / filter_in添加波sim: / firfilt_copy_tb / u_firfilt_copy / filter_out添加波sim: / firfilt_copy_tb filter_out_ref——运行

合成脚本选项

有关合成脚本选项的信息,请参见第三方合成工具的自动化脚本.