如何使用5G工具箱生成一个用于SystemVerilog验证的5G波形

杰克·埃里克森MathWorks

RTL验证的挑战之一是开发现实的直接测试。像3GPP 5G新无线电(NR)标准这样的新标准需要深入的领域专业知识,这使得创建符合标准的波形验证模型更具挑战性。

5G Toolbox™为5G通信系统的建模、仿真和验证提供了符合标准的功能和示例,以确保其符合5G NR标准。本视频展示了如何使用HDL Verifier™从一个5G工具箱功能自动生成SystemVerilog验证组件,该组件通过在SystemVerilog中调整参数合成一个真实的波形,以及在此过程中您将经历的一些更常见的步骤,包括:

- 分区MATLAB®从算法和测试台架上定义什么是可参数化的

- MATLAB函数输出转换成固定点

- 解决阻止C代码生成的编码风格问题

- 将生成的SystemVerilog DPI组件集成到一个简单的测试平台中

如果您正在为5G无线应用程序设计硬件,您需要验证硬件的功能是否符合标准。如何创建符合标准的波形,更好的是,如何使用参数创建波形以测试不同的场景?

MATLAB与5G工具箱提供了符合标准的功能和示例,用于建模、仿真和验证5G通信系统,以确保它们符合3GPP 5G新无线电(NR)标准。

在这里,我将展示如何重用什么通讯科算法工程师开发产生的SystemVerilog验证一个5G创新无线电波形。它需要多长时间来学习5G规范和代码了波形SystemVerilog的?

5G工具箱有一些波形产生的好例子,你可以使用开始,就像这里。但在算法开发过程中,测试和算法往往没有相互区分。

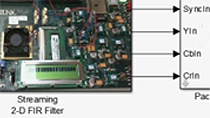

无线HDL工具箱包含5G的硬件设计IP,与使用5G工具箱功能,并已构建了这一点,像NR HDL小区搜索基准测试平台。此最强的小区ID,这意味着它的设计的搜索执行OFDM解调并识别最强的主和副同步信号。

波形生成的大部分是在这个函数中,从而产生的块模式的情况下B.试验台在频率偏移增加和噪音,使之更具代表性你会接收什么在空中完成的。I’m going to put that functionality into the main function and pass these parameters as inputs, so when I use the component in SystemVerilog I can use the same stimulus and sweep the parameters for signal-to-noise ratio, frequency offset, and set a different cell ID. This is hard-coded for case B, I could parameterize that too—but I’m keeping this simple for now.

这里的主要功能,在这里我添加了频率偏移和噪声的结束。我做的另一件事是将其转换为固定点。在MATLAB的默认类型是双精度浮点,但RTL设计的投入是固定的点。

HDL验证器是产生此组件的产品。它调用MATLAB Coder来生成C代码,并构建一切来将其链接到SystemVerilog仿真中。所以它会在任何SystemVerilog模拟器中本机运行。

命令是dpigen,我需要为输入参数定义数据类型—它可以计算出驱动这些参数的代码的输出。

但是,当我开始运行这个命令,我得到了一些错误。MATLAB是一种解释语言,漂亮的数据类型的原谅,所以我不得不做出对C代码生成一些修正,例如,如果一个变量将被分配复杂的数据,复杂的数据进行初始化。和C代码生成不允许你的元素,你开始从中读取后添加到一个结构,所以有这几个补丁。但总体而言,这些修改是相当小的。

现在我可以生成组件,并看看有什么被创建。它生成所有必要构建功能,来构建它的生成文件的C代码,并建立了DLL。如果您需要编译在不同的平台上,你可以使用Makefile。它还生成一些SystemVerilog代码来演示如何使用组件。

它需要初始化句柄,它有重置行为,当启用时,它调用函数的每一个边缘的时钟。在这种情况下,请注意这个函数输出整个波形——这就是MATLAB代码通常的工作方式——但这意味着我可能不想一遍又一遍地调用它,我只调用它一次,然后禁用它。

我都创建了一个简单的测试平台,没有什么花哨这里。它只是实例化的RTL设计,而这又是从无线HDL工具箱IP生成。然后,我在这里只是实例化产生的SystemVerilog DPI。这是一个非常简单的测试平台,它只是做了复位,设置一些参数为DUT,然后载荷波形。下面是一个电话后它禁用DPI。然后,它遍历并拿出样品,在从全波形的时间。

您也可以在MATLAB和C代码动态生成的样本,如果你想使用较少的内存,并确定与稍微更长的运行时间。

我已经编制的DUT,这是我的小测试平台的DO文件。这里的关键是,我还需要一定要编译生成的SystemVerilog和链接DLL启动模拟器的时候。

这需要一段时间来模拟,所以我会跳过这一波。输入信号是在这里,波形参数和数据本身。在本设计中的硬件被称为两遍,我只是跑第一关,这是寻找PSS检测。这reportValid表示如果检测出PSS相关,如果我在其中的一个放大,有相关结果,它清除了门槛,这是PSS0。

您还可以从MATLAB或Simulink生成一个检查组件,甚至可以从Simulink生成UVM。金宝app但这里我只想关注波形。

总的来说,这花费了一两个小时的时间,如果我与MATLAB代码的开发人员合作,可能会更快。但这是一种非常快速和有效的方法,可以生成可参数化的SystemVerilog组件来生成5G新的符合无线电标准的波形,以验证您的5G硬件设计。

您也可以从以下列表中选择一个网站:

如何获得最佳的网站性能

选择最佳的网站性能的中国网站(在中国或英文)。其他MathWorks的国家网站都没有从您的位置访问进行了优化。