基于fpga的单脉冲技术:算法设计

这个例子展示了开发单脉冲技术的工作流程的前半部分,其中使用数字下转换(DDC)对信号进行下转换。本例中的模型适合在FPGA上实现。本例主要介绍了利用单脉冲技术估算目标方位和仰角的设计。

这个例子的第二部分,基于fpga的单脉冲技术:代码生成,展示了如何从实现模型生成HDL代码,并验证生成的HDL代码与行为模型相比产生了正确的结果。整个算法采用定点数据类型设计。

该示例展示了如何使用相控阵系统工具箱™、DSP HDL工具箱™和定点设计器™在Simulink®中设计一个fpga就绪的单脉冲技术来匹配相应的行为模型。金宝app为了验证实现模型,该示例将实现模型的仿真输出与行为模型的输出进行了比较。

相控阵系统工具箱为单脉冲技术提供了浮点行为模型分阶段。MonopulseFeed系统对象™。DSP HDL工具箱提供了下转换滤波所必需的FIR滤波器。

定点设计器提供了用于开发定点和单精度算法的数据类型和工具,以优化嵌入式硬件的性能。位真模拟可以观察有限的范围和精度的影响,而无需在硬件上实现设计。

单脉冲是一种利用天线不同元件接收到的回波来估计信号到达方向(DOA)的技术。这个方向有助于估计物体的位置。本例使用DSP HDL工具箱和定点设计器进行算法设计。该技术使用四束光束来测量目标的角位置。所有四束同时产生,方位角和仰角的差异是在一个脉冲中实现的,因此称为单脉冲。

子系统设计

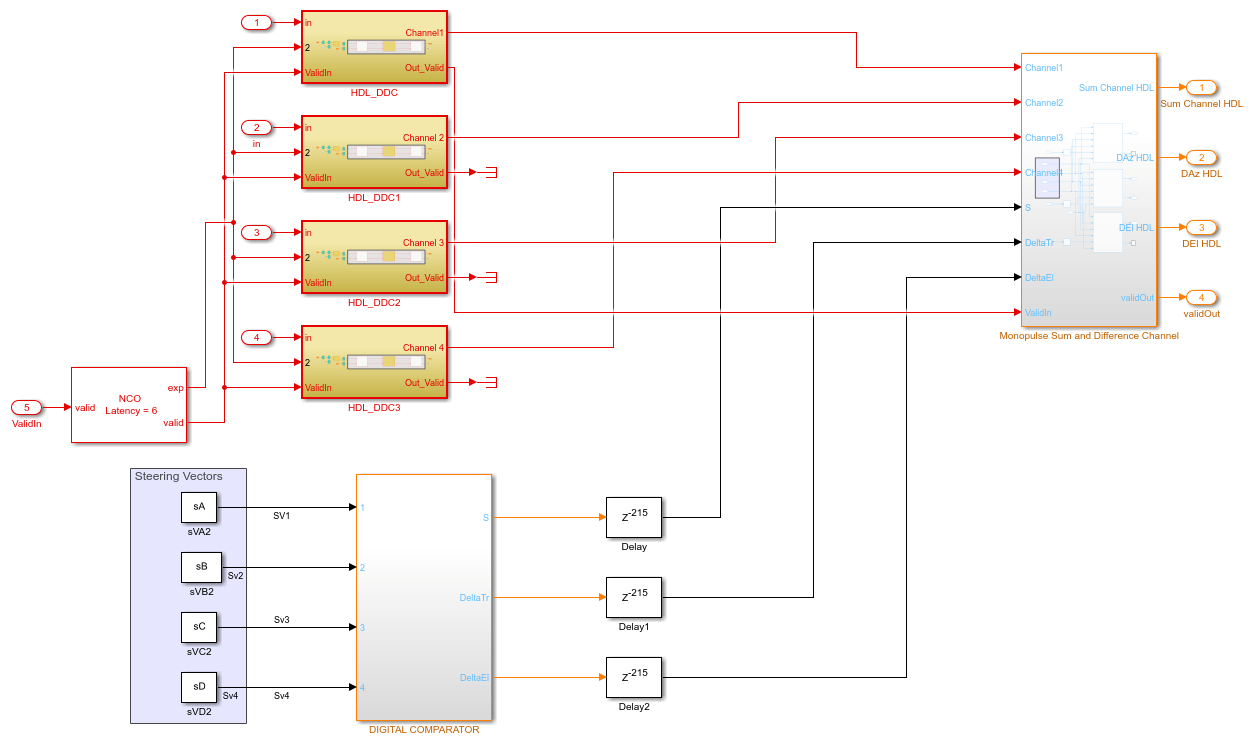

该算法通过使用支持HDL代码生成的Simulink®块实现。金宝app金宝app该模型假设信号来自4元均匀矩形阵列(URA),因此,该模型有4个正弦信号作为输入。假设市建局有4个要素,该模型由来自市建局每个要素的4个接收通道组成。一旦信号转换到数字域,DDC块确保接收信号的频率降低,以减少处理的采样率。该框图展示了子系统,子系统由以下模块组成。

多路输入信号

数字下变频

单脉冲和与差通道

modelname =“金宝appSimulinkDDCMonopulseHDLWorkflowExample”;open_system (modelname);确保模型是可见的,没有被范围阻碍。。集(allchild (0)“可见”,“关闭”);

Simu金宝applink模型有两个分支。顶部分支是单脉冲技术和数字下转换算法的行为浮点模型,底部分支是使用支持HDL代码生成的块的功能等效的定点版本。金宝app除了绘制两个分支的输出以比较两者之外,还计算并绘制了两个输出的和通道之间的差值或误差。

行为模型的输出有延迟( )块。这个延迟是需要的,因为实现算法使用220个延迟来启用管道,这会产生需要考虑的延迟。这种延迟对于行为模型和实现模型之间的输出时间对齐是必要的。

)块。这个延迟是需要的,因为实现算法使用220个延迟来启用管道,这会产生需要考虑的延迟。这种延迟对于行为模型和实现模型之间的输出时间对齐是必要的。

数字下变频(DDC)

的DDC和单脉冲HDL子系统展示了在80 MHz和近15 MHz载波频率采样的接收信号如何通过DDC下转换到基带,然后传递到单脉冲和差分子系统。DDC模块是一个数控振荡器(NCO)和一组低通滤波器的组合。NCO块提供混合和解调传入信号的信号。

open_system ([modelname/DDC和单脉冲HDL]);

实现子系统中控制向量的和和差输出的215毫秒的延迟补偿了下转换链的延迟。

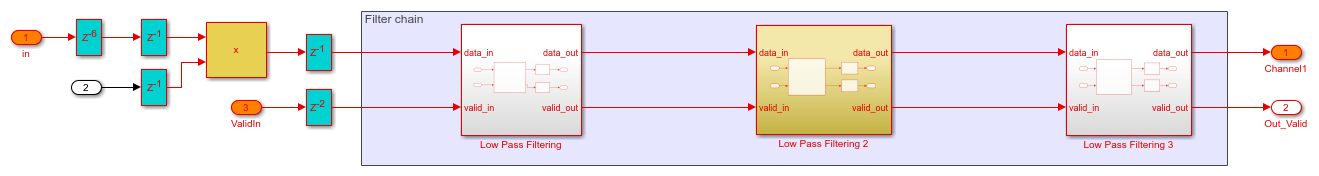

DDC还包含一组低通滤波器,如图所示。一旦混合,需要对混合信号进行低通滤波以消除高频成分。本例使用级联过滤器链进行低通过滤。NCO为混合器产生高精度正弦信号。NCO块有6个周期的延迟。该信号与输入信号混合,并在通过滤波阶段时从较高的频率转换为相对较低的频率。

open_system ([modelname'/DDC和单脉冲HDL/HDL_DDC']);

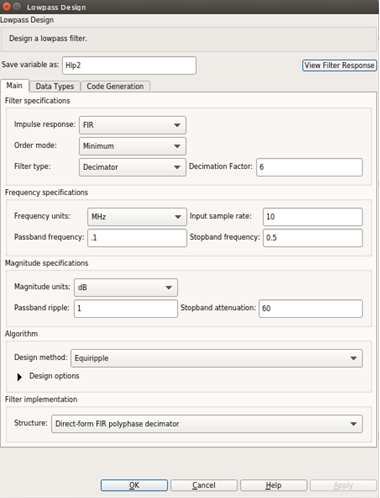

在本例中,输入信号的载波频率为15 MHz,采样频率为80 MHz。下转换过程将采样信号降低到几千赫。设计了低通FIR滤波器的系数filterBuilder.必须选择系数值以满足所需的通带标准。

一旦生成,这些系数将用于配置FIR Filter块。

单脉冲和与差通道

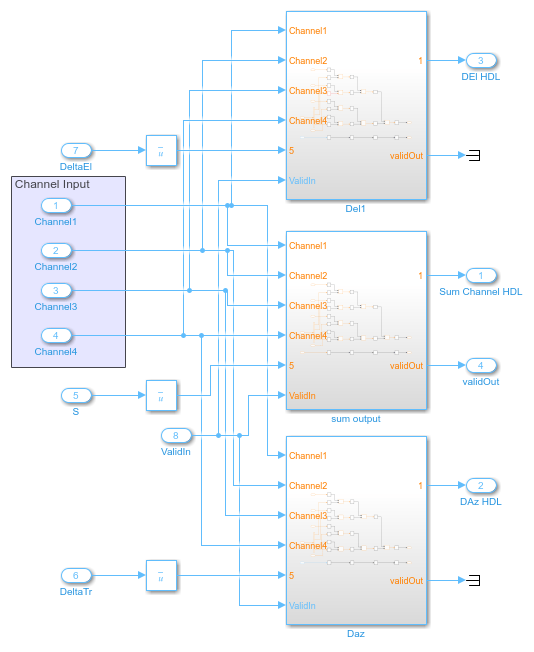

单脉冲算法还必须为不同的元素生成一个转向向量。方向矢量已经生成,入射角为方位角30度,仰角为20度。转向矢量被传递给数字比较器,以提供所需的和和和差通道输出。然后将下转换信号乘以这些向量的共轭,如图所示。通过对和信道和差分信道的处理,可以得到接收信号的DOA。显示了用于比较天线阵列不同元素的转向矢量的数字比较器。

open_system ([modelname/DDC和单脉冲HDL/数字比较器]);

图中,数字比较器取转向矢量,分别计算不同转向矢量sVA、sVB、sVC和sVD的和和和差。你也可以计算转向向量使用分阶段。SteeringVector方法中所示的方法也可以生成Simulink中基于fpga的波束形成算法设计金宝app.一旦完成了阵列各元素对应的各个转向矢量的和和差,就进行了相应方位角和仰角的和差通道的计算。从和差单脉冲子系统得到3个信号,分别是和、方位差和高程差。整个算术是在定点数据类型中执行的。使用此命令打开单脉冲和差通道子系统。

open_system ([modelname/DDC和单脉冲HDL/单脉冲和差通道]);

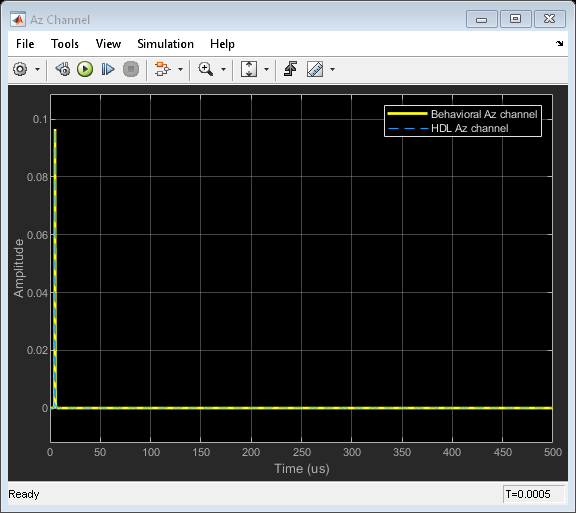

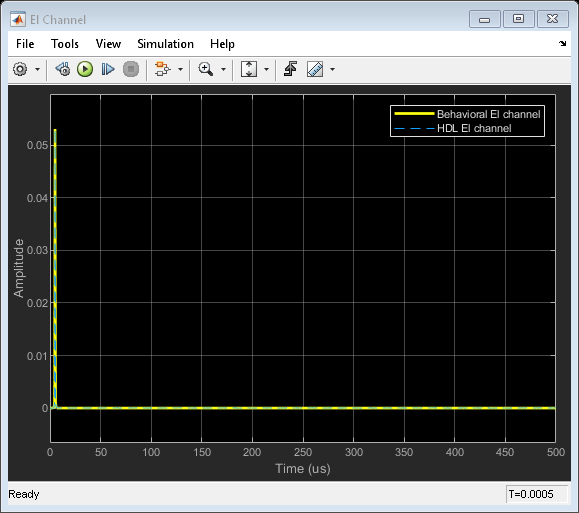

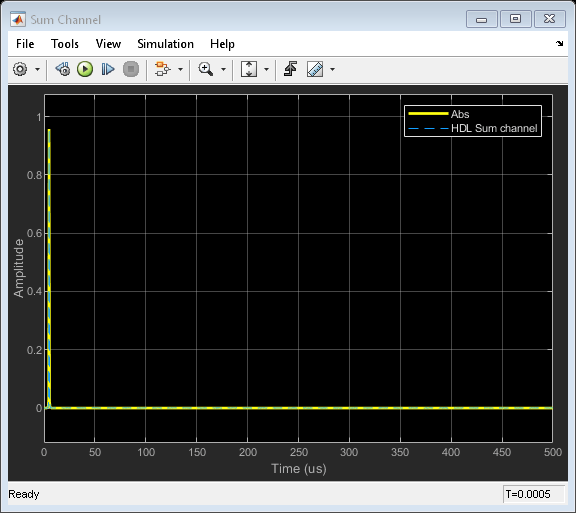

实施模型与行为模型的结果比较

要比较实现模型和行为模型的结果,请运行为显示结果而创建的模型。您可以通过单击Play按钮或在M金宝appATLAB®命令行上调用sim命令来运行Simulink模型。使用范围块来比较输出帧。

sim (modelname);

图中显示了和和和差通道的输出。这些通道可以被馈送到估计器,以指示物体的角度/方向。

总结

本例演示了如何设计一个fpga就绪算法,自动生成HDL代码,并在Simulink中验证HDL代码。金宝app举例说明了DDC和单脉冲馈电系统的Simulink模型设计,并以相控阵系统工具箱金宝app中的等效行为模型作为黄金参考对结果进行了验证。除了行为模型之外,该示例还演示了如何使用支持HDL代码生成的Simulink块创建用于实现的子系统。金宝app金宝app并将实现模型的输出与相应行为模型的输出进行比较,验证两种算法在功能上是等价的。

一旦实现算法在功能上被验证为等效的黄金参考,HDL Coder™可以用于Simulink对HDL代码的生成,HDL Verifier™可以用于金宝app生成一个共同仿真模型(高密度脂蛋白编码器)试验台。

这个由两部分组成的系列的第2部分展示了如何从实现模型生成HDL代码,并验证生成的HDL代码产生的结果与浮点行为模型和定点实现模型相同。