为QAM收发器模型建立HDL测试平台

这个例子展示了如何使用SystemVerilog DPI-C组件生成来构建一个行为测试工作台。该测试台用于验证一台64-QAM发射机和接收机的可合成的HDL代码。

需求和先决条件

下载188bet金宝搏本例所需的产品:

MATLAB®

金宝app仿真软件®

金宝app仿真软件编码器®

其中一个支持的HDL模金宝app拟器:Cadence®Incisive®,或Mentor Graphics®ModelSim®/QuestaSim®

支持的C编译器之一:M金宝appicrosoft®Visual Studio™for Windows,或GNU GCC for Linux®

概述

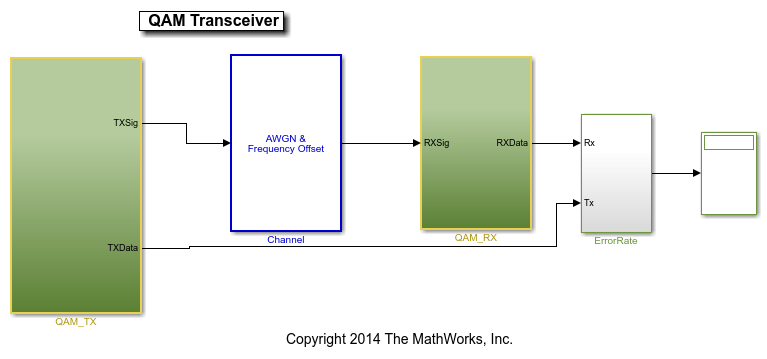

QAM接收方模型的顶层结构如下图所示。对QAM Tx HDL和QAM Rx HDL子系统进行了优化,用于生成HDL代码。使用HDL编码器,我们可以从这两个子系统生成HDL代码。这个示例附带生成的HDL代码,因此您不必为这个练习生成代码。

建立代码生成模型

要在HDL中构建一个完整的行为测试平台,我们需要通道子系统和出错率子系统的行为模型。利用这些模型,我们可以为这两个子系统生成SystemVerilog DPI-C组件。在生成DPI-C组件之前,我们需要首先设置代码生成选项。

从svdp金宝appi_qam模型中打开Simulink模型配置参数面板。设置以下参数:

选择代码生成->系统目标文件。单击Browse按钮并选择“systemverilog_dpi_gr .tlc”。

如果你有嵌入式编码器,你可以选择'systemverilog_dpi_ert'目标文件。

在“工具链”设置中,如果您使用的是Windows,请选择Visual Studio版本之一;如果您使用的是Linux,请选择GCC工具链之一。

接下来,通过在MATLAB中执行以下两个命令,导出DPI-C组件:

> > rtwbuild (svdpi_qam /频道)

> > rtwbuild (“svdpi_qam / ErrorRate”)

运行生成的测试平台

对于Mentor Graphics ModelSim/QuestaSim,

在GUI模式下启动ModelSim/QuestaSim。

将当前目录更改为当前MATLAB目录

输入以下命令开始模拟:

做QAM_DPIC_tb_mq.do

节奏的:

启动终端shell。

将当前目录更改为当前MATLAB目录。

在shell中输入以下命令。

sh QAM_DPIC_tb_incisive.sh

仿真结束时,错误率打印如下:

*************模拟摘要********************

误码率:0.001356

错误数:4.000000

接收比特数:2950.000000

*******************************************************