生成来自Simulink的本机SystemVerilog断言金宝app

这个例子显示了如何从一个模型的Simulink断言本地SystemVerilog声明。金宝app只要在Simulink和HDL测试环境中需要相同的断言行为,此功能都很有用。金宝app

要求和先决条件

下载188bet金宝搏此示例所需的产品:

MATLAB®.

金宝appSimulink®

金宝appSimulink Coder™

MentorGraphics®SexchingIm®/Questasim®或支持的金宝appSystemVerilog模拟器

支持的C编译器之一:M金宝appicrosoft®VisualC++或GNU GCC

概要

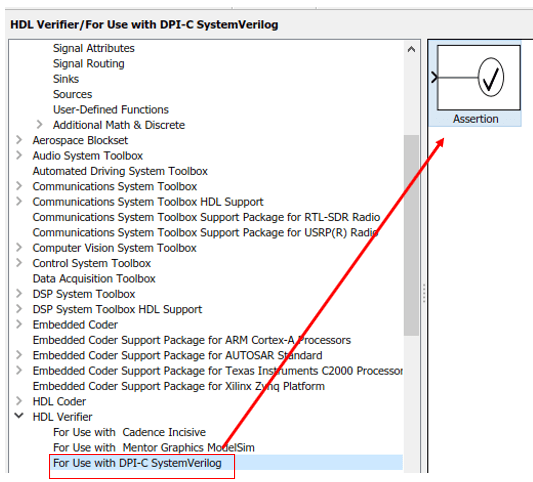

要生成包含SystemVerilog断言的DPI-C组件,Simulink模型必须使用金宝appDPI-C断言块。找到这个街区HDL验证者- >与DPI-C SystemVerilog一起使用图书馆如下所示:

此块可以像泛型一样使用断言块在模型验证图书馆。模拟行为与Simulink断言块相同,但在DPI-C组件期间,块为每个生成块生成本机Sy金宝appstemVerilog断言DPI-C断言块存在于模型中。

设置示例

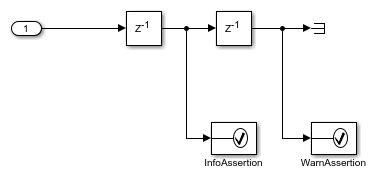

此示例中的模型包含两个DPI-C块断言。其中一个用于使用自定义选项提供延迟的信息,第二个块被设置为在第二次延迟结束时提供警告。

运行以下代码以打开设计。

Open_System('svdpi_assertion');

为代码生成设置模型

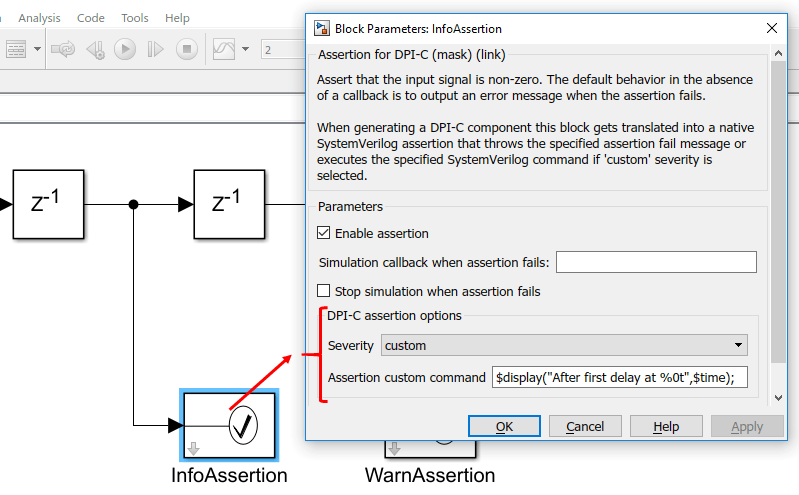

该模型用DPI-C系统目标文件(SystemVerILog_dpi_grt.tlc)预先配置。在生成DPI-C组件之前,请务必通过块掩码在SystemVerilog中配置所需的断言行为。

默认情况下,断言块将生成SystemVerilog错误($错误(“”))触发时的空消息。这可以通过提供错误消息来更改,将错误更改为警告($警告(“”))带有警告消息,或提供自己的自定义SystemVerilog命令。

下图显示了第一个延迟后断言块的SystemVerilog行为配置。在外面的参数DPI-C断言选项小组仅影响Simulink仿真行为。金宝app

请注意断言自定义命令是一个有效的systemverilog语句。

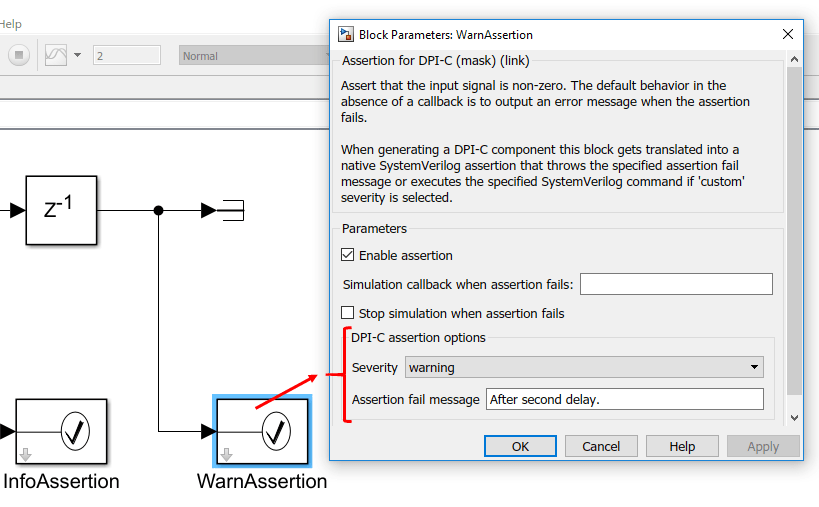

第二个断言块配置为输出具有指定消息的警告,如下所示。

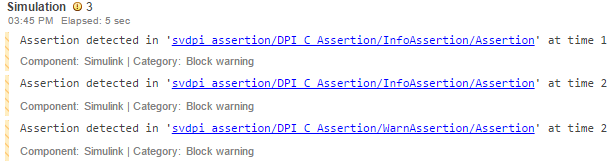

如果我们运行模型,我们可以看到Simulink中触发了两个断言警告:金宝app

生成SystemVerilog DPI-C组件

当svdpi_assertion.模型,右键单击dpi_c_assertion.块,选择C / C ++代码 - >构建此子系统。

单击出现的对话框中的“版本”。

该构建为此生成C代码dpi_c_assertion.子系统和系统的Verilog DPI-C包装和打包文件命名

“dpi_c_assertion_build / dpi_c_assertion_dpi.sv”和“dpi_c_assertion_build / dpi_c_assertion_dpi_pkg.sv”。

或者,您可以通过执行来生成组件:

SLBUILD('svdpi_assertion / dpi_c_assertion');

在HDL模拟器中运行生成的测试台

对于此示例,将使用ModelSSIM / Questasim Simulator。要获取有关如何运行TestBench的详细说明,请参阅“使用SystemVerilog DPI组件生成”。

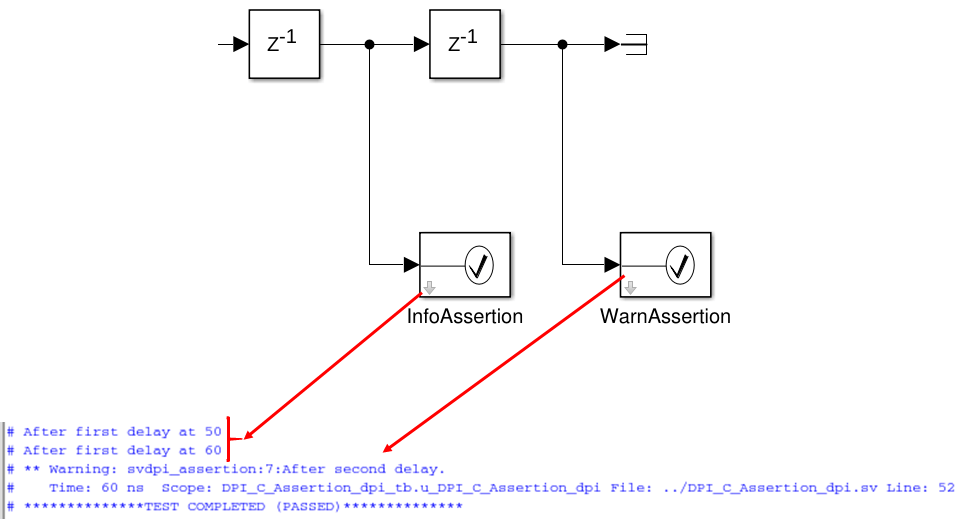

运行testbench后,请注意DPI-C组件抛出的消息和警告。

跟踪SystemVerilog断言回到Simulink金宝app

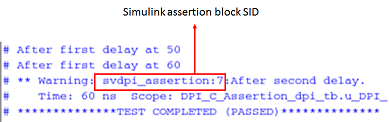

如果要追踪生成警告的断言,则需要从警告消息中查找Simulink标识符(SID),如下所示:金宝app

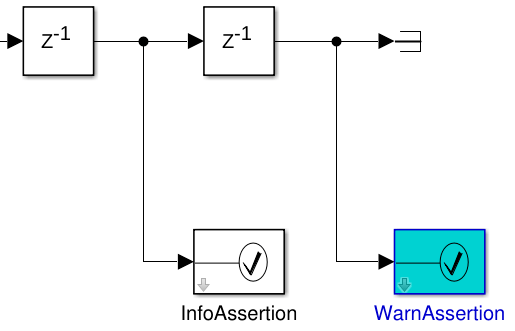

一旦找到断言块的SID,您可以使用Simulink Programmatic API来突出显示相应的块。金宝app执行:

金宝appsimulink.id.hilite('svdpi_assertion:7');

这将突出显示相关块。

过滤HDL模拟器中的断言

如果要在HDL模拟器中过滤断言,则需要提供要过滤为HDL模拟器的PLUERGS参数的块的SID。

例如,“Infoassertion”断言块的SID是“SVDPI_ASSERTION:6”。因此,为了过滤此块给出的信息,我们需要将参数“+ svdpi_assertion:6”提供给HDL模拟器。在ModelsIm / Questasim中,模拟命令是:

VSIM-C-voptargs = + acc-sv_lib.../dpi_c_assertion.work.dpi_c_assertion_dpi_tb.+ svdpi_assertion:6