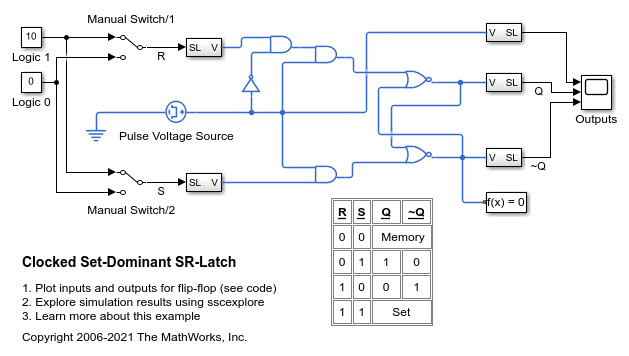

时钟设置为主的SR锁定

此示例显示了如何从SIMSCAPE™Electrical™逻辑组件中建模设定的SR-LATCH。初始条件通过交换机的初始化命令传递给相关和门。

模型

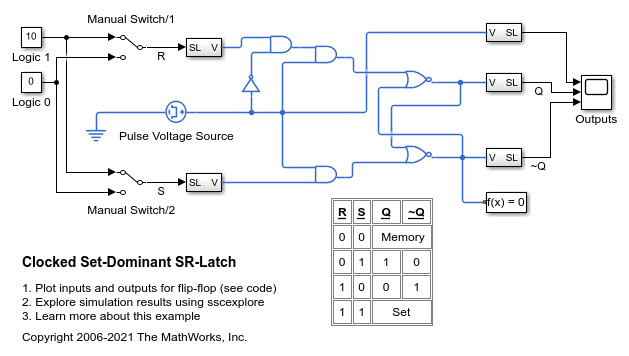

SIMSCAPE日志记录的仿真结果

下面的图显示了设定主导SR-latch的输入和输出。SR-LATCH的两个输入均设置高,因此其输出状态为Q较高,而对于〜Q则低。

此示例显示了如何从SIMSCAPE™Electrical™逻辑组件中建模设定的SR-LATCH。初始条件通过交换机的初始化命令传递给相关和门。

下面的图显示了设定主导SR-latch的输入和输出。SR-LATCH的两个输入均设置高,因此其输出状态为Q较高,而对于〜Q则低。