在多核处理器和FPGA上实现一个FFT

这个示例向您展示了如何通过图形化划分模型来利用具有FPGA加速的多核处理器目标。这个例子需要Simulink Coder™生金宝app成多线程代码和HDL Coder™生成HDL代码。您不能在Macintosh系统上生成HDL代码。

介绍

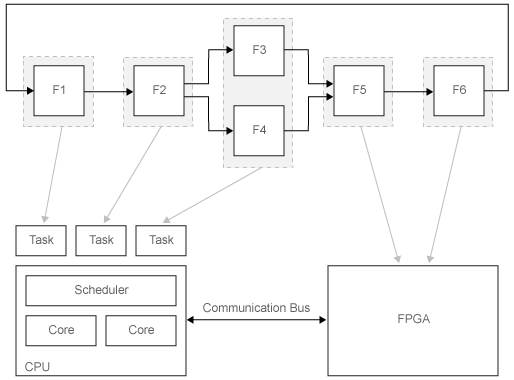

一些现代处理器包括与FPGA组件集成的多核处理器,以创建高性能应用程序。这需要多核和FPGA编程,包括并行线程的编程、HDL和系统内核之间的通信接口。金宝appSimulink™允许您通过图形化划分算法,并将从这些分区生成的软件分配给处理器上的线程和FPGA上的模块,从而利用这些方法。该示例使用一个应用程序级模型生成一个可执行文件,由多个线程和HDL代码组成,以利用FPGA的硬件并行性。如下图所示。

示例模型

加载示例模型:

slexMulticoreFPGAExample

架构定义

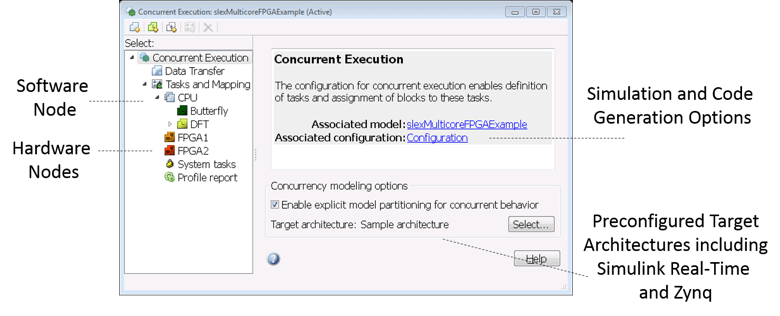

此模型的所有并发执行设置都可以在并发执行对话框(配置参数>求解器>配置任务)中访问。

实现算法的第一步是定义目标体系结构的结构元素。这包括硬件的结构元素,例如处理节点(CPU、FPGA)的数量和类型以及通信通道(AXI、PCI)。

这也包括模型配置参数中的软件设置(如系统目标文件,硬件实现,数据传输设置)。在本例中,我们选择了预先配置的目标体系结构“示例体系结构”。该体系结构使用桌面作为部署过程的替身。

划分和映射模型

对模型进行分区,以决定哪些函数顺序运行,哪些函数并发运行。

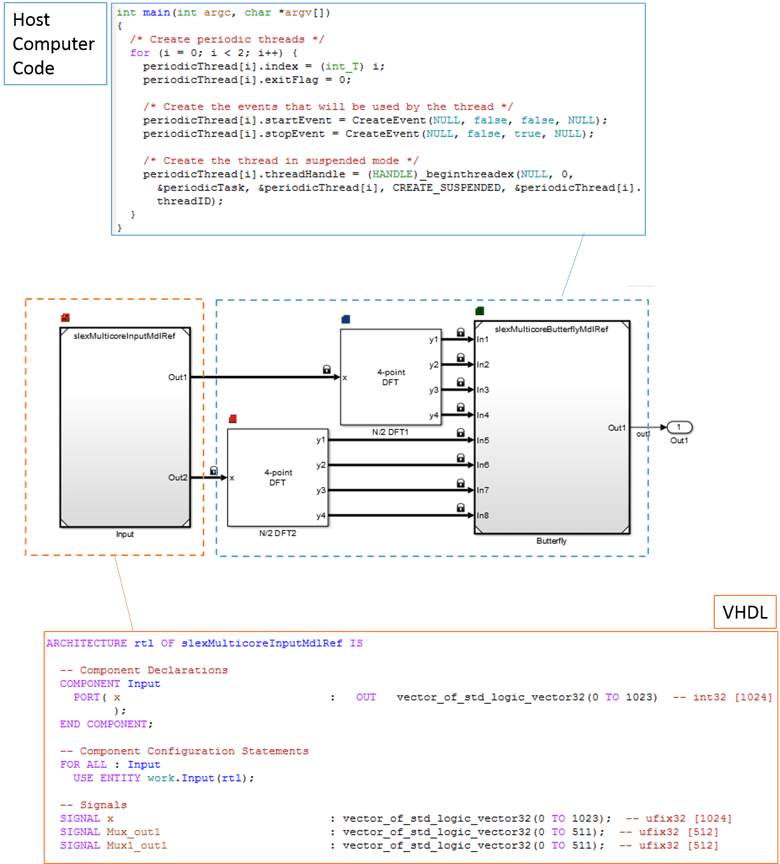

实例模型由MATLAB系统模块、模型模块、原子子系统和输出模块组成。显式分区在模型的根级基于这些块创建分区。而隐式分区则根据块样本时间和其他调度约束创建分区。

在对模型进行分区之后,您可以将分区映射到CPU任务和FPGA节点。您可以通过GUI或API更改设计空间探索的映射。在映射过程中,信号将自动映射到通道。

您可以在“并发执行”对话框中更改块映射到线程和FPGA的方式。有关详细信息,请参见在多核目标上优化和部署.

生成多线程和HDL代码

双击'Generate Code and Profile Report'按钮来生成多线程代码。在本例中,主机代替目标环境。C代码为映射到处理器任务的块生成。这段代码是使用桌面计算机本地的线程组织的。代码片段显示了如何创建线程。此外,为映射到硬件节点的块生成HDL代码。下面的代码片段说明了如何用VHDL创建模块/实体。

close_system (“slexMulticoreFPGAExample”, 0);