对比与外部内存有限的自适应直方图均衡化

这个例子展示了如何实现contrast-limited自适应直方图均衡化(CLAHE)算法的FPGA,包括外部存储器接口。

金宝app支持的硬件

Xilinx®Zynq®ZC706评估装备+ FMC-HDMI-CAM夹层卡

介绍

视频处理算法通常一个完整的帧的视频数据存储在内存中。实现这种存储在一个FPGA BRAM利用率和增加会导致输入视频分辨率的限制。这个例子展示了如何在fpga上实现视觉算法通过使用外部内存资源减少使用布拉姆和使处理高分辨率的视频输入。

这个示例使用的外部存储器接口AXI4协议和验证设计对内存争用。AXI4随机存取接口提供了一个简单,直接接口互连的内存。这个协议使算法作为记忆大师提供的地址和管理直接破裂转移。AXI4主写控制器和AXI4主读控制器模块在本例模型简化AXI-4界面模型™。金宝app当你生成使用高密度脂蛋白HDL代码编码器™产品,生成的代码包含一个完全兼容的AXI4接口IP。

模型外部存储器

您可以使用SoC Blockset™块和可视化工具的建模、模拟、分析硬件和软件体系结构对asic fpga和系统芯片(SoC)。这些功能可以帮助您使用内存模型,构建系统架构总线模型和界面模型和帮助你一起模拟架构算法。这个示例模型外部内存使用两个街区的SoC Blockset库:

内存通道:物体通过外部内存流数据。它的模型之间的数据传输通过共享内存读写掌握算法。下面的例子使用了AXI4随机接入信道类型。

内存控制器:大师之间的块断定,赋予他们独特的访问共享内存。它被配置为支持多种渠道与不同的仲裁协议。金宝app这一块也记录和显示内存性能数据。这个特性允许您分析和调试在仿真时系统的性能。

HDL实现

CLAHE算法有三个步骤:瓷砖,直方图均衡化和双线性插值。双线性插值一步使用像素强度从输入帧。存储的全部输入帧视频数据,直到双线性插值一步需要外部存储器。

图中显示的示例模型的顶层。HDMI Rx块处理视频输入并将其传递到CLAHEAlgorithm_fpga子系统。HDMI Rx块将原始视频数据转换为YCbCr 4:2:2像素流格式。一个像素的输出数据流适合硬件算法设计。HDMI Rx块也指导SoC建设者工具来生成所需的IP块接收视频数据从FMC-HDMI-CAM卡附加的硬件。

模型中,AXI4-Master写控制器和AXI4-Master读AXI4内存映射接口控制器模块模型。AXI4-Master写控制器块写输入帧到外部存储器,和AXI4-Master阅读控制器读取框架从外部内存块的双线性插值。阿喜读FIFO块将输出像素流发送到HDMI Tx块。HDMI Tx块转换一个像素流在YCbCr 4:2:2格式原始视频数据显示在模拟。这一块也指导SoC建设者工具生成的IP块传输视频数据回FMC-HDMI-CAM卡。显示的状态阿喜读FIFO和阿喜写FIFO模块设计硬件上运行时,四个调试信号从这些块连接到led在黑板上。

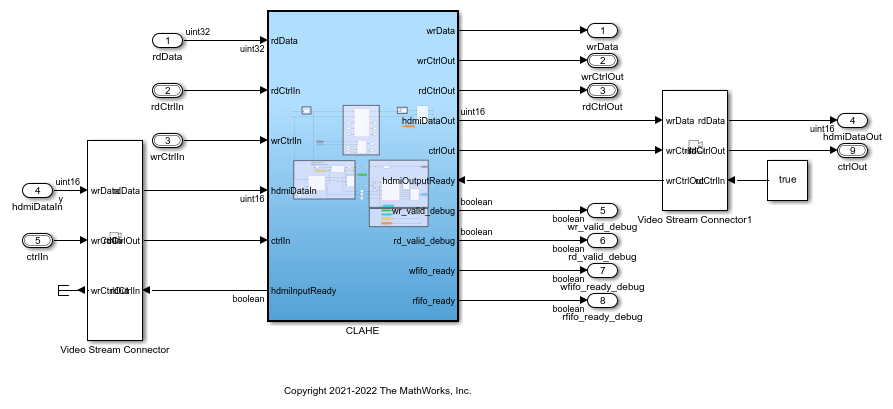

下一个图显示了CLAHEAlgorithm_fpga参考模型。输入像素流连接到一个视频连接板。这个街区提供了一个视频接口连接任意两个IPs的FPGA实现。在这个例子中,视频连接器阻塞连接HDMI输入和输出与FPGA的算法。

下一个图显示了CLAHEAlgorithm_fpga / CLAHE子系统,它实现了阿喜从外部存储器读写,和CLAHE算法。

子系统包含这些地区:* AXI写入内存:这部分输入数据到DDR写道。它由一个AXI4大师写控制器块接收输入视频控制信息从HDMI Rx块和模型AXI4为写数据到DDR内存映射接口。它生成五个信号:wr_addr,wr_len,wr_valid,rd_start,框架。的wr_valid信号输入到阿喜写FIFO块,存储传入的像素强度。SoC总线创造者块生成wrCtrlOut主,从总线写数据到DDR。每个破裂模型写一行数据。写完tileHeight(/ 2行tileHeight对应于每个瓷砖的高度CLAHE)模型断言rd_start信号开始读请求。的框架信号指示输入帧数。

阿喜从内存中读取:本节从DDR读取数据。它由一个AXI4-Master阅读控制器接收块

rd_start信号从AXI4-Master写控制器。块生成AXI4-Master阅读控制器rd_addr,rd_len,rd_avalid,rd_dready信号。SoC总线创造者块将这些信号组合成一辆公共汽车。块还生成AXI4-Master阅读控制器pixelcontrol总线对应rd_data。模型片32位rd_data信号获取8位(LSB)亮度组件,然后将其写入缓存的内存块CLAHE算法。

CLAHE:详细描述CLAHE算法硬件实现的,看到的对比有限的自适应直方图均衡化(视觉HDL工具箱)的例子。CLAHEHDLAlgorithm子系统作用于8位灰度图像,这就是为什么8位亮度(Y)组件是分开的16位YCbCr像素数据。

CLAHE CLAHEHDLAlgorithm子系统执行三个步骤:瓷砖,直方图均衡化和双线性插值。在第一步中,输入帧分为8-by-8网格的瓷砖。在第二步中,计算每个块的直方图,然后执行分配、再分配和运作进行计算。计算CDF值存储在缓冲区进行进一步处理。第三步计算输出像素强度通过使用双线性插值的提供值。输入帧的像素强度作为地址的缓冲区存储提供值。这些像素强度从外部读取内存存储原始输入帧。

因为从外部存储器读回的数据突发模态,它不能被直接使用双线性插值。缓存缓冲区存储从外部存储器读取的行。足够的深度缓存来存储的行数等于tileHeight。的rdValid从CLAHEHDLAlgorithm子系统生成的信号rd_addr信号从缓存中读取数据。数据从缓存读取(pixValue),然后返回CLAHEHDLAlgorithm子系统完成双线性插值计算输出像素强度。

硬件实现

的SoC建设者工具构建、加载并执行模型在FPGA板上。在这个例子中使用的硬件板Xilinx®Zynq®ZC706评估工具。建立、加载和执行硬件的设计,遵循这些步骤。

设置Vivado®工具合成,实现,和一代的FPGA比特流。

示例模型运行在

加速器默认模式加快仿真速度。然而,SoC建设者工具要求正常的模拟模式。在仿真金宝app软件配置参数,设置模拟模式来正常的。启动SoC建设者通过点击工具配置、构建和部署在仿真软件将来金宝app发布。

选择构建模型,然后回顾的内存映射检查内存映射窗格。

在选择项目文件夹窗格中,指定您的项目文件夹。在选择构建操作窗格中,选择构建、加载和运行。

在验证模型窗格中,单击验证检查兼容性模型实现的。然后单击构建开始建立模型。当FPGA合成启动时,外部壳打开。

当比特流生成完成,连接硬件窗格中,选择测试连接测试主机之间的连接和硬件。在硬件上点击加载比特流负载。

这个图显示了最终的SoC建设者完成这些步骤后的结果。

仿真和结果

这个例子使用一个输入的视频大小480 -,- 640像素。这个尺寸是HDMI Rx配置块。在Xilinx Zynq ZC706评估工具包,PL DDR控制器配置为一个64位AXI4-Slave接口运行在200 MHz。由此产生的带宽是1600 MB / s。这个例子中有两个AXI大师连接到DDR控制器。这些AXI大师DUT AXI4读写接口。每像素的YCbCr 4:2:2视频格式需要2字节。为DUT AXI4读写接口,每个像素在4个字节。在这种情况下,读和写接口的吞吐量要求2 * 4 * 480 * 640 * 60 = 147.456 MB / s。

这图显示了控制器性能的内存块。查看性能图,第一次打开内存控制器。然后,在性能选项卡上,单击查看性能的情节。选择所有大师下带宽,然后单击更新。DUT后开始编写和读取数据到外部存储器,吞吐量仍然约154 MB / s,这是内所需的吞吐量为147.456 MB / s。

示例中的信号模型在模拟记录。这些信号通过使用视图逻辑分析仪应用。这个数字显示输入和输出的记录数据帧。

这个图显示了模型的输入和输出帧。结果显示改进后的输出图像的对比。

引用

[1]Zuiderveld,卡雷尔。“对比度自适应直方图均衡化有限。”In Graphics Gems IV, edited by Paul S. Heckbert, 474-485. AP Professional, 1994.