通过FPGA中断触发软件任务

这个例子展示了如何建模一个划分硬件和软件的算法。硬件IP在FPGA结构中实现,触发在嵌入式处理器中实现的软件任务。在SoC硬件上设计、仿真并实现一个完整的设计。

金宝app支持硬件平台:

Xilinx®Zynq®ZC706评估试剂盒

Xilinx Zynq UltraScale™+ MPSoC ZCU102评估试剂盒

Xilinx Zynq UltraScale™+ RFSoC ZCU111评估试剂盒

Zynq-7000开发委员会

Altera®Cyclone®V SoC开发套件

Altera Arria®10 SoC开发套件

介绍

许多片上系统(SoC)应用程序需要硬件设备来触发处理器上的异步任务。当实现跨越硬件和软件的低延迟控制循环时,此功能非常有用。它在处理由软件发出的紧急硬件请求时也很有用。对于这种设计,硬件设备向中断控制器提出中断请求,以表示数据已准备好由处理器上的软件任务执行。

设计任务

此示例包括FPGA中的两个硬件IP核。这些IP核异步地产生中断信号。中断触发处理器上的两个独立任务,每个硬件IP核对应一个任务。处理器任务通过读或写寄存器来访问硬件设备。

模型结构

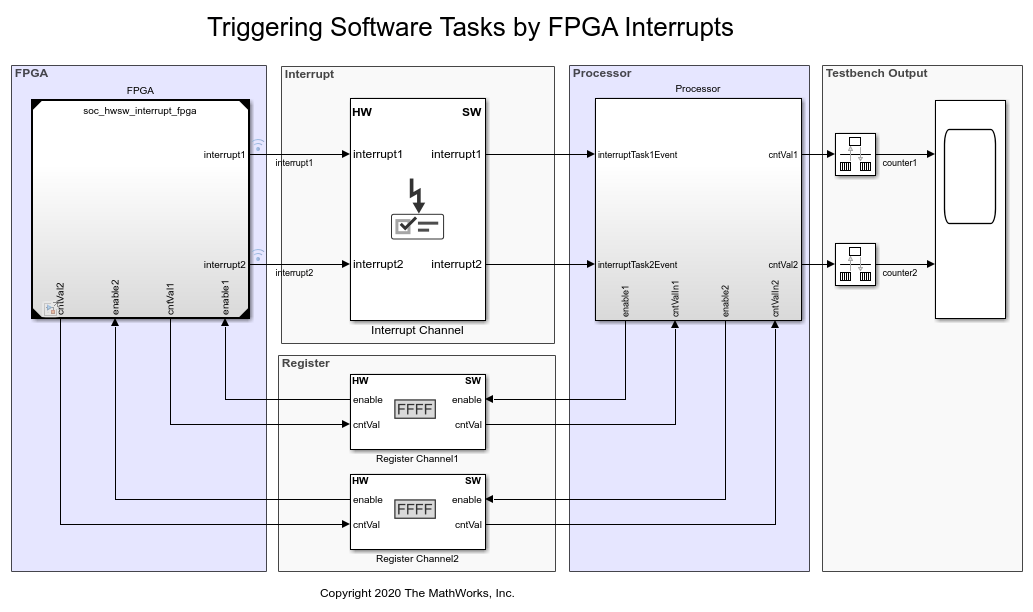

顶部模型sw_hw_interrupt_top包括FPGA模型sw_hw_interrupt_fpga和处理器模型sw_hw_interrupt_proc模型引用。顶部模型还包括中断通道和寄存器通道块,用于模拟从FPGA到处理器的数据传输。

FPGA模型实现了两个IP核,基于递增的32位计数器值生成中断。当计数器值的第16位或第18位从0变为1时,第一个IP核产生一个中断。当计数器值的第14位或第16位从0变为1时,第二个IP核产生一个中断。在产生中断时,计数器的值被注册并使用寄存器通道块转移到处理器。处理器模型实现两个软件任务,每个IP核一个,读取之前由FPGA注册的计数器值。

模拟

模拟系统0.03秒,并打开顶部模型上的Scope块以可视化处理器读取的计数器值。

下一个,模拟选项卡上,单击数据检查查看由中断触发的各种事件的时间。在顶部视图中增加interrupt1和interrupttas1信号,在底部视图中增加interrupt2和interrupttas2信号。仿真图显示,每当一个中断被触发时,相应的任务就被执行。在0.01802秒时,触发interrupt2,需要100微秒由Interrupt Channel块处理并触发相应的interruptTask2,后者需要500微秒运行。

在0.01966秒时,interrupt1和interrupt2同时被触发,处理器根据它们的相对优先级对它们进行服务。由于interrupt1首先在中断通道块的输入端口连接,所以它的优先级比interrupt2高。由于interrupt1的优先级更高,所以在intertask1仍在执行时,interruptTask2等待执行。

硬件实现和运行

这些产品是本下载188bet金宝搏节所要求的:

高密度脂蛋白编码器™

嵌入式编码器®

用于Xilinx设备的So金宝appC Blockset支持包,或用于Intel设备的SoC Blockset支持包

有关支持包的更多信息,请参见金宝appSoC Blockset支金宝app持的硬件.

为了在一个受支持的SoC板上实现该模型,使用金宝appSoC建设者工具。默认情况下,模型将在上面实现ZedBoard因为它配置了那个板。打开SoC建设者点击工具条中的“配置、构建和部署”按钮,并遵循以下步骤:

选择构建模型在设置屏幕上。点击下一个.

点击下一个在审查任务地图屏幕上。

在检查内存映射屏幕上,单击查看/编辑内存映射查看内存映射。点击下一个.

控件上指定项目文件夹选择项目文件夹屏幕上。点击下一个.

选择为外部模式构建、加载在选择构建操作屏幕上。点击下一个.

在验证模型屏幕上,单击验证检查实现模型的兼容性。点击下一个.

在构建模型屏幕上,单击构建开始构建模型。当FPGA合成开始时,一个外部外壳打开。点击下一个.

点击测试连接在连接硬件屏幕测试主机与SoC板的连通性。点击下一个去…运行应用程序屏幕上。

FPGA综合可能需要30分钟以上的时间。为了节省时间,你可以按照以下步骤使用预先生成的比特流:

关闭外壳以终止合成。

通过运行此命令将预生成的位流复制到项目文件夹

拷贝文件下面的命令点击加载并运行加载预生成的比特流并在SoC板上运行模型

拷贝文件(fullfile (matlabshared.sup金宝appportpkg.getSupportPackageRoot,“工具箱”,“soc”,...“金宝appsupportpackages”,“xilinxsoc”,“xilinxsocexamples”,“比特流”,...“soc_hwsw_interrupt_top-zedboard.bit”),”。/ soc_prj ');

加载比特流后,运行生成的软件模型soc_hwsw_interrupt_sw在外部模式。从模型工具栏中,打开数据检查并在顶部视图中添加interruptTask1,在底部视图中添加interruptTask2。观察每次触发中断时,相应的任务都会执行。

在其他委员会实施:要在除ZedBoard之外的其他受支持的单板上实现该模型,金宝app请先将模型配置为受支持的单板,然后设置示例参数如下。

在硬件选项卡上,单击硬件设置打开“配置参数”窗口。

在硬件实现选项卡,选择您的板硬件板在顶部和处理器模型上。

在目标硬件资源>FPGA设计(顶级)选项卡使包括MATLAB作为AXI主IP用于基于主机的交互并设置IP核时钟频率(MHz)10 MHz。

接下来,单击配置、构建和部署在工具条上打开SoC建设者并遵循上述ZedBoard的步骤。修改拷贝文件命令匹配与您的板对应的位流。在Altera Arria®10 SoC开发套件和Altera Cyclone®V SoC开发套件的情况下使用如下拷贝文件命令对应您的板。对于Altera Arria®10 SoC开发套件,复制'.periph。rbf’和‘.core。rbf的文件。

拷贝文件(fullfile (matlabshared.sup金宝appportpkg.getSupportPackageRoot,“工具箱”,“soc”,...“金宝appsupportpackages”,“intelsoc”,“intelsocexamples”,“比特流”,...“soc_hwsw_interrupt_top-c5soc.rbf”),”。/ soc_prj ');

以下是可用的预生成的位流文件:

“soc_hwsw_interrupt_top-zc706.bit”

“soc_hwsw_interrupt_top-zedboard.bit”

“soc_hwsw_interrupt_top-zcu102.bit”

“soc_hwsw_interrupt_top-XilinxZynqUltraScale_RFSoCZCU111EvaluationKit.bit”

“soc_hwsw_interrupt_top-c5soc.rbf”

“soc_hwsw_interrupt_top-a10soc.periph.rbf”

“soc_hwsw_interrupt_top-a10soc.core.rbf”

总之,这个示例展示了来自FPGA的中断如何在处理器中触发动作。您使用SoC Blockset对行为进行了建模,并经历了在SoC设备上实现它所需的工作流。