使用流量发生器分析内存带宽

本示例演示如何分析SoC应用程序的内存带宽。在内存密集型硬件设计中,可能有多个主服务器访问一个公共DDR内存。在这种情况下,分析所有内存master的动态需求对指导算法设计和部署硬件板需求非常重要。您可以使用内存流量生成器模拟内存流量,分析带宽使用情况并在硬件上进行验证。

金宝app支持的硬件平台

Xilinx®Zynq®ZC706评估试剂盒

Xilinx®Kintex®7 KC705开发板

设计任务

考虑一个在FPGA上实时输入和输出执行高清视频处理的应用程序。这个应用程序需要四个内存使用者同时争夺DDR访问。内存主机1将传入的视频帧写入内存,内存主机4将视频帧从内存中读取并连接到输出显示器。Memory master 2从内存中读取数据供FPGA处理,Memory master 3将数据写回内存。

每个master操作的HD视频具有以下特点:

帧尺寸:1920x1080p

像素大小:2字节(YCbCr格式)

帧周期:1/60 = 16.67ms(适用于60 FPS)

帧数据:1920x1080x2 = 4.1472MB

每个主机需要以下最低内存带宽来获得60帧/秒的帧速率。

内存带宽:帧数据/帧周期= 4.1472e6/16.67e-3 = 248.8MBps

假设内存控制器特性如下:

时钟频率:200mhz

数据宽度:32位

突发事务长度:128

使用SoC块集设计

使用以下命令创建模型内存控制器而且内存流量发生器块来建模四个内存主机。

内存控制器:设置内存控制器参数配置参数>硬件实现>目标硬件资源。下FPGA设计(mem控制器)选项卡,设置时钟频率为200mhz,数据宽度为32。下FPGA设计(调试)选项卡上,选择包括AXI互连监视器。

内存流量发生器1和4:Master 1和Master 4的内存流量特征是相同的,因为它们表示进出内存的视频帧流。master 1和master 4的内存流量特征设置如下:

突发大小(字节):突发事务长度*(数据宽度/8)= 128* 32/8 = 512

突发请求总数: 4帧模拟数据= 4*流量数据/突发大小= 4*8100 = 32400

突发间访问时间:帧周期/突发请求数= 16.67e-3/8100 = 20.58e-7秒。数据流量是恒定的,以恒定的速率连续接收数据。爆破时间设置如下:

第一次爆发时间= 20.58 e -

脉冲之间的随机时间= [20.58e-7 20.58e-7]

用上面的值更新Memory Traffic Generator1和Memory Traffic Generator4块掩码。设置请求类型对于内存流量生成器1和内存流量生成器4的写入器和读取器。清除等待爆破完成选项在两个块掩码,因为这些主人代表主人与连续的流量,如HDMI相机和显示器。

内存流量发生器2和3:内存流量发生器2代表FPGA算法的读取器,内存流量发生器3代表FPGA算法的写入器。master 2和master 3的内存流量特征设置如下:

突发大小(字节):突发事务长度*(数据宽度/8)= 128* 32/8 = 512

突发请求总数: 4*流量数据/突发大小= 4*8100 = 32400(4帧模拟数据)

突发间访问时间:(突发长度+ 10)/时钟周期= 6.9e-7(0.69us)。为了允许数据读写请求的突发时间具有一定的随机性,由于算法需求的变化,突发时间设置如下:

第一次爆发时间: 7.2 e -

脉冲之间的随机时间: [7.2e-7 7.4e-7]

模拟

运行模型。模拟完成后,打开内存控制器块并单击查看性能图下性能选项卡。选择下的所有master带宽选择并单击创建图。您可以注意到,所有主服务器的带宽都大致达到了190 MBps,没有达到所需的248 MBps。诊断查看器中的警告也可以观察到这一点。

为了满足带宽要求,在下面的配置参数设置中将控制器的数据宽度从32修改为64目标硬件资源。这需要相应地更改内存流量发生器设置,如下所示:

突发大小(字节):突发事务长度*(数据宽度/8)= 128* 64/8 = 1024

突发请求总数: 4*流量数据/突发大小= 4*4050 = 16200(4帧模拟数据)

内存流量发生器1和内存流量发生器4的突发访问时间:帧周期/突发请求数= 16.67e-3/4050 = 41.16e-7秒。

第一次爆发时间: 41.16 e -

脉冲之间的随机时间: [41.16e-7 41.16e-7]

对于内存流量生成器2和3,爆发之间的第一次爆发时间和随机时间没有变化,因为它们是根据算法需求确定的。

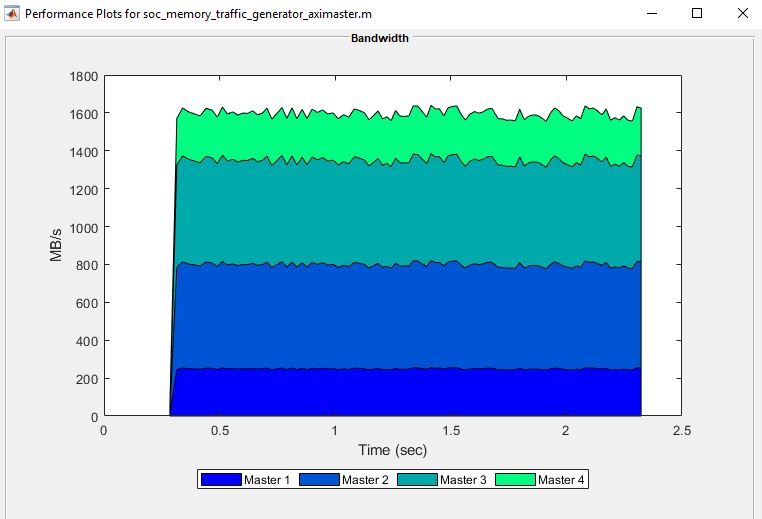

模拟模型并打开带宽图从内存控制器,如前所述。注意,内存流量发生器1和4实现的内存带宽为248 MBps。生成器2和3的内存带宽约为500 MBps。这满足了设计要求,因为所有的主机都能满足248mhz的实时性要求。注意,诊断查看器上没有警告,因为突发请求没有被丢弃。

在硬件上实现和运行

SoC Blockset支金宝app持包Xilinx设备为本节所必需。

要在受支持的FPGA板上实现该模型,请使用金宝appSoC建设者应用程序。默认情况下,将在上面实现模型Xilinx®Zynq®ZC706评估试剂盒因为它是用那个板配置的。

AXI流量发生器(ATG),内存流量发生器块的硬件IP核不支持随机突发访问时间,它在仲裁策略中区分Reader和Writer主,而不像内存流量发生器块用于模拟。金宝app因此,在硬件上实现之前,需要对内存块进行如下修改:

让所有内存流量生成器都成为“写入器”

对于内存流量发生器2和3,为突发之间的随机时间设置[7.2e-7 7.2e-7],使其固定在7.2e-7的突发之间时间

打开SoC建设者,选择片上系统选项卡中的Simuli金宝appnk工具条,然后单击配置、构建和部署按钮。一旦SoC Builder打开,请遵循以下步骤:

选择构建模型在设置屏幕上。点击下一个。

点击查看/编辑内存映射查看上的内存映射回顾内存映射屏幕上。点击下一个。

指定项目文件夹选择项目文件夹屏幕上。点击下一个。

选择构建、加载和运行在选择构建操作屏幕上。点击下一个。

点击验证检查模型的兼容性验证模型屏幕上。点击下一个。

点击构建开始建立模型构建模型屏幕上。当FPGA合成开始时,一个外部外壳将打开。点击下一个来负载比特流屏幕上。

FPGA合成可能需要30分钟以上才能完成。为了节省时间,您可能希望通过以下步骤使用提供的预生成的比特流:

关闭外壳以终止合成。

复制预生成的比特流到您的项目文件夹,并通过运行以下命令重命名。

拷贝文件(fullfile (matlabshared.sup金宝appportpkg.getSupportPackageRoot,“工具箱”,“soc”,...“金宝appsupportpackages”,“xilinxsoc”,“xilinxsocexamples”,“比特流”,...“soc_memory_traffic_generator-zc706.bit”),”。/ soc_prj ');

点击负载按钮加载预生成的比特流。

要运行此示例,请将示例测试工作台复制到项目文件夹中。

拷贝文件(fullfile (matlabroot,“工具箱”,“soc”,“socexamples”,...“soc_memory_traffic_generator_aximaster.m”),”。/ soc_prj ',“f”);

测试台将生成的硬件ATG IP核配置为内存流量生成器。要在硬件上运行,将突发请求的数量增加100倍MATLAB®作为AXI MasterIP将样本返回到MATLAB®,这涉及到访问硬件的大量延迟。负载soc_memory_traffic_generator_zc706_aximaster.mat在ATG配置中将所有master的突发请求数量增加到100倍。将.mat文件请求保存在ATG配置中。

输入以下命令运行测试台soc_memory_traffic_generator_aximaster。

soc_memory_traffic_generator_aximaster

运行测试台架之后,将生成以下输出,显示内存流量。所有主机通过带宽要求。

在Xilinx®Kintex®7 KC705开发板上实现:为了在KC705开发板上实现该模型,必须先将模型配置到Xilinx®Kintex®7 KC705开发板上,并设置如下样例参数。开放型号配置参数,导航到硬件实现选项卡,执行如下操作:

选择Xilinx®Kintex®7 KC705开发板下拉列表硬件板。

导航到目标硬件资源>FPGA设计(顶级)TAB并启用包括MATLAB作为AXI主IP,用于基于主机的交互。

导航到目标硬件资源>FPGA设计(mem控制器)制表符和设置控制器数据宽度(位)来64。

导航到目标硬件资源>FPGA设计(调试)TAB并启用包括AXI互连监视器。

接下来,打开SoC Builder,并按照前面针对Xilinx®Zynq®ZC706所述的步骤进行操作。修改copyfile命令以匹配Kintex®7 KC705开发板位流,如下所示。

拷贝文件(fullfile (matlabshared.sup金宝appportpkg.getSupportPackageRoot,“工具箱”,“soc”,...“金宝appsupportpackages”,“xilinxsoc”,“xilinxsocexamples”,“比特流”,...“soc_memory_traffic_generator-kc705.bit”),”。/ soc_prj ');

总之,在设计算法之前,您模拟了预期设计的内存流量。您分析了内存带宽并修改了内存参数以满足设计要求。您在硬件上验证了结果。