使用模板创建SoC模型

SoC Blockset™模型模板为用于仿真、HDL代码生成或SoC部署的模型提供了设计模式和最佳实践。从任何一个SoC Blockset模型模板创建的模型都设置了用于仿真和代码生成的配置参数。

使用创建SoC模型SoC Blockset模板

为了有效地为SoC设计建模硬件,可以使用SoC Blockset模板创建一个项目。

在MATLAB中®Home选项卡,选择金宝app按钮。或者,在命令行输入:

金宝app

关于Simul金宝appink®开始页,向下滚动到SoC Blockset部分,其中包含到常见工作流的SoC模板的链接。选择一个模板并保存项目。在工作区中打开一个项目文件夹,其中包含:

一个有名字的模型

soc_ * _top.slx- SoC项目的顶层模型。referencedmodels-包含从顶部模型引用的模型的文件夹。一些模板包括FPGA模型和处理器模型。其他模板只包含一个参考模型:FPGA模型或处理器模型。公用事业公司-包含模型使用的实用函数或测试台数据的文件夹。

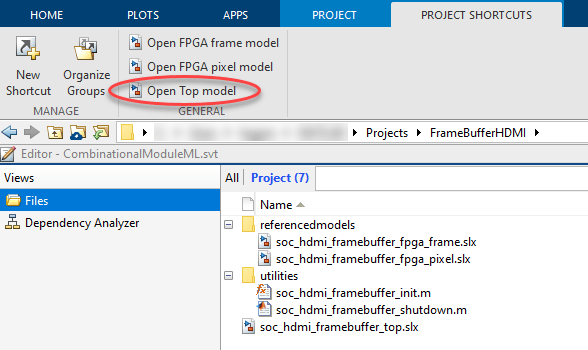

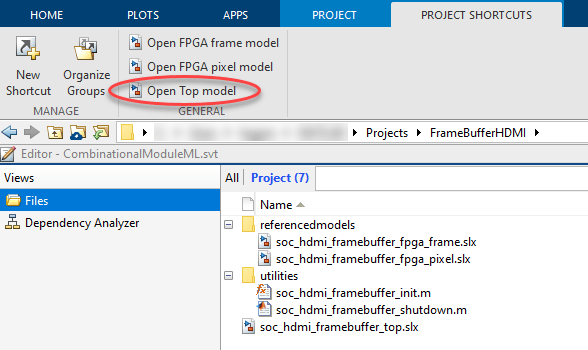

要在Simulink中打开顶层模型,请在金宝app项目的快捷方式选项卡上,单击开放式顶模.

在每个模板中,导航到标记的块FPGA算法在FPGA模型,或处理器的算法在处理器模型中。这些块被突出显示以便于检测。用您自己的算法模型替换模板块。

提示

要轻松地找到算法块,请在整个模型层次结构中遵循注释。

打开SoC Blockset块库,选择库浏览器按钮,然后选择SoC Blockset在左边的窗格中。或者,在命令行输入:

该库包括用于创建SoC模型和测试工作台的块。soclib

模板结构

SoC Blockset模板中的顶层模型包括一个FPGA子系统,它表示用于对FPGA编程的逻辑。FPGA子系统包括两个Simulink模型变体:金宝app

基于框架的FPGA模型-用于增强仿真性能(在RFSoC模板中不可用)

基于样本的FPGA模型-用于周期精度和代码生成

顶层模型还包括一个处理器子系统,它表示打算在SoC处理器上运行的软件程序。FPGA和顶层子系统都包含标记为FPGA算法或处理器算法的块。用你自己的逻辑替换这些算法。该模板的顶层模型还包括一个内存系统,具有内存控制器和内存通道。这些块表示板子上的物理内存系统。该模型通常包括寄存器通道(用于实现处理器和FPGA之间的通信)、测试台或I/O块。

修改项目

修改FPGA模型

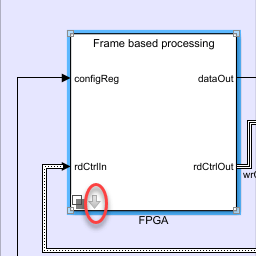

从顶部的模型,通过点击FPGA块左下角的箭头打开FPGA模型:

FPGA模型包含两个模型变体:基于帧的变体和基于样本的变体。双击要修改的模型变体。FPGA模型通常包括两个主要子系统供您修改:

FPGA算法包装器-双击打开模型。算法包装器包含一个名为FPGA算法.这个块有两个输入和一个输出,被实现为一个乘数。用您自己的FPGA算法替换此块。根据需要添加输入和输出。

测试源包装器-该块包括一个测试源,旨在生成刺激作为FPGA算法的输入。根据您的需要修改测试源,或者用另一个源块替换它。如果FPGA算法的输入是从I/O块(如HDMI或SDR)路由的,请考虑使用特定的应用程序模板。

请注意

并非所有模板都在FPGA模型中包含测试源块。

修改处理器模型

处理器模型包括一个任务管理器块和处理器包装器。该模板将处理器算法实现为“直通”线。打开处理器算法包装器,并替换处理器的算法块(蓝色突出显示)与您所需的算法。

修改注册通道

模板的顶层模型还包括用于处理器和FPGA模型之间通信的寄存器通道。使用寄存器通道配置FPGA模式,l或读取和检查状态寄存器。的注册通道模板中的块包含一个寄存器。要添加额外的寄存器,您必须修改寄存器通道块参数,FPGA算法和处理器算法:

将寄存器添加到寄存器通道-双击注册通道块打开块掩码,并根据需要添加额外的寄存器。上添加寄存器将创建额外的端口注册通道块。有关其他信息,请参见注册通道.

向处理器模型添加端口-导航到处理器算法包装器模型。要导航到处理器模型,请单击开放处理器模型在项目的快捷方式选项卡。双击处理器算法包装器修改它。

对于写寄存器,向模块添加一个输出端口,并添加逻辑以将值驱动到添加的输出端口。对于读寄存器,添加一个输入端口和逻辑来处理从读寄存器返回的信息。从顶层模型,电线端口到注册通道块。

为FPGA模型添加端口-导航到FPGA算法封装模型。单击,进入基于FPGA/Frame的处理模型开放式FPGA样本模型在项目的快捷方式选项卡。双击FPGA算法封装修改它。

对于写寄存器,向模块和逻辑添加一个输入端口,以处理从读寄存器返回的信息。对于读寄存器,添加一个输出端口和逻辑,将值驱动到添加的输出端口。

为了在使用Simulink基于样本的变体时实现等效行为,请在FPGA包装器金宝app中对基于样本的处理模型重复此步骤。

从顶层模型,电线新的端口到注册通道块。