SDR模板

软件无线电(SDR)模板为SoC参考设计提供了一个仿真模型,可从通讯工具箱™ Xilinx支持包金宝app®Zynq公司®-基于无线电的. 使用此模板模拟全参考设计,并分析内部和外部连接对内存和SDR算法的影响,例如内存行为和射频(RF)I/O行为。

开始使用SoC块集™ 用于设计SDR系统的模型,请遵循以下步骤使用SoC块集模板创建SoC模型.

所需产品下载188bet金宝搏

通讯工具箱

Xilinx设备的SoC块金宝app集支持包

模板结构

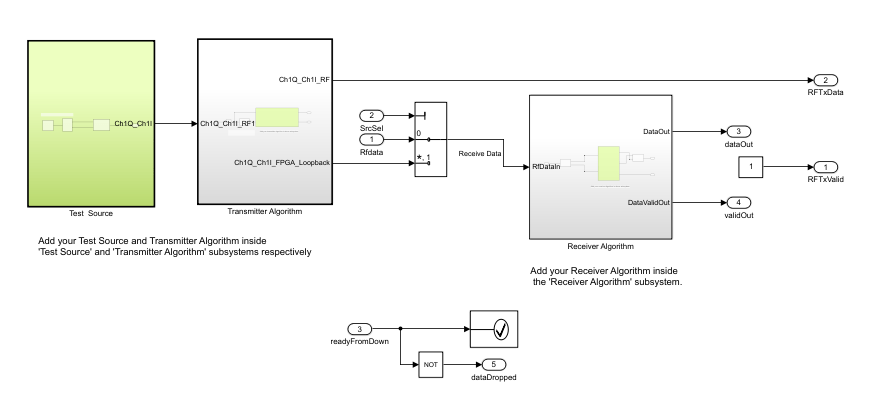

该模板对由AD9361发射器和接收器模块组成的SDR收发器进行建模。收发机将射频信道连接到FPGA,FPGA实现了接收机和发射机算法。FPGA算法包括测试源块,它产生一个正弦信号并将其驱动到发射器。FPGA算法还包括Tx算法(实现为简单的直通线)和Rx算法(实现为增益块)。配置寄存器srcSel公司在FPGA中建模,为Rx算法选择数据源。处理器写入srcSel公司注册以选择来自FPGA的测试源或来自收发器的RF数据。该寄存器使用寄存器通道阻止。来自FPGA算法的数据通过记忆通道阻止。

使用此模板作为指导,用自己的功能替换FPGA中的Rx算法和Tx算法以及处理器中的处理器算法。记忆渠道类型参数设置为AXI4通过DMA流到软件它通过共享外部存储器来模拟直接存储器存取(DMA)数据传输。

处理器从内存中读取计算出的数据,并执行额外的计算(在模板中作为直通线实现)。可以通过双击向量范围阻塞测试台水槽。

修改项目

修改FPGA模型

在MATLAB中®,在项目快捷方式选项卡,单击开放式FPGA示例模型. 然后,打开FPGA Tx Rx Alg包装器。请注意以绿色突出显示的三个区域。这些区域代表用户代码,位于接收器算法块、发射器算法块和测试源块中。

FPGA模型包括以下部分供您修改(以绿色突出显示):

测试源块–此块生成10 kHz正弦信号,并将其驱动到发射器算法。根据您的需要修改测试源或用替代源块替换它。

接收器算法子系统–在绿色高亮显示的子系统内,名为Rx算法,有一个块标记算法。该算法以I/Q数据作为输入,以有效信号作为输出。用您自己的Rx算法替换此块。

发射器算法–在绿色高亮显示的子系统内,名为Tx算法算法有一个来自测试源的输入和两个输出信号:一个到射频通道,一个到FPGA。用您自己的Tx算法替换此块。

要启用一致的模拟行为,请在项目快捷方式选项卡,单击开放式FPGA帧模型重复这个步骤。

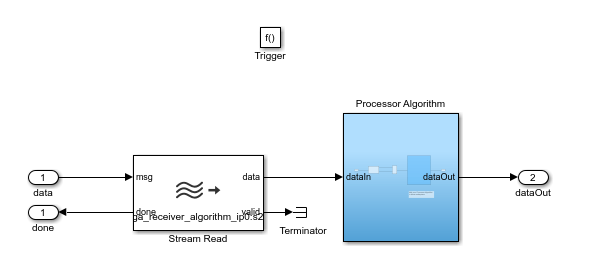

修改处理器型号

在MATLAB中,在项目快捷方式选项卡,单击开放处理器模型. 以蓝色突出显示的子系统表示处理器算法的用户代码。打开处理器算法包装器并替换内部处理器算法块(也用蓝色突出显示)和所需的算法。

修改寄存器通道

模板的顶部模型还包括用于在处理器和FPGA模型之间通信的寄存器信道。使用寄存器通道配置FPGA模型或读取和检查状态寄存器。这个寄存器通道模板中的块包含一个寄存器。要添加其他寄存器,必须修改寄存器通道块参数、FPGA算法和处理器算法:

将寄存器添加到寄存器通道–双击寄存器通道block打开块掩码并根据需要添加其他寄存器。添加寄存器会在寄存器通道阻止。有关其他信息,请参阅寄存器通道.

向处理器型号添加端口–导航到处理器算法包装器模型。要导航到处理器型号,请单击开放处理器模型上项目快捷方式选项卡。双击处理器算法包装器修改它。

对于写寄存器,将输出端口添加到模块,并添加逻辑以将值驱动到添加的输出端口。对于读寄存器,添加一个输入端口和逻辑来处理从读寄存器返回的信息。从顶部模型,将端口连接到寄存器通道阻止。

向FPGA模型添加端口–导航到FPGA算法包装器模型。要导航到基于FPGA/帧的处理模型,请单击开放式FPGA示例模型上项目快捷方式选项卡。双击FPGA算法包装器修改它。

对于写寄存器,向模块和逻辑添加一个输入端口,以处理从读寄存器返回的信息。对于读寄存器,添加一个输出端口和逻辑以将值驱动到添加的输出端口。

使用Simulink时的等效行为金宝app®基于样本的变体,对FPGA包装器中基于样本的处理模型重复此步骤。

从顶部模型,将新端口连接到寄存器通道阻止。