IP核生成I2C控制器IP配置音频编解码芯片

本示例说明如何使用使用Stateflow™模块建模的I2C主控制器来对I2C控制器进行建模,以配置音频编解码器芯片。

在这个例子中,你:

使用Simulink中的Stateflow®块对I2C主控制器进行建模金宝app

使用I2C主控制器块对I2C控制器进行建模,以配置音频编解码器芯片

利用黑盒子系统和双向端口特性来处理I2C IP核中的三态逻辑

通过IP核生成流程为I2C控制器生成IP核

1.I2C协议概述

I2C总线,也称为Inter-IC总线,是一种简单、多主、多从、双向两线总线,由串行数据(SDA)和串行时钟(SCL)线组成。连接到总线上的每个设备都可以通过唯一的7位或10位地址进行软件寻址,并保持简单的主从关系。串行,8位导向,双向数据传输可以在标准模式下以高达100kbit /s,在快速模式下高达400kbit /s,或在高速模式下高达3.4 Mbit/s进行。I2C总线有两个节点:主节点和从节点。主节点生成时钟并发起与从节点的通信。由主机寻址的从节点在确认期间接收时钟并响应主机。有四种操作模式,即主发送、主接收、从发送和从接收。主站通过发送开始位,然后是从站的7位或10位地址,然后是读(1)或写(0)位来开始通信。如果与该地址对应的从机存在,则它以ACK位进行响应。主机基于读或写位以发送或接收模式继续通信。 Similarly, the slave continues its operation based on the read or write instruction from the master. The figure below shows the timing diagram of I2C protocol.

2.在Simulink中使用状态流块建模广义I2C主控制器金宝app

在设计中配置多个外围设备可能是一个繁琐而乏味的过程。相反,创建一个通用的I2C主控制器,可以直接用于配置音频编解码器芯片。下图展示了在Simulink中使用Stateflow块实现的通用I2C主控制器的体系结构。金宝app

上面的部分显示了I2C主控制器块。要配置外设,必须向I2C主控制器块提供特定于设备的配置。使用I2C主控制器配置音频编解码芯片的框图如下所示。

下面的模型展示了在Simulink中使用Stateflow块建模的I2C主控制器。金宝app

modelname =“hdlcoder_I2C_master_controller”;open_system (modelname);open_system (“hdlcoder_I2C_master_controller / I2C_MasterController”);

I2C主控制器目前只支持I2C写,不支持I2C读回。金宝appI2C主控制器由两部分组成:I2C主控制器图和三态缓冲黑盒。I2C主控制器图通过三态缓冲黑盒向从设备提供串行数据、SDA和串行时钟、SCL。三态缓冲区黑盒使用手写的VHDL代码,用于SDA端口的双向功能。由于Simulink不支持双向端口建模,在模型中加入了三态缓冲区黑盒。金宝app金宝app

要创建黑匣子,请执行以下步骤。

1.制作一个子系统,其中包含您想导入用于创建黑盒的HDL源代码的输入和输出端口。I2C三态缓冲区黑盒如下所示。

2.要将子系统指定为黑盒接口,请右键单击子系统并选择HDL代码> HDL块属性并将“架构”设置为“黑匣子”,如下图所示。

3.数据端口I2C_SDAI2C主控制器是双向的。要将端口设置为双向,请右键单击I2C_SDA端口和单击HDL块属性,并设置双向端口如下所示。

4.在仿真时,将使用黑盒子系统内部的实际内容进行仿真。

在代码生成过程中,HDL Coder不会在黑盒子系统下生成代码。相反,代码生成器将您手写的HDL代码集成到IP核中。I2C主控制器块的输入可以通过在输入端添加设备特定的配置图来提供。此图表包含有关需要为从设备配置的寄存器的详细信息。有关设备配置的更多信息,请参阅Zedboard, Zybo板和Arrow SoC开发套件使用I2C主控制器的音频编解码器配置部分。

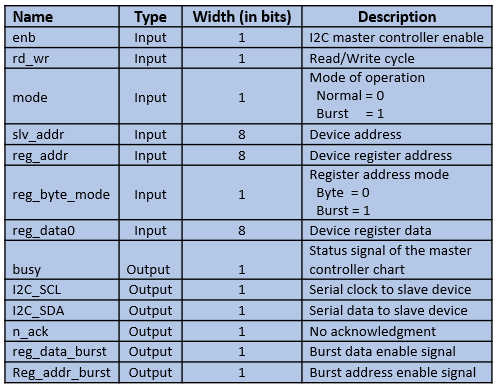

2.1 I2C主控制器块I/O描述

I2C Master Controller模块的输入输出接口如下图所示。

2.2 I2C主控制器状态流程图描述

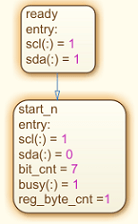

I2C主控制器图是在所有状态下生成所需时钟(SCL)并根据I2C协议通过串行数据(SDA)端口提供数据的方式制作的。下面的状态显示了时钟和开始位的生成。

以下状态用于发送从设备的7位地址。

这个函数bitget用于向SDA端口串行发送位。它允许用户在其参数列表中提到的整数的指定位置获得位值。从一种状态到另一种状态的转换取决于为转换条件指定的执行顺序。如上图所示,过渡从cmd_slave_addr_p到cmd_slave_addr_n状态基于转换条件(bit_cnt > 0)发生。bit_cnt的值一直递减,直到转换条件满足。bit_cnt的值初始化为“7”,它的值递减到“1”,用于在SDA端口上发送从设备的7位地址。对于HDL代码生成,必须使用支持的数据类型。金宝app冒号(:)是cmd_slave_addr_n状态中使用的类型转换运算符(scl(:)= 0)将类型为'double'的值转换为类型为'logical' (scl是所示状态中的逻辑数据类型)。下面显示的状态用于向从设备发送寄存器地址。

下面显示的状态用于将寄存器数据发送到从设备。

下面的状态显示了停止位的生成。

3.在Zedboard上使用I2C主控制器库块配置音频编解码器ADAU1761

本节介绍如何:

模型音频编解码器ADAU1761设备配置图使用statflow块在Simulink。金宝app

使用I2C主控制器库块配置音频编解码器ADAU1761。

执行所创建模型的仿真。

如前所述,要在Zedboard上配置音频编解码器ADAU1761,需要创建ADAU1761的设备配置图。这个图表应该连接到前面创建的I2C主控制器库块。

注意:您必须为自己的设备创建设备配置表。本例将展示如何使用I2C主控制器库块来配置音频编解码器设备。用于ADAU1761的设备配置图是特定于此设备的,不能用于配置其他设备。

为ADAU1761创建的配置模型如下所示。

modelname =“hdlcoder_I2C_adau1761”;open_system (modelname);

3.1模拟音频编解码器ADAU1761配置模型

对于音频编解码芯片ADAU1761,需要配置20个寄存器。其中很少必须由I2C主控制器以突发模式和字节模式写入。第一个寄存器以字节模式写入,第二个寄存器以长度为6字节的突发模式写入。其余18个寄存器以字节模式写入。

音频编解码器ADAU1761配置仿真波形如下图所示。

I2C主控制器与音频编解码芯片ADAU1761之间的字节模式传输如下图所示。

下面的模拟显示了开始位的发送,然后是从设备的7位地址(0x3B),然后是写(0)位,然后是16位寄存器地址(0x4000),然后是8位寄存器数据(0x0E)和从设备的确认。

3.2 IP Core生成流程

要生成音频编解码器ADAU1761配置HDL IP核,请遵循下面给出的步骤。

1.在MATLAB命令窗口中使用以下命令设置Xilinx Vivado合成工具路径。运行该命令时,请使用自己的Vivado安装路径

hdlsetuptoolpath (“ToolName”,“Xilinx Vivado”,“路径”,“C: \ Xilinx \ Vivado \ 2017.4 \ bin \ vivado.bat ');

2.在ADAU1761配置模型中,选择I2C_IP子系统,然后右键单击打开HDL工作流顾问。在任务1.1中,选择IP核生成对于目标工作流程,通用Xilinx平台目标平台及Xilinx Vivado用于合成工具。还可以选择系列、设备、包和速度,如下图所示。

3.在任务1.2中,将所有端口的“目标平台接口”设置为“外部端口”。

4.三态HDL逻辑出现在VHDL文件hdlcoder_i2c_trstate .vhd中。将其复制到当前工作目录中。

copyfile(fullfile(matlabroot, 'toolbox', 'hdlcoder', 'hdlcoderdemos', ' hdlcoder_i2c_trstate .vhd'), ' hdlcoder_i2c_trstate .vhd');

5.在Task 3.2中,将三态缓冲区VHDL文件添加到其他源文件中。然后右键单击生成RTL代码和IP核,然后单击运行到选定的任务。

生成用于配置ADAU1761的I2C IP Core。下图显示了IP核生成报告。

生成的IP核可用于用户参考设计。要创建参考设计,请参见在Zynq板上编写音频系统参考设计.

4.在Zybo板上使用I2C主控制器库块配置音频编解码器SSM2603

本节介绍如何:

模型音频编解码器SSM2603设备配置图使用statflow块在Simulink。金宝app

使用I2C主控制器库块配置音频编解码器SSM2603。

执行所创建模型的仿真。

要在Zybo板上配置音频编解码器SSM2603,需要创建SSM2603的设备配置图。这个图表应该连接到前面创建的I2C主控制器库块。

注意:用于SSM2603的设备配置图表特定于此设备,不能用于配置其他设备。

为SSM2603创建的配置模型如下所示。

modelname =“hdlcoder_I2C_ssm2603”;open_system (modelname);

4.1模拟音频编解码器SSM2603配置模型

音频编解码芯片SSM2603需要配置11个寄存器。所有数据都将以字节模式写入。

音频编解码器SSM2603配置仿真波形如下图所示。

下面的模拟显示了开始位的发送,接着是从设备的7位地址(0x1A),接着是写(0)位,接着是8位寄存器地址(0x0C),接着是8位寄存器数据(0x10)和从设备的确认。

4.2 IP核生成流程

SSM2603配置模型的IP Core生成步骤与上文第3.2节IP Core生成工作流程中提到的步骤相同。生成的IP核可用于用户参考设计。要创建参考设计,请参见在ZYBO板上编写音频系统参考设计.

5在Arrow SoC Development Kit上使用I2C主控制器库块配置音频编解码器SSM2603

本节介绍如何:

模型音频编解码器SSM2603设备配置图使用statflow块在simulink。金宝app

使用I2C主控制器库块配置音频编解码器SSM2603。

执行所创建模型的仿真。

要在Arrow SoC Development Kit上配置音频编解码器SSM2603,需要创建SSM2603的设备配置图。这个图表应该连接到前面创建的I2C主控制器库块。

注意:用于SSM2603的设备配置图表特定于此设备,不能用于配置其他设备。

Arrow SoC Development Kit上SSM2603的配置模型与Zybo板上SSM2603的配置模型相同。有关SSM2603配置模型,请参阅本文的第4节。

5.1模拟音频编解码器SSM2603配置模型

Arrow SoC Development Kit上的音频编解码芯片SSM2603配置与Zybo板上的音频编解码芯片SSM2603配置相同。请参考本文第4.1节进行模拟。

5.2 IP核生成流程

要生成音频编解码器SSM2603配置HDL IP核,请遵循下面给出的步骤。

1.在MATLAB命令窗口中使用以下命令设置Intel Quartus工具路径。运行该命令时,请使用自己的Quartus安装路径

hdlsetuptoolpath (“ToolName”,Altera Quartus II,“路径”,“C: \ intelFPGA \ 18.1 \第四的\ bin64 \ quartus.exe);

2.在SSM2603配置模型中,选择I2C_SSM2603子系统,然后右键单击打开HDL工作流顾问。在任务1.1中,选择IP核生成对于目标工作流程,通用Altera平台目标平台及Altera QUARTUS II用于合成工具。还可以选择系列、设备、包和速度,如下图所示。

3.在任务1.2中,将所有端口的“目标平台接口”设置为“外部端口”。

4.trstate HDL逻辑出现在Verilog文件hdlcoder_I2C_tristate_arrowssm2603.vhd中。将其复制到当前工作目录中。

copyfile(fullfile(matlabroot, 'toolbox', 'hdlcoder', 'hdlcoderdemos', 'hdl_I2C_tristate_arrowssm2603.vhd'), 'hdl_I2C_tristate_arrowssm2603.vhd');

5.在Task 3.2中,将三态缓冲区Verilog文件添加到额外的源文件中。然后右键单击生成RTL代码和IP核,然后单击运行到选定的任务。

生成配置SSM2603的I2C IP Core。下图显示了IP核生成报告。

生成的IP核可用于用户参考设计。要创建参考设计,请参见基于Intel板的音频系统参考设计.