验证手写和生成的HDL代码的组合

此示例使用HDL协同模拟和FPGA在环(FIL)模拟来验证包含生成的和遗留HDL代码的HDL设计。此处使用术语“遗留”来表示可能已手工编写、从第三方购买或为另一个项目生成并保存以供此设计中重用的代码。

该示例中的遗留代码实现有限状态机(FSM),该有限状态机是多输入多输出(MIMO)解码器的子模块,该解码器旨在用于无线通信系统中。大多数MIMO解码器都是在Simulink中开发的,其HDL代码将由HDL编码器生成。FSM属于Simulink设计。FSM的遗留代码将与Simulink模型集成,并通过代码生成过程并入FPGA实现。金宝app

该示例将展示设计师或验证工程师如何使用HDL验证器协同模拟向导将传统FSM与Simulink模型集成,并对其进行验证。HDL协同模拟提供了完整的可视性和控制,支持代码的调试和验证。金宝app

成功集成遗留FSM后,当从Simulink模型生成HDL代码时,协同模拟块自动合并遗留代码,从而实现MIMO解码器的完整FPGA实现。最后,使用FPGA在环路中在实际FPGA上验证整个设计。金宝app

示例概要

使用cosimulation向导将旧HDL代码导入Simulink模型金宝app

通过联合模拟旧HDL代码并将结果与行为模型进行比较,验证旧HDL代码

使用黑盒中的协同模拟块为整个MIMO解码器生成HDL代码

用FPGA在环路中验证MIMO解码器

要求和先决条件

对于cosimulation和fpga-in-in-loop,您需要以下软件和硬件:

支持的HDL模拟器之一金宝app。有关支持的模拟器,请参阅联合模拟要求.

FPGA设计软件

支持的FPGA开发板之金宝app一。有关支持的硬件,请参阅金宝app用于FPGA验证的支持FPGA设备.

对于使用以太网的连接:安装在主机上的千兆以太网适配器、千兆以太网交叉电缆

用于使用JTAG:USB Blaster I或II电缆和英特尔FPGA板驱动程序进行连接。Digilent®JTAG电缆和Xilinx FPGA板驱动程序。

MATLAB®和FPGA设计软件可以本地安装在您的计算机上,也可以安装在网络可访问的设备上。如果您使用网络上的软件,则需要在计算机上安装第二个网络适配器,以便为FPGA开发板提供专用网络。请参阅计算机的硬件和网络指南以了解n如何安装网络适配器。

注意:该示例包括代码生成。如果您没有访问HDL编码器软件的权限,可以跳过本例中的代码生成步骤,使用提供给您的HDL文件和FIL向导,在循环中使用FPGA模拟它们。

为有限状态机创建一个参考模型

参考模型是实现的行为的模拟模型。它通常在HDL验证中使用,通过将其与RTL实现实例化,为两者提供相同的输入并进行比较它们的输出。验证中的参考模型的优点是它们可以独立于实现(通常由不同的人)开发,提供了对预期行为的独立验证,它们比实际实现更容易(不需要合成或实际设备时序))它们通常在模拟中快速运行。

在此示例中验证传统HDL代码的第一步是为该部分的设计创建参考模型。已经为FSM完成了。打开行为_mimo.slx模型。双击MIMO解码器子系统,您将看到FSM子系统包含一个实现FSM行为的MATLAB功能块。此参考模型将用于验证FSM的传统HDL代码。

1.使用协同模拟向导导入旧版HDL代码

通过在MATLAB命令提示符下键入以下命令来调用协同模拟向导:

科西姆维扎德

从下拉列表中选择HDL与Simulink和首选HDL模拟器金宝app的协同模拟。如果HDL模拟器不在系统路径上,请提供路径并单击“下一步”。

使用cosimWizard的Add按钮添加FSMSubsystem.vhd、FSMSubsystem_pkg.vhd和Embedded_Controller.vhd文件(位于“verify_legacy_hdlsrc”文件夹中),并对列表重新排序,将FSMSubsystem.vhd放在列表底部,将FSMSubsystem_pkg.vhd放在列表顶部,以获得正确的编译顺序。然后单击下一步。

单击以下2面板上的“下一步”以接受默认值并到达输入/输出端口面板。在输入端口列表中,从前3个端口的下拉列表中选择以下端口类型值:

时钟:端口类型=时钟重置:端口类型=重置时钟\u启用:端口类型=重置

端口类型的这种识别会导致协同模拟块强制HDL模拟器中的这些信号,而不是要求在Simulink图中驱动这些信号。在本例中,我们将clk_启用端口视为协同模拟的另一个重置。在继续下一步之前,类似地选择“未使用”对于ce_out,由于在Simulink中不需要它,因此导致从协同模拟块中忽略它。金宝app

cosimulation wizard自动识别HDL代码中的输入和输出,并根据在其中找到的端口为Simulink创建cosimulation块。关于输出端口,它无法从HDL代码中了解到一些细节。在HDL代码中,输出只是位的集合,没有指示如何进行模金宝app拟ike在Simulink中解释这些位。您必须告诉cosimulation wizard您希望这些位被视为有符号值还是无符号值,如果要将它们解释为定点数字,则将基数放在何处。

在“输出端口详细信息”面板中,优化每个输出的数据类型。在这种设计的情况下,输出端口的解释如下。请注意,HDL代码中有多个标量端口用于矢量端口(out_1、out_6、out_9、out_10、out_11、out_12):

OUT_1:签名,分数长= 0(4个标量)OUT_2:unsigned,分数长度= 0 OUT_3:unsigned,分数长度= 0 OUT_4:unsigned,分数长度= 0 out_5:签名,分数长度= 10 out_6:签名,分数长度= 10(3个标量)OUT_7:签名,分数长度= 2 OUT_8:未签名,分数长度= 0 OUT_9:签名,分数长度= 0(4个标量端口)OUT_10:签名,分数长度= 0(4个标量)OUT_11:签名,分数长度= 10(4个标量)OUT_12:签名,分数长度= 10(4个标量)OUT_13:无符号,分数长度= 0 OUT_14:签名,分数长度= 0

在时钟/重置详细信息面板上设置以下值:

CLK周期= 10 ns,主动边缘=上升复位初始值= 1,持续时间= 27 ns clk_enable初始值= 0,持续时间= 37 ns

单击“下一步”进入“开始时间校准”面板,并将“HDL开始协同模拟的时间(ns)”设置为40。

继续执行最后一步并取消选中“自动确定在仿真开始时自动确定时间尺度”复选框。对于此示例,我们知道Cosimulation的时间尺度应该是1秒,在Simulink中对应于HDL模拟器中的10 ns。金宝app有关使用其他设计的自动时间尺度设置功能的信息,请参阅HDL验证程序文档。设置上述时间刻度,然后单击“完成”。

将生成用于将传统HDL代码导入Simulink模型的协同模拟块。您可以将新生成的协同模拟块和2个方便命令块拖放到FSMSubsystem块内的Simulink模型中,并金宝app将其连接到FSMSubsystem的输出端口。针对该示例提供了一个协同仿真模型,该模型在MIMO解码器子系统内具有比较器和断言块。已添加比较器和断言块,以提醒您嵌入式控制器参考模型的输出与传统HDL实现之间的任何不匹配。

使用以下命令调整生成的协同模拟块的大小,以便于将其插入到协同模拟模型中:

设置参数('untitled / fsmsubsystem','位置', [0 0 165 852]);

打开cosim_mimo.slx模型。将cosimWizard创建的新块和便利命令块拖动到cosimulation模型中,替换MIMODecoder子系统中的占位符子系统。

2.协同模拟以验证旧HDL代码

在联合仿真模型中,双击“启动HDL模拟器”块以启动所选的HDL模拟器。单击Simulink中的Play(播放)按钮以启动协同模拟,并观察MATLAB窗口中是否显示警告消息。这表明由于参考FSM模型和HDL实现之间的差异,输出信号不匹配。金宝app

现在,您可以使用Simulink金宝app和HDL模拟器调试功能来隔离问题并修复错误。在这种情况下,出现错误是因为HDL实现中缺少状态转换弧。请注意,在HDL模拟器的波形显示中,FSM状态在模拟过程中很早就被卡住了。

修复手写HDL代码并重新运行联合模拟

已为此示例提供更正的HDL代码。请使用以下命令将新代码复制到您的工作目录,覆盖Embedded_Controller.vhd的错误版本:

复制文件(完整文件)(“验证\u遗留\u hdlsrc”,“固定高密度脂蛋白”,'embedded_controller.vhd'),“验证\u遗留\u hdlsrc”,“f”);

双击“编译HDL设计”块,重新编译旧的HDL代码。如果HDL模拟器在上次执行协同模拟后仍然打开,请退出该模拟器,并重新启动HDL模拟器,然后重新播放协同模拟。这一次你不应该发现不匹配。

既然您调试并验证了嵌入式控制器的遗留HDL代码,您可以继续使用FPGA-In--in-Loop验证整个MimoDecoder。

设置FPGA设计软件环境

在使用FPGA循环之前,请确保正确设置系统环境以访问FPGA设计软件。您可以使用该功能刀具轨迹将FPGA设计软件添加到当前MATLAB会话的系统路径。

为HDL代码生成准备模型

要准备FPGA在环模型,包括遗留HDL代码,并为MIMO解码器的其余部分生成新的HDL代码,您需要做两件事来完成FPGA实现:

编辑联合模拟模型以删除FSM参考设计

使用HDL编码器黑盒将遗留HDL合并到模型中以生成代码

如果要按照所有步骤准备模型,以便使用HDL黑盒生成HDL代码,请使用其他名称保存联合模拟模型,然后按照以下步骤继续模型准备的其余部分:

1.编辑联合模拟模型以删除FSM参考设计

在MIMO解码器子系统内部删除嵌入式_Controller功能块

删除驱动嵌入式控制器输入的“自”块,enablecoder输入除外

删除输出上的比较器和断言块

重新连接Cosimulation块输出到DelaysubSystem1的输入

2.使用HDL编码器BlackBox将传统HDL合并到模型中的模型中

选择协同模拟块并键入control-G以创建子系统

右键单击新的协同模拟子系统,然后选择HDL代码和HDL块属性

选择架构=黑盒

在EntityName参数中输入FSMSubsystem

在ImplementationLatency参数中输入0

确定“HDL块属性”对话框

3.重新运行模拟以更新图表。

双击“启动HDL模拟器”块以启动HDL模拟器

单击Simulink中的播放按钮以启动Cosimu金宝applation

保存模型

3.在循环中生成HDL代码和FPGA

这一步需要HDL编码器。如果没有此软件,可以使用预生成的HDL文件进行FIL模拟。直接跳到第5步。使用FIL向导进行FIL模拟。

如果您希望按照流程生成HDL文件并返回模型的顶层,请右键单击MIMODecoder子系统,然后在“HDL代码”下启动HDL Coder Workflow Advisor。

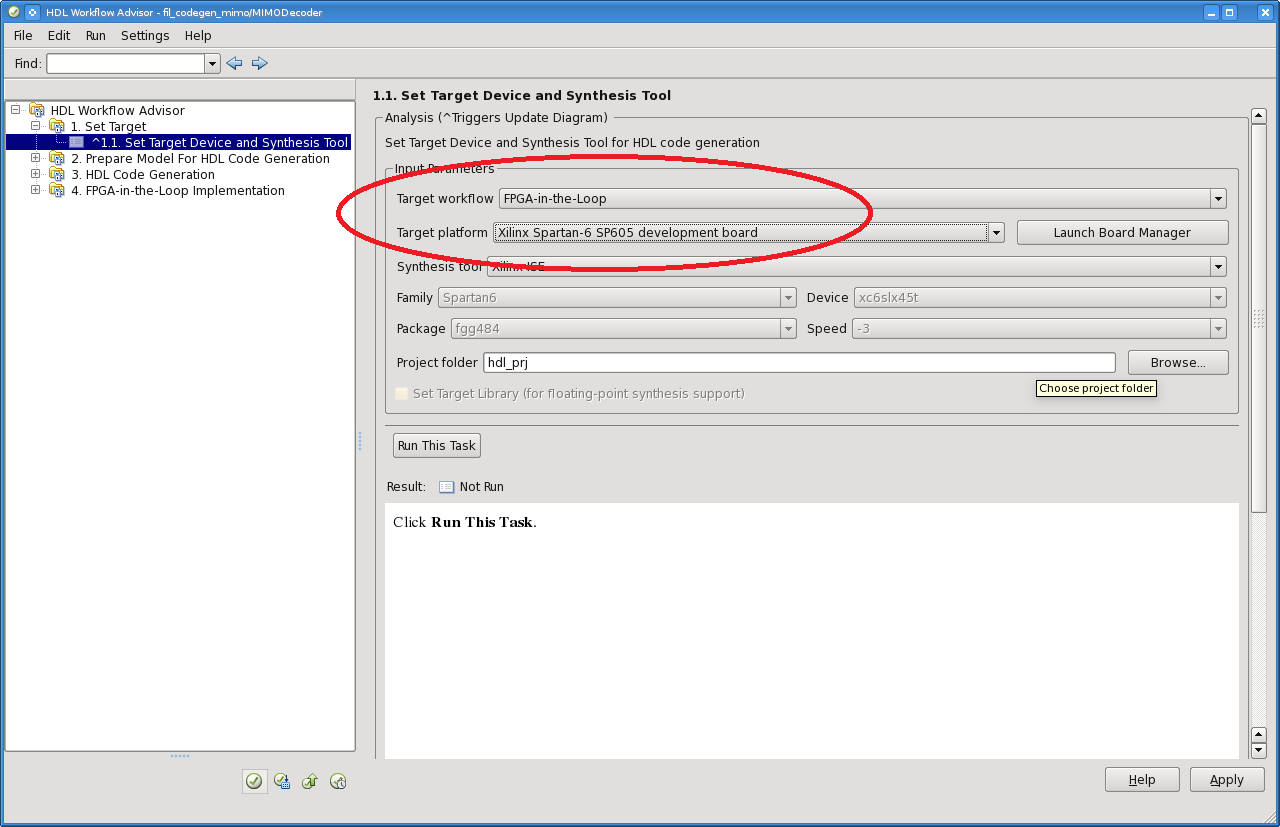

步骤1.1:选择循环中的FPGA目标工作流,从下拉列表中选择首选的FPGA开发板,并确定一个可写目录以保存生成的HDL代码。

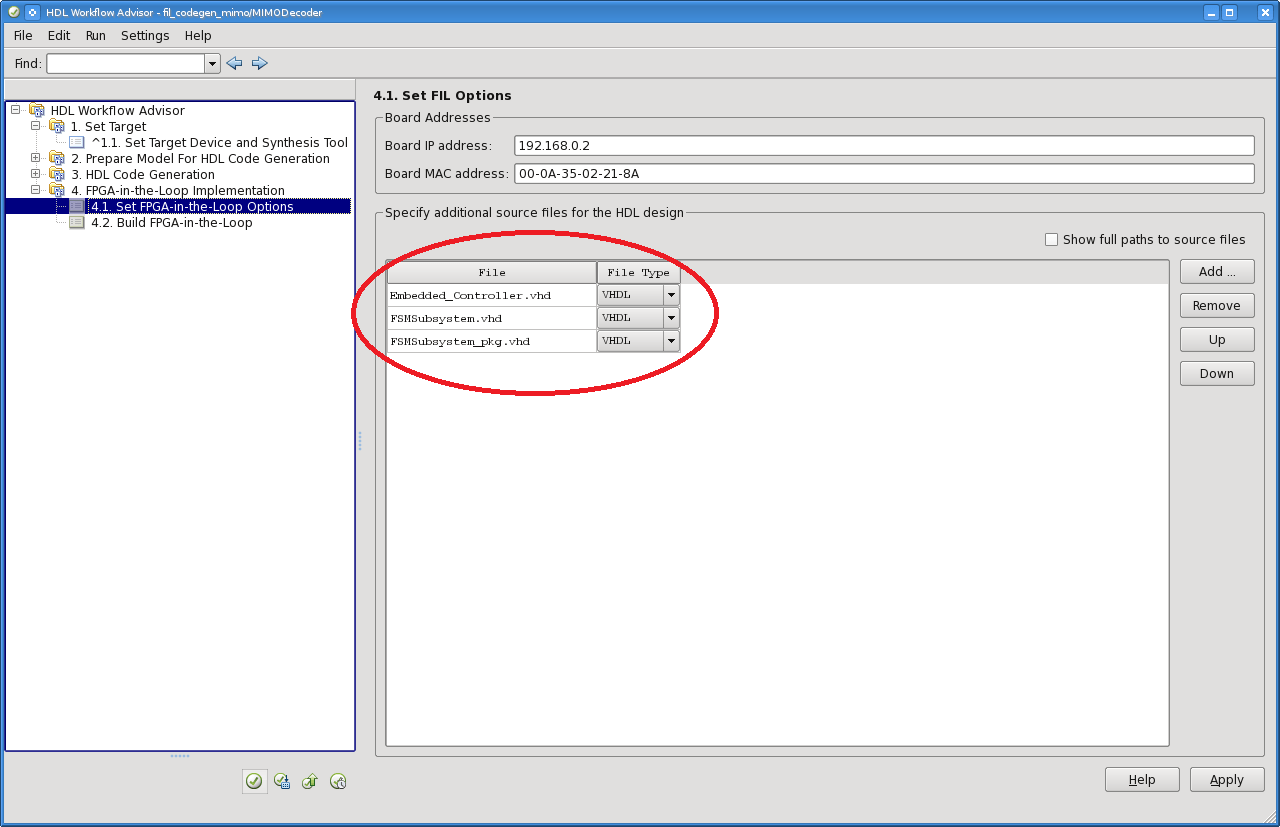

步骤4.1:在“设置FPGA选项”中,选择“添加”并使用浏览器导航到在步骤1中将复制到工作文件夹中复制的EmbeddedController HDL文件,并在步骤3中修改固定的HDL代码。

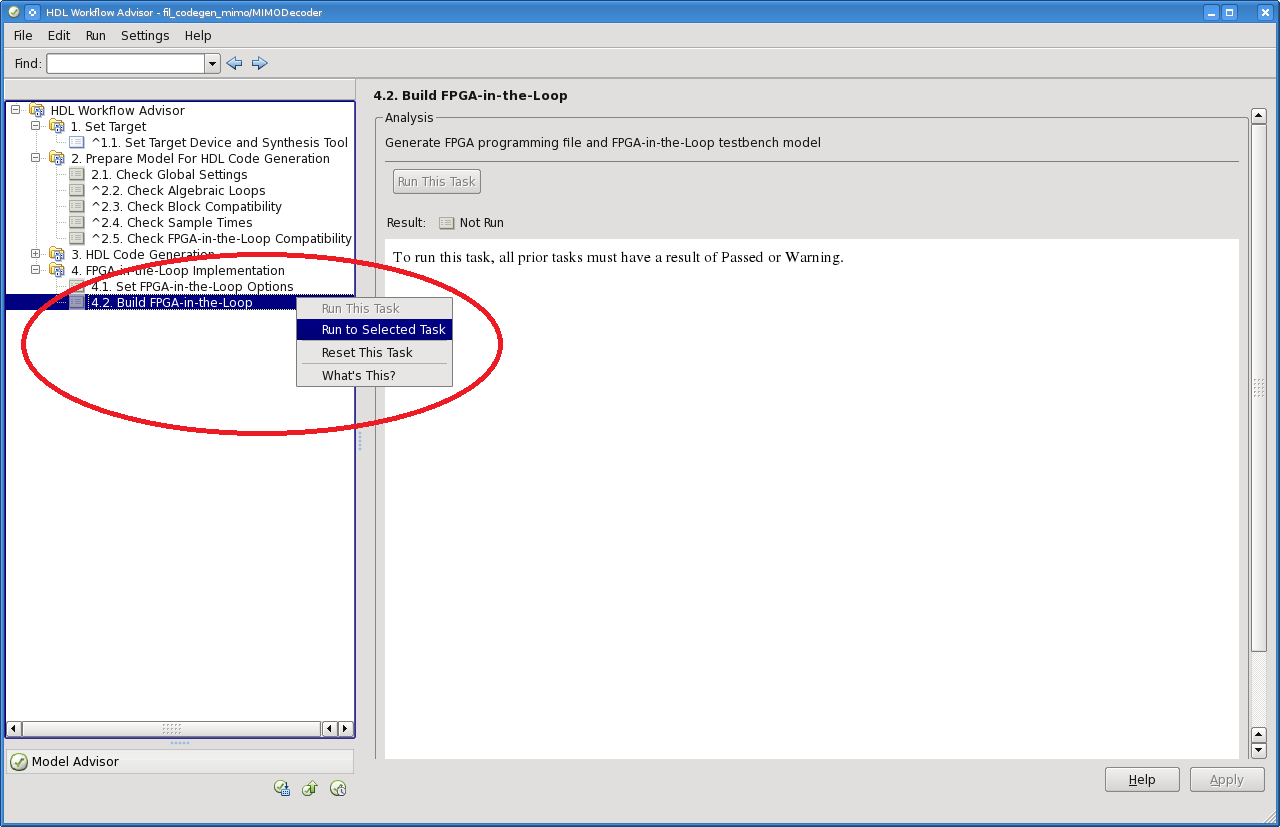

步骤4.2:右键单击左侧导航树中工作流的步骤4.2,然后选择“运行到此任务”。此步骤可能需要几分钟,因为它包括合成、映射和路由FPGA设备设计的步骤。

结果将是用于MIMO解码器子系统的FPGA在环仿真的FPGA编程文件,以及包含解码器原始模型(包括用于FSM的传统HDL)的新模型,以及环路块中的FPGA。它还将具有带有断言块的比较器,以识别与我们在协同模拟模型中看到的信号类似的不匹配信号。

4.用FPGA在环仿真验证设计

由于生成的验证模型包括FSM子系统的协同模拟,因此您需要使用HDL模拟器来运行整个FIL模型。确保关闭先前协同模拟的HDL模拟器,然后重新启动HDL模拟器。

在步骤3中生成的FPGA在环模型中,打开FIL块。

选择“加载”将FPGA编程文件下载到主板上的设备。

在Simulink模型中单击Play金宝app以运行FPGA在环仿真。

观察比较范围中的结果和模型中的错误率计算。FIL模拟结果应与参考模型完全匹配。

5.使用FIL向导进行FIL仿真

对于没有HDL编码器软件的用户,此步骤是步骤4的替代方法。如果已完成步骤4,则无需继续此步骤。

预生成的HDL文件位于“verify_legacy_gen_hdlsrc”文件夹中。您可以使用FIL向导为循环中的FPGA创建FPGA编程文件。FIL向导还将创建一个FIL块,您可以放弃该块,因为本例提供的FIL模型已经包含FIL块。

通过输入以下命令打开FIL向导:

电影向导

在里面fil选项从列表中选择您的FPGA开发板。

在源文件中选择添加并选择文件夹verify_legacy_gen_hdlsrc和identify中的所有文件mimodecoder.vhd.作为顶级文件。

接受向导其余选项的默认值

等待创建FIl块和FPGA编程文件。由于合成和路由FPGA实现所需的时间,这可能需要几分钟。

打开gm_fil_codegen_mimo_fil.slx模型,并将新生成的fil块拖动到所示位置的模型中。

打开FIL块掩码,单击信号属性选项卡。将每个rx_解码输出的数据类型更改为fixdt(1,6,0),以匹配行为块的数据类型。

打开FIL块掩码,单击主选项卡,选择加载并等待FPGA编程文件下载到设备。

在Simulink模型中按Play以金宝app在循环中运行FPGA。

观察比较范围中的结果和模型中的错误率计算。FIL模拟结果应与参考模型完全匹配。

本文总结了使用HDL协同模拟和FPGA在环验证HDL设计的示例。