包括驱动程序和监控在UVM测试台

本示例使用uvmbuild生成通用验证方法(UVM)测试台的功能,包括来自Simulink®设计和测试台的UVM驱动程序和监视器。金宝app

介绍

从基于帧的行为建模转换到Simulink中的标量建模需要转换块来转换信号采样时间和大小。金宝app转换块在这两个域中划分Simulink测试台。金宝app

基于帧的域:测试平台的一部分,作为帧对数据进行操作。

基于标量的域:作为标量操作和操作数据的测试平台的一部分。

UVM框架使用事务级建模来处理来自序列(刺激生成器)的事务,并在记分牌(检查器)中验证结果事务。

在将Simulink测试台转换为UVM金宝app测试台时,保持这些域的分离是很重要的。域分离支持测试平台组件更好的组件化和可重用性。

Simulink中的设计和测试金宝app

编写基于标量的算法,并在其周围添加测试台,使用转换子系统(例如,缓冲区和不缓解,速率转换或这些块的组合)将基于帧的域和标量域分开。该模型包括刺激生成子系统,被测标量的设计(DUT)和响应检查子系统。在刺激生成和DUT之间引入了额外的转换子系统,以将数据从帧转换为标量和DUT和响应检查器,以将数据从标量转换为帧。

该示例使用Simulink设计和测金宝app试一个流水线分割cordic算法,并确定给定数量的流水线阶段的最大错误阈值。在本设计中,对七个管道阶段进行了测试。

该设计在Simulink中包含两个采样时间。金宝app

慢的采样时间(绿色)是基于在DUT中测试的较低层次算法的高层次事务不可知来操作的。在这个例子中,事务由三个向量组成:分子、分母和cordic算法的除法结果。

快速采样时间(红色)是以标量计算的。管道DUT在红色采样时间对两个标量进行采样,当有效输出信号被断言时,经过7个红色采样时间后得到cordic分割结果。

vectorGengerator子系统产生不同的分子和分母矢量序列。矢量的大小和范围是定义的InitFcn在Simulink模型浏览器下金宝app的回调。

Vectortoscalar子系统将高级事务(向量)转换为DUT能够理解的标量序列。

ScalarToVector子系统根据它从DUT接收的标量序列组装结果向量。

DivideChecker子系统验证结果向量是否包含在某个错误阈值内的正确分割结果。如果错误大于阈值,则模拟输出警告。此外,DivideChecker子系统输出三个MAT文件,您可以通过绘图来可视化结果。

模型如下图所示:

打开并模拟模型。由于没有触发断言,因此不会存在错误阈值违规。

open_system (“drv_and_mon_uvmtb”);r = sim卡(“drv_and_mon_uvmtb”);

模拟将三个MAT文件写入磁盘:num.mat那den.mat,result_cordic.mat。这些文件分别包含Cordic部门的分母,分子和结果。

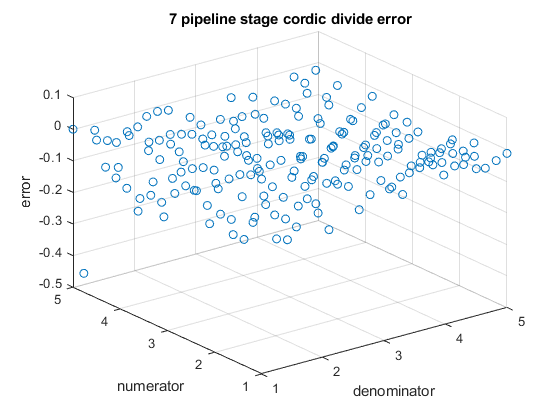

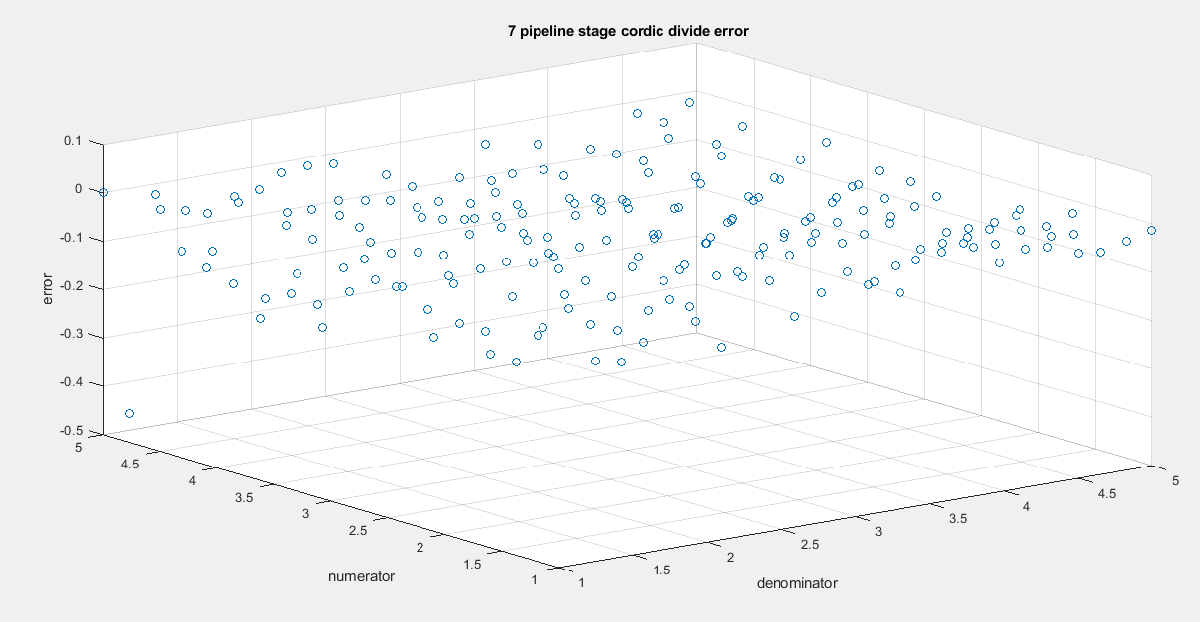

提供了一个MATLAB函数从MAT文件生成三维散点图。生成的图形有助于可视化误差,并进一步确认误差小于阈值。

plot_cordic_results ('num.mat'那“den.mat”那'结果_cordic.mat');

使用驱动程序和监视器生成UVM测试台

使用uvmbuild将设计导出到UVM环境并指定要映射到UVM驱动程序,监视器或两者的Simulink子系统。金宝app

UVM驱动程序和监视器使您能够区分基于框架的域和基于标量的域。当转换到UVM框架时,基于框架的域映射到UVM事务,而基于标量的域映射到时间感知的UVM组件(驱动程序、dut和监视器)。标准组件定义根据环境的各个部分在模拟中的角色将它们分开。对于这个示例:

VectorGenerator子系统被映射到UVM序列。

VectorToScalar子系统映射到UVM驱动。

Pipelined_Cordic_Divide子系统映射到DPI DUT SystemVerilog模块。

ScalarToVector子系统被映射到UVM监视器。

分割器子系统映射到UVM计分板。

要根据Simulink设计生成UVM测试台,请执行以下代码。金宝app

序列=“drv_and_mon_uvmtb / VectorGenerator”;司机=“drv_and_mon_uvmtb / VectorToScalar”;dpi_dut ='drv_and_mon_uvmtb / pipelined_cordic_divide';Moninor =.'drv_and_mon_uvmtb / scalartovector';记分板=“drv_and_mon_uvmtb / DivideChecker”;uvmbuild (dpi_dut序列,记分板,'司机',司机,“监控”, moninor);

###启动DPI子系统生成用于UVM测试台###启动建立过程为模型:Pipelined_Cordic_Divide ###开始的SystemVerilog DPI成分生成###生成DPIħ包装/ TMP / Bdoc21a_1606923_116573 / tp7ffdc2b8 / hdlverifier-ex46125948 / uvm_build / drv_and_mon_uvmtb_dpi_components/Pipelined_Cordic_Divide_build/Pipelined_Cordic_Divide_dpi.h ###生成DPI C包装/tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/Pipelined_Cordic_Divide_build/Pipelined_Cordic_Divide_dpi.c ###生成UVM模块封装/ TMP / Bdoc21a_1606923_116573 / tp7ffdc2b8 / hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/Pipelined_Cordic_Divide_build/Pipelined_Cordic_Divide_dpi_pkg.sv ###生成的SystemVerilog模块/tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/Pipelined_Cordic_Divide_build/Pipelined_Cordic_Divide_dpi.sv ###生成的makefile为:画中画elined_Cordic_Divide_dpi ###调用make来构建DPI共享库###的构建过程中成功完成了模型:Pipelined_Cordic_Divide制作摘要顶级车型的目标建:示范行动重建原因======================================================================================================== Pipelined_Cordic_Divide代码生成和编译的代码生成信息文件不存在。内置1款1(0型号已经是最新的)建立时间:对于模型0H0米25.063s ###开始构建过程:VectorGenerator ###开始的SystemVerilog DPI分量产生### DPI生成包装^ h的/ tmp / Bdoc21a_1606923_116573 /tp7ffdc2b8 / hdlverifier-ex46125948 / uvm_build / drv_and_mon_uvmtb_dpi_components / VectorGenerator_build / VectorGenerator_dpi.h ###生成DPI C包装/tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/VectorGenerator_build/VectorGenerator_dpi.c ###生成UVM模块封装/TMP / Bdoc21a_1606923_116573 / tp7ffdc2b8 / hdlverifier-ex46125948 / uvm_build / drv_and_mon_uvmtb_dpi_components / VectorGenerator_build / VectorGenerator_dpi_pkg.sv ###生成的SystemVerilog模块/tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/VectorGenerator_build/VectorGenerator_dpi.sv ###生成的生成文件为:VectorGenerator_dpi ###调用使构建dPI共享库###的模型的构建过程的顺利完成:VectorGenerator制作摘要顶级车型的目标建:示范行动重建原因================================================================================================ VectorGenerator代码生成和编译的代码生成信息文件不存在。 1 of 1 models built (0 models already up to date) Build duration: 0h 0m 12.471s ### Starting build procedure for model: VectorToScalar ### Starting SystemVerilog DPI Component Generation ### Generating DPI H Wrapper /tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/VectorToScalar_build/VectorToScalar_dpi.h ### Generating DPI C Wrapper /tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/VectorToScalar_build/VectorToScalar_dpi.c ### Generating UVM module package /tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/VectorToScalar_build/VectorToScalar_dpi_pkg.sv ### Generating SystemVerilog module /tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/VectorToScalar_build/VectorToScalar_dpi.sv ### Generating makefiles for: VectorToScalar_dpi ### Invoking make to build the DPI Shared Library ### Successful completion of build procedure for model: VectorToScalar Build Summary Top model targets built: Model Action Rebuild Reason =============================================================================================== VectorToScalar Code generated and compiled Code generation information file does not exist. 1 of 1 models built (0 models already up to date) Build duration: 0h 0m 10.362s ### Starting build procedure for model: ScalarToVector ### Starting SystemVerilog DPI Component Generation ### Generating DPI H Wrapper /tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/ScalarToVector_build/ScalarToVector_dpi.h ### Generating DPI C Wrapper /tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/ScalarToVector_build/ScalarToVector_dpi.c ### Generating UVM module package /tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/ScalarToVector_build/ScalarToVector_dpi_pkg.sv ### Generating SystemVerilog module /tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/ScalarToVector_build/ScalarToVector_dpi.sv ### Generating makefiles for: ScalarToVector_dpi ### Invoking make to build the DPI Shared Library ### Successful completion of build procedure for model: ScalarToVector Build Summary Top model targets built: Model Action Rebuild Reason =============================================================================================== ScalarToVector Code generated and compiled Code generation information file does not exist. 1 of 1 models built (0 models already up to date) Build duration: 0h 0m 8.7445s ### Starting build procedure for model: DivideChecker ### Starting SystemVerilog DPI Component Generation ### Generating DPI H Wrapper /tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/DivideChecker_build/DivideChecker_dpi.h ### Generating DPI C Wrapper /tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/DivideChecker_build/DivideChecker_dpi.c ### Generating UVM module package /tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/DivideChecker_build/DivideChecker_dpi_pkg.sv ### Generating SystemVerilog module /tmp/Bdoc21a_1606923_116573/tp7ffdc2b8/hdlverifier-ex46125948/uvm_build/drv_and_mon_uvmtb_dpi_components/DivideChecker_build/DivideChecker_dpi.sv ### Generating makefiles for: DivideChecker_dpi ### Invoking make to build the DPI Shared Library ### Successful completion of build procedure for model: DivideChecker Build Summary Top model targets built: Model Action Rebuild Reason ============================================================================================== DivideChecker Code generated and compiled Code generation information file does not exist. 1 of 1 models built (0 models already up to date) Build duration: 0h 0m 11.441s ### Starting UVM test bench generation for model: drv_and_mon_uvmtb ### Generating UVM transaction object ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/scoreboard/mw_Pipelined_Cordic_Divide_scoreboard_trans.sv ### Generating UVM interface ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/uvm_artifacts/mw_Pipelined_Cordic_Divide_if.sv ### Generating UVM sequence ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/sequence/mw_Pipelined_Cordic_Divide_sequence.sv ### Generating UVM sequence transaction ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/sequence/mw_Pipelined_Cordic_Divide_sequence_trans.sv ### Generating UVM driver ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/driver/mw_Pipelined_Cordic_Divide_driver.sv ### Generating UVM monitor ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/monitor/mw_Pipelined_Cordic_Divide_monitor.sv ### Generating UVM input monitor ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/uvm_artifacts/mw_Pipelined_Cordic_Divide_monitor_input.sv ### Generating UVM agent ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/uvm_artifacts/mw_Pipelined_Cordic_Divide_agent.sv ### Generating UVM scoreboard ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/scoreboard/mw_Pipelined_Cordic_Divide_scoreboard.sv ### Generating UVM scoreboard configuration object ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/scoreboard/mw_Pipelined_Cordic_Divide_scoreboard_cfg_obj.sv ### Generating UVM environment ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/uvm_artifacts/mw_Pipelined_Cordic_Divide_environment.sv ### Generating UVM test ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/uvm_artifacts/mw_Pipelined_Cordic_Divide_test.sv ### Generating UVM top ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/top/mw_Pipelined_Cordic_Divide_top.sv ### Generating UVM test package ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/top/drv_and_mon_uvmtb_pkg.sv ### Generating UVM test bench simulation script for Mentor Graphics QuestaSim/Modelsim ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/top/run_tb_mq.do ### Generating UVM test bench simulation script for Cadence Incisive ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/top/run_tb_incisive.sh ### Generating UVM test bench simulation script for Cadence Xcelium ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/top/run_tb_xcelium.sh ### Generating UVM test bench simulation script for Synopsys VCS ./uvm_build/drv_and_mon_uvmtb_uvm_testbench/top/run_tb_vcs.sh

如图所示,UVM驱动程序和监视器在不同的目录中生成。

运行UVM测试台

可以通过进入UVM测试台式顶部模块目录来执行生成的UVM测试台drv_and_mon_uvmtb_uvmbuild \ uvm_testbench \ top并执行一个生成的HDL模拟器脚本。本例使用ModelSim/QuestaSim®。图中显示了要执行的命令。

要确认UVM模拟与Simulink测试台匹配,请检查此要求。金宝app

没有抛出错误阈值违规。通过查看UVM模拟日志并检查是否存在UVM错误来验证。UVM仿真日志如图所示。

UVM记分板输出三个MAT文件(

num.mat那den.mat,result_cordic.mat),在UVM仿真的最后。从视觉上看,由Simulink设计生成的三维散点图必须与UVM仿真的图相匹配。金宝appUVM模拟MAT文件的绘图可以使用以下命令生成:

得到的UVM仿真三维散点图如图所示。图与前面几节中显示的Simulink设计图金宝app相匹配。

结论

在Simulink和UVM框架中保持基于框架和基于标量的行为建模分离会带来这些好处。金宝app

域分离使得能够在更高的抽象级别进行基于帧的事务处理的建模,而无需引入较低级别转换,该算法依赖于正在开发的算法。

VectorGenerator和DivideChecker子系统可以在不同的Simulink或UVM项目中重用,这些项目有不同的算法,但需要相同的高级事务金宝app生成和检查。

域分离使DUT算法具有多速率特性。

域分离使高级事务能够以不同的数据类型运行而不是DUT。在此示例中,DUT具有端口数据类型

UFX10_EN5.,但是vectorgegerator和DivifeChecker子系统是双数据类型。如果您有Simulink金宝app Test®,您可以选择映射在Simulink测试套件中的转换块到UVM驱动程序和监视器。域分离支持更加精简的UVM测试台生成工作流。

这uvmbuild函数允许您通过提供附加的可选名称-值对来指定映射到UVM驱动程序、监视器或两者的Simulink子系统,从而分离基于框架的域和标量域。金宝app