联系Xilinx Zynq®UltraScale+™RFSoC gigasample数据转换器,并在MATLAB中进行原生分析®和仿真软金宝app件®

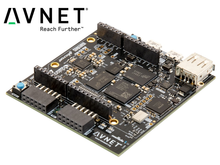

Xilinx SoC和FPGA器件的设计、分析和原型

在Xilinx fpga和Zynq soc上调试和测试HDL代码。

为RFSoC器件的FPGA部分生成代码

使用基于Xilinx zynq的硬件设计和原型视觉系统

这个支持包金宝app使您能够在Xilinx上部署深度学习处理器®基于FPGA和SoC的硬件来自MATLAB

学习如何使用MATLAB和Simulink部署算法到FPGA。金宝app

学习和评估HDL编码器的入门指南

最简单的生成方式”。文件从任何映像

程序最小化通过WiFi使用代码生成直接从Simulink。金宝app

用MATLAB应用程序控制LED闪烁的例子,使用MATLAB作为AXI Master从HDL验证器

在MATLAB环境中使用Xilinx ISIM进行RTL模块行为仿真

使用系统发生器的BFSK发射机10.1

CORDIC算法应用

用CORDIC计算三角函数(sin和cos)

Matlab代码用于Xilinx FPGA (Spartan, Virtex)的18k块RAM声明,使用VHDL或Verilog

BFSK收发器,使用SysGen 10.1