主要内容

HDL代码生成

从MATLAB生成HDL代码®和仿真软金宝app件®

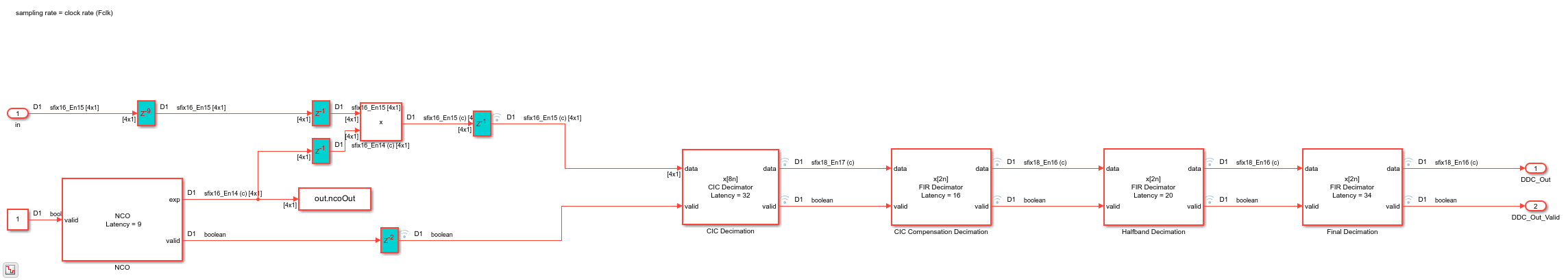

要在fpga或asic上实现DSP设计,您可以使用HDL Coder™或Filter design HDL Coder™。这两种产品下载188bet金宝搏都可生成可合成和可移植的VHDL®和Verilog®代码,并生成VHDL和Verilog测试台,用于快速模拟、测试和验证生成的代码。

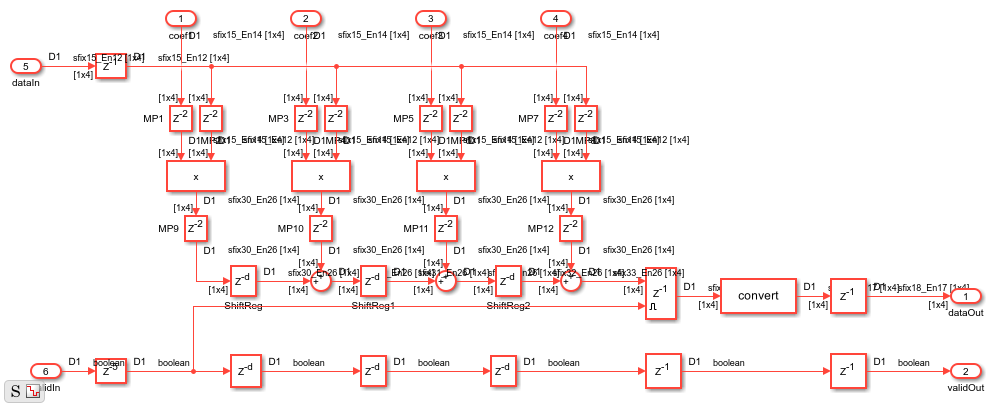

高密度脂蛋白编码器-从Simulink或MATLAB设计生成金宝app代码。这种支持包金宝app括过滤器、数学和信号操作,以及为资源使用和性能而优化的其他算法,如FFT HDL优化,传输线HDL优化,NCO HDL优化块。有关如何使用HDL Coder生成HDL代码的基本示例,请参见可编程FIR滤波器的FPGA.

滤波器设计HDL编码器-生成代码从MATLAB滤波器设计。您可以使用Generate HDL用户界面或使用命令行选项访问代码和测试台生成特性。这些特性也集成在Filter Designer应用程序中。有关如何使用Filter Design HDL Coder生成HDL代码的示例,请参见高密度脂蛋白巴特沃斯滤波器(Filter Design HDL编码器).

要在Simulink或MATLAB中调试设计,请使金宝app用逻辑分析仪波形查看器。

金宝app模型可视化工具

| 逻辑分析仪 | 可视化、测量和分析随时间变化的转换和状态 |

功能

generatehdl |

生成量化DSP滤波器的HDL代码(需要)滤波器设计HDL编码器) |

主题

在Simulink库浏览器和文档中过滤支持HD金宝appL代码生成的块。金宝app

生成过滤系统对象的HDL代码(Filter Design HDL编码器)

了解从筛选器System对象生成HDL代码的细节。

选择HDL代码生成参数来控制过滤架构中的速度和面积权衡。

选择资源共享和管道优化选项。

为HDL代码生成选择一个支持基于框架的输金宝app入的块。

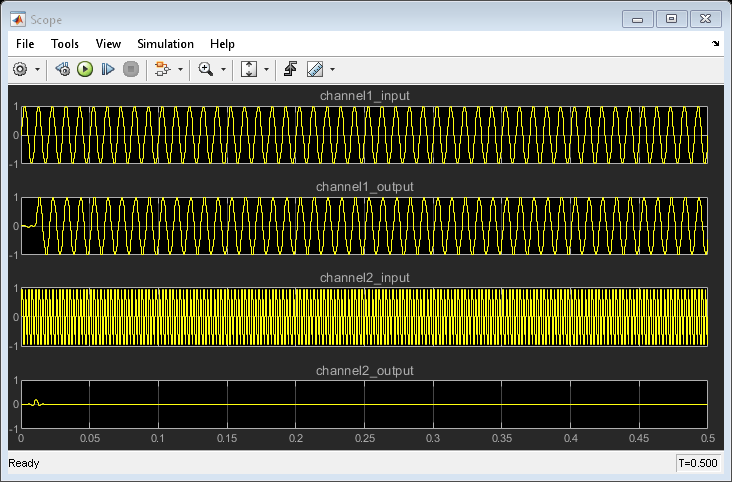

使用逻辑分析仪可视化可编程FIR滤波器的多个信号。