ISO 26262和IEC 61508的ASIC和FPGA工作流程

杰克·埃里克森Mathworks

概述了用于ISO 26262和IEC 61508的IEC认证工具包中的HDL代码生成和验证支持。金宝app

ISO 26262和IEC 61508的IEC认证工具包增加了工作流程和工件文档,用于将基于模型的功能安全设计与ASIC和FPGA实现连接起来。这包括来自TUV SUD的证书,证明HDL编码器符合ISO 26262对任何ASIL的要求,并已根据IEC 61508、IEC 62304、EN 50128和ISO 25119进行了适用性测试。

这个工作流程包括:

- 要求编写

- 体系结构建模

- 实现建模

- 在model Advisor中进行静态模型分析

- HDL代码生成

- 在每个步骤进行验证和验证,包括为下游RTL验证生成模型

该工具包还提供了用于管理和记录工作流步骤和工件的模板。如果在部署此过程中需要更广泛的支持,MathWorks提供了金宝appISO 26262过程部署咨询服务。

要了解更多关于MathWorks ISO 26262工作流的信息,请访问在MATLAB和Si金宝appmulink中支持ISO 26262金宝app。

从发行版2020a开始,HDL编码器已获得ISO 26262认证,包括ISO 26262和MathWorks IEC 61508的ASIL D. IEC认证工具包,已更新了基于模型的设计与FPGA和ASIC实现的连接的完整工作流程。

该工具包提供了工作流和工件来帮助您遵守——并证明您遵守——这些功能性安全标准。在HDL部分中,有一个来自TUV SUD的HDL编码器证书,以及他们的报告,解释了用于验证它的过程。

这不仅仅是HDL编码器。工具包中的工作流文档涵盖了从需求编写、体系结构建模到实现建模,再到HDL代码生成的整个过程,每个步骤都进行了验证和验证。

正如您所看到的,这个工作流的很大一部分是首先验证模型的行为是否符合需求,这包括将需求与模型和测试联系起来,并确保这些需求在测试中被完全覆盖。然后进入实现阶段,验证每个实现阶段生成的设计其功能与前一阶段相匹配。

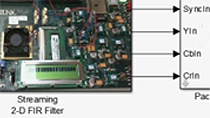

该工作流还提供了一些技术,帮助确保下游FPGA或ASIC实现的完整性。在生成HDL代码之前,使用Model Advisor运行特定于任务的检查。在这里,我将在我们的HDL教程设计上运行ISO检查,这是一个信号处理设计,在创建时没有考虑到认证,因此它应该能识别大量问题。

没有错误,这是好事,并且警告可以让您了解好的实践,以防止在这个级别上进行假设,从而导致后续的问题。其中一些应该在设计中解决,而另一些则涉及到工具设置,比如增加检查问题(如溢出)的严重性。

在验证下游实现方面,HDL验证器提供了许多方法来重用基于模型的设计工作。在这个流程图中显示的是在一个FPGA上运行您的设计,使用Simulink测试在循环中运行,并根据您的模型逐一检查结果。金宝app您还可以使用HDL验证器为下游仿真生成SystemVerilog验证组件,包括UVM。查看HDL验证器产品页面了解更多信息。

该工具包还展示了如何将手写代码集成到流程中,以及如何使用HDL验证器与您的模型一起验证它。

最后,该工具包提供了一个模板,您可以使用它来演示项目的一致性。它列出使用的标准,并提示您在流程中使用的相关信息。

MathWorks为您提供帮助和咨询,通过这些功能性安全工作流程来提高您的组织能力。工具包本身提供了一些很好的资源来帮助你开始。

相关产品下载188bet金宝搏

你也可以从以下列表中选择一个网站:

如何获得最佳的网站性能

选择中国网站(中文或英文)以获得最佳网站表现。其他MathWorks国家站点不适合来自您所在位置的访问。