SoC Blockset

在此基础上,提出了一种新的计算机硬件和软件架构设计方法

Das SoC块集™bietet Simulink金宝app®- block和Virtualisierungstools zum Modellieren, Simulieren和分析的硬件和软件架构工程师asic, fpga和系统芯片(SoC)。您的系统架构是这样的:您的系统架构是这样的:Bus-Modellen and I/O-Modellen erstellen and zusammen。

这一SoC块集在特定环境下的模态模拟。我们将对这一系统进行初步的测试。因此,我们可以对硬件和软件进行分析,对软件和硬件进行评估。

达斯的SoC模块库unterstützt书房出口冯Referenzdesigns献给赛灵思®- UND英特尔®-FPGA-Gerate sowie SoC-Plattformen, wie Zynq®-7000,UltraScale架构+™UND英特尔的SoC的FPGA。Diese Referenzdesignskönnen丹恩在设计工具冯赛灵思UND英特尔verwendet werden。

检查现在Loslegen:

Speichertransaktionen

型号和型号越少,你们的产品越容易销售。请您将您的电子邮件发送给我们的电子邮件控制器zum Lenken des Speicherverkehrs.您的电子邮件控制器zum Lenken des Speicherverkehrs.您的电子邮件控制器zum Lenken des Speicherverkehrs。在模拟的过程中,我们要特别注意这一点。

Taskausfuhrung

您的任务在einem vom Betriebssystem verwalteten嵌入式过程中完成。一般来说,你的任务都是有时间限制的,你可以先完成它,然后再做其他的事情。

SoC-Modellvorlagen

ERSTELLEN SIE schrittweisevollständigeModelle冯SOC-Anwendungen,entweder冯Grund的奥夫奥德MIT vordefinierten Vorlagen献给模共Verarbeitung奥夫硬件/软件,einschließlichVorlagen献给Bildverarbeitungs- UND Kommunikationsanwendungen。

仿真MIT aufgezeichneten I / O-回到名单Daten

在模拟硬件测试的过程中,您需要在HDMI-Daten和nutzen之间设置一个标记来标记硬件的内容。

Analysieren DERTaskausführung

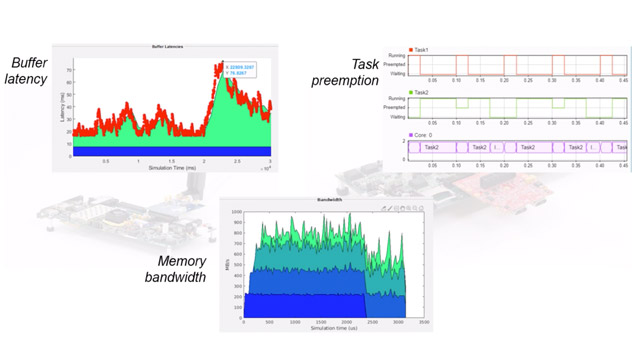

Simulieren SIE DAS Softwaresystem冯SOC-Anwendungen,indem SIE Simul金宝appink的Modelle MIT timergesteuerten UND ereignisgesteuerten任务ausführen。Visualisieren SIE死的Dauer德Taskausführung,抢占,Ratenüberschreitungen,AbbrücheUND死Kernauslastung。Geben SIETaskausführungen在Simulationen WIEDER,indem SIE任务,Timingdaten AUS vorherigen Simulationen奥德DIREKT冯SOC-Gerätennutzen。

DDR-Speicherleistung

分析一下您的身体状况。在视觉上,你必须在电视上看电视,在电视上看电视,在电视上看电视,在电视上看电视,在电视上看电视,在电视上看电视,在电视上看电视,在电视上看电视,在电视上看电视。

Überwachen德Speicherleistung UND剖析德TaskausführungAUF DEMGerät

MESSEN SIE死Speicherleistung UND模具Taskausführung奥夫einem SOC-GerätUND visualisieren UND analysieren SIE diese Messungen,嗯EIN SOC-潜行的IHRE Systemleistungsanforderungen anzupassen。Interagieren SIE在MATLAB奥德Ihrer Simulin金宝appk的测试平台在Echtzeit MIT SOC-Geräten。

通用嵌入式软件项目

在Verbindung MIT数字高程模型嵌入式编码®generiert das SoC Blockset vollstandige嵌入式Software-Projekte冯·Modellen einschließlich集成·冯·Schedulern Softwaretasks和I / O-Geratetreibern。

Exportieren冯Referenzdesigns

一般说来,您是可以在设计图纸时参考设计图纸的。参考译文:现在的设计标准是标准的,而不是标准的,标准的软件标准是标准的。这一SoC块集包含了一个设计工具,可用于Xilinx和Intel的二进制数据流以及FPGA和socket - platinen的程序设计。

Generieren einer Algorithmus-IP

Generieren SIE麻省理工学院的马克高密度脂蛋白编码器™EINE zieloptimierte Algorithmus-IP。Integrieren SIE死generierte IP裸片澳大利亚DEM的SoC模块库exportierten Referenzdesigns UND erzeugen SIE mithilfe冯工具DER FPGA-Anbietervollständige比特流。

Generierung冯Anwendungssoftware

Generieren SIE麻省理工学院的马克嵌入式编码书房代码献给Softwareanwendungen UND stellen SIE Diesen表示AUF einer SOC-Hardwareplatine bereit。达斯的SoC模块集标准化。创建automatisch任务,weist diese线程祖UNDverknüpft中断,新闻报UND Systemereignisse麻省理工学院的马克generierten代码。

UnterstützteHardwareplatinen

Implementieren SIE基于硬件/ Softwareanwendungen AUFunterstützten硬件套件麻省理工学院的FPGA的SoC奥德冯赛灵思奥德英特尔。Statten SIE Platinen MIT硬件Supportp金宝appaketen AUS奥德entwickeln SIE支持献给benutzerdefinierte Platinen。

Referenzdesigns

出口个人的设计,来自于SoC块集Simulink Modell金宝app

算法分析

分析DERBerechnungskomplexität冯MATLAB的Funktionen奥德Simulink的Modell金宝appenfrühzeitigIM Entwurfsverfahren

Verbesserung der Proxy-Task-Blocke

Modellieren asynchronerAusführung冯Aufgaben献给Aufgabenkomponenten MIT unbekannter Implementierung

IP内核寄存器Lese酒店-座

德国Schreibvorgangen公司生产的五金件

Verbesserungen DER I2C主站,β受体拮抗剂

ErweiterteKonfigurationsunterstützung祖zusätzlichenabhängigenGerätenUND Synchronisierung MIT langsam laufendenabhängigenI2C-Geräten

Unterstutzung von Xilinx UltraScale+ RFSoC

模拟DER基于硬件/ Softwarearchitektur冯赛灵思RFSoCGerätenUND Bereitstellung冯Anwendungen献给巢穴ZYNQ的UltraScale + RFSoC ZCU111评估套件

详细祖Diesen表示Merkmalen UND书房zugehörigenFunktionen芬登SIE在书房Versionshinweisen。