主要内容

通用CRC发电机HDL优化

生成CRC码位并将其附加到输入数据中

- 库:

通信工具箱HDL支持/错误检测和校正/ CRC金宝app

通信工具箱/错误检测和纠正/ CRC

描述

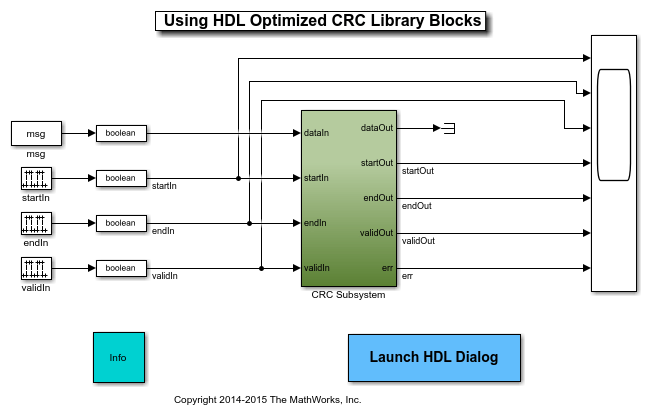

的通用CRC发电机HDL优化块,类似于一般CRC发电机块,生成循环冗余校验(CRC)校验和,并将其附加到输入消息。的通用CRC发电机HDL优化块处理为HDL代码生成进行了优化。该块不是一次处理整个帧,而是接受并返回一个带有控制信号的数据样本流。控制信号表明样本的有效性和帧的边界。为了实现更高的吞吐量,该块接受高达CRC长度的矢量数据,并实现并行架构。

港口

输入

输出

参数

模型的例子

算法

参考资料

[1] Campobello,G.,G.凯顿和M. Russo。“并行CRC实现。”IEEE计算机汇刊52岁的没有。10(十月2003):1312-19。https://doi.org/10.1109/TC.2003.1234528。

扩展功能

在R2012A介绍