数字下变频滤波器链的HDL实现

这个例子展示了如何使用DSP系统工具箱™和定点设计器™来设计一个三级、多速率、定点滤波器,实现了数字下转换器(DDC)的滤波器链,以满足全球移动系统(GSM)规范。

使用Filter Design HDL Coder™,我们将为相同的三级、多速率、定点滤波器生成可合成的HDL代码。最后,使用Simulink®和金宝appHDL Verifier™MS,我们将共同模拟定点过滤器,以验证生成的HDL代码产生与等效的Simulink行为模型相同的结果。

数字变频技术

数字下变频(DDC)是数字无线电的重要组成部分。DDC执行必要的频率转换,将数字无线电中的高输入采样率转换为更低的采样率,以便进一步和更容易处理。在本例中,DDC工作在大约70 MHz,必须将速率降低到270 KHz。

为了进一步约束我们的问题,我们将在Graychip的GC4016多标准四元DDC芯片中建模其中一个DDC。除其他功能外,GC4016提供了以下滤波器:具有可编程抽取因子(8-4096)的五级CIC滤波器;一个21抽头FIR滤波器,以2为十进制,并具有可编程的16位系数;以及一个63抽头FIR滤波器,它也可按2进行十进制运算,并具有可编程的16位系数。

DDC由一个数字控制振荡器(NCO)和一个混频器组成,以正交下转换输入信号到基带。基带信号然后通过级联积分器梳状滤波器(CIC)和两个FIR抽取滤波器进行低通滤波,以实现约270khz的低采样率,以便进一步处理。最后阶段通常包括一个重采样器,它对信号进行插值或抽取,以根据应用程序实现所需的采样率。再采样器还可以实现进一步的滤波。典型DDC的框图如下所示。

本例主要讨论三级、多速率抽取滤波器,它由CIC和两个抽取FIR滤波器组成。

GSM规范

感兴趣的GSM带宽是160 KHz。因此,DDC的三级多速率滤波器响应必须在此带宽上平坦到通带纹波以内,峰值到峰值的纹波必须小于0.1 dB。查看如下所示的GSM带外抑制掩模,我们看到滤波器也必须在100 KHz时实现18 dB的衰减。

此外,GSM需要270.833 Ksps的符号速率。由于Graychip的输入采样率与其时钟频率69.333 MHz相同,因此我们必须将输入采样降至270.833 KHz。这要求三阶段,多速率滤波器十进制256。

级联积分器梳状(CIC)滤波器

CIC滤波器是非常有用的多速率滤波器,因为它们可以实现高抽取(或插值)速率,并且无需乘法器即可实现。cic是简单的箱车滤波器,通过上采样器或下采样器递归级联实现。这些特性使得cic对于高速运行的数字系统非常有用,特别是当这些系统要在asic或fpga中实现时。

尽管cic具有理想的特性,但它们也有一些缺点,最显著的事实是,由于它们的类正弦响应,它们会在通带区域引起衰减。由于这个原因,CICs通常必须跟随一个补偿滤波器。补偿滤波器必须在通带区域具有逆正弦响应,以消除由CIC引起的下垂。

三个过滤器的设计和级联可以通过图形用户界面过滤器设计器来执行,

但是我们将使用命令行功能。

我们对CIC的定义如下:

R = 64;抽取因子D = 1;延迟百分比Nsecs = 5;%分段数猫头鹰= 20;输出字长%Cic = dsp。CICDecimator (“DecimationFactor”R“NumSections”Nsecs,...“FixedPointDataType”,“最小节字长度”,...“OutputWordLength”OWL);

我们可以通过调用info方法查看CIC的详细信息。

信息(cic)

ans = 9x56 char数组的离散时间FIR多速率滤波器(实)“-----------------------------------------”“滤波器结构:级联积分器-梳状抽取器”“抽取因子:64”“差分延迟:1”“节数:5”“稳定:是”“线性相位:是(类型2)”' ' '

让我们绘制和分析CIC滤波器的理论幅度响应,它将在69.333 MHz的输入速率下工作。

Fs_in = 69.333e6;FVT = fvtool(cic,“Fs”, Fs_in);fvt。颜色=“白色”;

首先要注意的是CIC滤波器有一个巨大的通带增益,这是由于结构内的添加和反馈。我们可以在FVTool中使用相应的设置来规范化CIC的震级响应。将CIC滤波器响应归一化,使其在直流处具有0 dB增益,将更容易分析下一级滤波器的叠加滤波器响应。

fvt。NormalizeMagnitudeto1 =“上”;

另一件需要注意的事情是,放大通带区域,我们看到CIC在80 KHz时有大约-0.4 dB的衰减(下垂),这在感兴趣的带宽范围内。CIC滤波器本质上是箱车滤波器的级联,因此有一个类似sinc的响应,导致下垂。这个下垂需要由FIR滤波器在下一阶段进行补偿。

轴([0.1 -0.8 0]);

补偿FIR抽取器

我们的DDC滤波器链的第二阶段需要补偿由CIC引起的通带下垂,并抽取2。由于CIC具有类似sinc的响应,我们可以用在通带中具有逆sinc响应的低通滤波器来补偿下垂。该滤波器将以输入采样率69.333 MHz的1/64工作,因此其速率为1.0833MHz。我们不再从头设计一个带逆sinc通带响应的低通滤波器,而是使用一个封闭函数,它可以让我们直接设计一个带CIC补偿(逆sinc)响应的decimator。

过滤器规格Fs = 1.0833e6;采样频率69.333MHz/64Apass = 0.01;% dBstop = 70;% dBFpass = 80e3;% Hz通带边缘频率Fstop = 293e3;% Hz阻带边频率%设计抽取滤波器。D和Nsecs在上面定义为分别为延迟百分比和分段数。补偿器= dsp。CICCompensationDecimator (“SampleRate”Fs,...“CICRateChangeFactor”R“CICNumSections”Nsecs,...“CICDifferentialDelay”D“PassbandFrequency”成就,...“StopbandFrequency”Fstop,“PassbandRipple”apas,...“StopbandAttenuation”, Astop);现在我们必须定义多速率过滤器的定点属性。默认情况下,累加器和乘法器的定点属性%的设置,以确保使用全精度算法,即no%量子化发生。缺省情况下,使用16位表示%过滤器系数。因为这是我们在这个例子中想要的,所以没有变化默认值中的%是必需的。

使用info命令,我们可以得到FIR补偿滤波器的全面报告,包括累加器和积的字长,这是自动确定的。

信息(补偿器)

ans = 10x56 char array '离散时间FIR多速率滤波器(实)“-----------------------------------------”“滤波器结构:直接形式FIR多相抽取器”“抽取因子:2”“多相长度:11”“滤波器长度:21”“稳定:是”“线性相位:是(类型1)”' ' ' '算术:double '

用逆sinc滤波器级联CIC,我们可以看到我们是否消除了由CIC引起的通带下垂。

cicCompCascade = cascade(cic,补偿器);fvt = fvtool(cic,补偿器,cicCompCascade,“Fs”(Fs_in Fs_in / 64, Fs_in]);fvt。颜色=“白色”;fvt。NormalizeMagnitudeto1 =“上”;轴([0.1 -0.8 0.8]);传奇(fvt“中投”,“补偿”,“级联”);

正如我们在两个滤波器级联的滤波器响应中所看到的,这是在CIC响应和补偿FIR响应之间,通带下垂已被消除。

第三阶段FIR抽取器

如前所述,GSM频谱掩模在100 KHz时需要18 dB的衰减。因此,对于我们的第三阶段和最后阶段,我们可以尝试一个简单的等纹波低通滤波器。同样,我们需要将系数量化为16位(默认值)。这个过滤器也需要抽取2。

N = 62;% 63次Fs = 541666;% 541.666千赫Fpass = 80e3;Fstop = 100e3;Spec = fdesign.decimator(2,低通滤波器的,“N, Fp,置”、N、成就、Fstop, Fs);给通带更多的权重Decimator =设计(规格,“equiripple”,“Wpass”2,“SystemObject”,真正的);

在默认情况下定义多速率过滤器时,累加器字大小自动确定,以保持完整的精度。但是,因为我们只有20位的输出,所以我们将输出格式设置为字长为20位,分数长度为-12。首先,我们必须将FullPrecisionOverride属性的默认值从true更改为false。

杀害多人者。FullPrecisionOverride = false;杀害多人者。OutputDataType =“自定义”;杀害多人者。RoundingMethod =“最近的”;杀害多人者。OverflowAction =“饱和”;杀害多人者。CustomOutputDataType = numerictype([],20,-12);

我们可以使用info方法查看筛选器的详细信息。

信息(杀害多人者)

ans = 10x56 char array '离散时间FIR多速率滤波器(实)“-----------------------------------------”“滤波器结构:直接形式FIR多相抽取器”“抽取因子:2”“多相长度:32”“滤波器长度:63”“稳定:是”“线性相位:是(类型1)”' ' ' '算术:double '

多级多速率DDC滤波器链

现在我们已经设计并量化了三个滤波器,我们可以通过级联归一化CIC和两个FIR滤波器得到总体滤波器响应。同样,我们使用归一化幅度来确保级联滤波器响应归一化到0 dB。

DDC =级联(cic,补偿器,decimator);FVT = fvtool(ddc,“Fs”, Fs_in);fvt。颜色=“白色”;fvt。NormalizeMagnitudeto1 =“上”;fvt。积分数= 8192*3;轴([0 1 -200 10]);%的放大

要查看整体滤波器响应是否符合GSM规范,我们可以在滤波器响应上覆盖GSM频谱掩码。

drawgsmmask;

我们可以看到,我们的整体滤波器响应是在GSM频谱掩模的限制范围内。我们还需要确保通带纹波满足峰值间小于0.1 dB的要求。我们可以通过使用axis命令放大来验证这一点。

轴([0.09 -0.08 0.08]);

实际上,通带纹波远低于0.1 dB的峰值到峰值GSM要求。

生成VHDL代码

Filter Designer还支持从下面金宝app所示的对话框生成HDL代码。

从Filter Designer以及命令行中,您可以生成VHDL或Verilog代码以及VHDL或Verilog文件中的测试工作台。此外,您还可以通过指定许多选项来定制生成的HDL代码,以满足您的编码标准和指南。

但是,在这里我们将使用命令行功能来生成HDL代码。

现在,我们有了满足规格的定点、三级、多速率过滤器,我们就可以生成HDL代码了。

级联的CIC和两个FIR滤波器并生成VHDL。

为了避免量化来自混合器的定点数据,混合器的字长为20位,分数长为18位(S20,18),我们将CIC的输入字长和分数长设置为相同的值S20,18。

%hcas = cascade(hcic, hcir, hpir);Workingdir = tempname;inT =数值类型(1,20,18);generatehdl(监护系统“InputDataType”inT,...“名字”,“过滤”,“开发”,硬件描述语言(VHDL)的,...“TargetDirectory”fullfile (workingdir“hdlsrc”));

###启动过滤器的VHDL代码生成过程:filter ### Cascade stage ###启动过滤器的VHDL代码生成过程:filter_stage1 ###生成:/tmp/Bdoc21a_1606923_234308/tp4e2110c0_b9d4_41ad_9eb1_3fc2c664ec16/hdlsrc/filter_stage1。vhd < / > # # # # # #开始代filter_stage1 VHDL的实体开始代filter_stage1硬件描述语言(VHDL)架构# # # # 1:部分积分器# # # # 2:部分积分器# # # # 3:部分积分器# # # # 4:部分积分器# # # # 5:部分积分器# # # # 6节:梳子# # # # 7节:梳子# # # # 8节:梳子# # # # 9节:梳子# # # # 10节:梳子# # #成功完成硬件描述语言(VHDL)过滤器的代码生成过程:生成:/tmp/Bdoc21a_1606923_234308/tp4e2110c0_b9d4_41ad_9eb1_3fc2c664ec16/hdlsrc/filter_stage2. vhd。vhd ###开始生成filter_stage2 VHDL实体###开始生成filter_stage2 VHDL架构###成功完成过滤器的VHDL代码生成过程:filter_stage2级联阶段# 3 ###启动过滤器的VHDL代码生成过程:filter_stage3 ###生成:< a href = " matlab:编辑(“/ tmp / Bdoc21a_1606923_234308 / tp4e2110c0_b9d4_41ad_9eb1_3fc2c664ec16 hdlsrc / filter_stage3.vhd ') " > / tmp / Bdoc21a_1606923_234308 / tp4e2110c0_b9d4_41ad_9eb1_3fc2c664ec16 hdlsrc / filter_stage3。vhd ###开始生成filter_stage3 VHDL实体###开始生成filter_stage3 VHDL架构###成功完成VHDL代码生成过程的过滤器:filter_stage3 ###生成:/tmp/Bdoc21a_1606923_234308/tp4e2110c0_b9d4_41ad_9eb1_3fc2c664ec16/hdlsrc/filter. vhd') /Bdoc21a_1606923_234308/tp4e2110c0_b9d4_41ad_9eb1_3fc2c664ec16/hdlsrc/filter.vhd'vhd ###开始生成过滤器VHDL实体###开始生成过滤器VHDL架构###成功完成过滤器VHDL代码生成过程:过滤器### HDL延迟为2个样本

在Simulink中HDL与ModelSim的联合仿真金宝app

为了验证生成的HDL代码产生的结果与我们的Simulink模型相同,我们将使用HDL Verifier MS在Simulink中共同模拟我们的HDL代金宝app码。我们有一个预先构建的Simulink模型金宝app,其中包括两条信号路径。一个信号路径产生三阶段多速率滤波器的Simulin金宝appk行为模型结果。另一条路径使用ModelSim®生成模拟结果,即我们生成的VHDL代码。

open_system (“ddcfilterchaindemo_cosim”);

通过双击Simulink模型中的按钮来启动ModelSim。金宝app注意,ModelSim必须安装在系统路径上。ModelSim将自动编译HDL代码,初始化模拟并打开Wave查看器。

当ModelSim准备就绪时,运行Simulink模型。金宝app这将与ModelSim一起执行联合仿真,并自动打开Time Scope以查看结果。

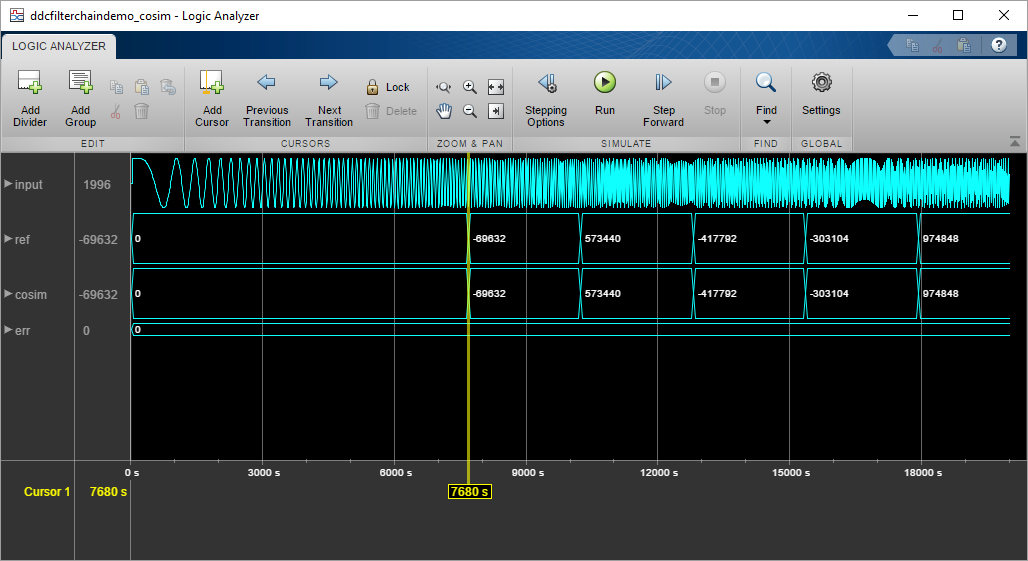

使用Logic Analyzer查看结果。

验证结果

顶部的轨迹是激励啁啾信号。下一个标记为“ref”的信号是三级多速率滤波器的Simulink行为模型产生的参考信号。金宝app作用域上标记为“cosim”的底部轨迹是生成的三级多速率滤波器HDL代码的ModelSim仿真结果。最后一个痕迹显示了Simulink的行为模型结果和ModelSim对HDL代码金宝app的模拟之间的误差。

总结

我们使用几个MathWorks™产品来设计和分析用于G下载188bet金宝搏SM应用的DDC的三级、多速率、定点滤波器链。然后我们生成HDL代码来实现过滤器,并通过比较Simulink的行为模型和ModelSim中通过HDL Verifier MS模拟的HDL代码来验证生成的代码。金宝app