HDL Code Generation

To implement a DSP design on FPGAs or ASICs, you can use either HDL Coder™ or Filter Design HDL Coder™. Both products generate synthesizable and portable VHDL®和Verilog®code, and also generate VHDL and Verilog test benches for quickly simulating, testing, and verifying the generated code.

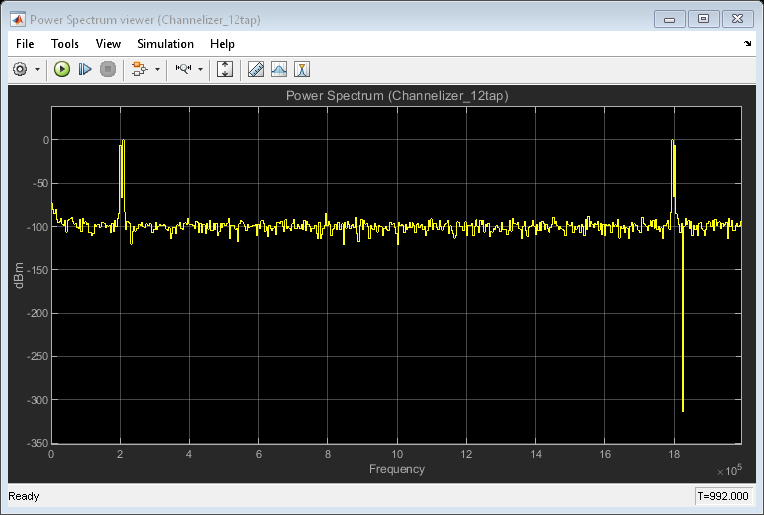

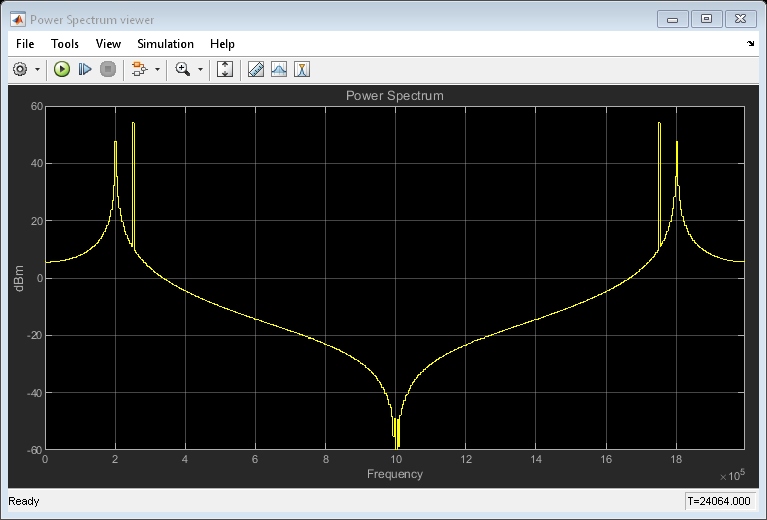

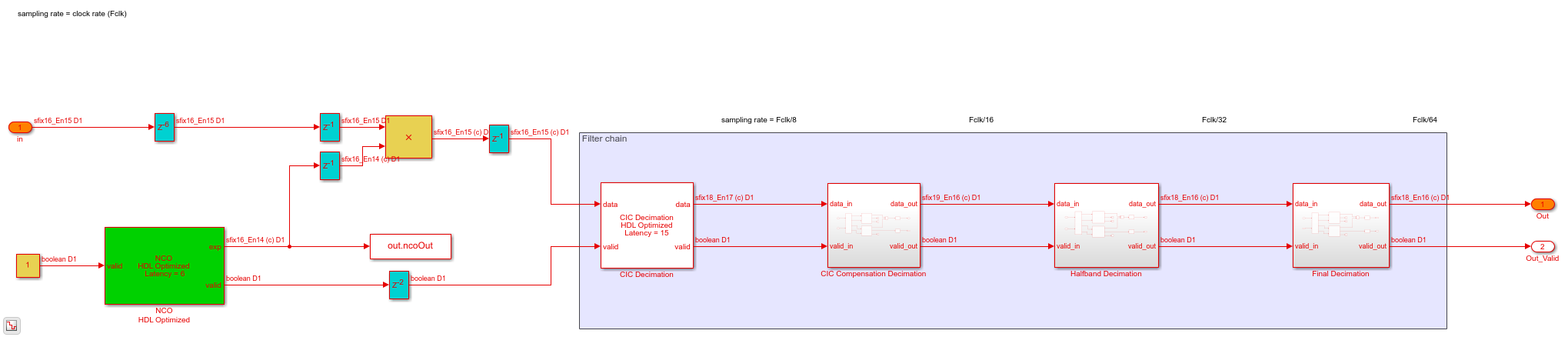

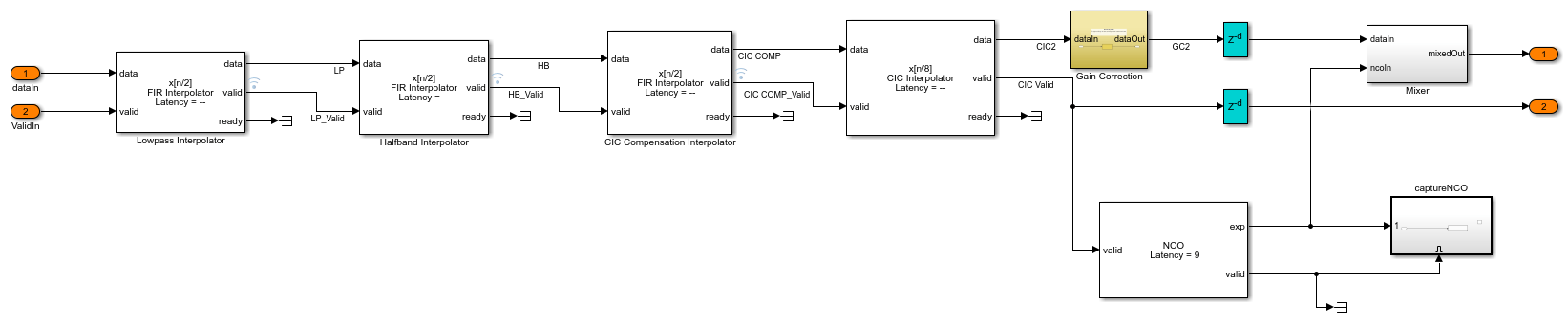

HDL Coder- 从Simulink或MATLAB设计生金宝app成代码。此支持包括金宝app过滤器,数学和信号操作以及针对资源使用和性能优化的其他算法,例如FFT HDL Optimized,IFFT HDL Optimized, 和NCO HDL Optimizedblocks. For a basic example of how to generate HDL code using HDL Coder, seeProgrammable FIR Filter for FPGA.

Filter Design HDL Coder— Generate code from MATLAB filter designs. You can access code and test bench generation features using the Generate HDL user interface, or by using command-line options. These features are also integrated with the Filter Designer app. For an example of how to generate HDL code using Filter Design HDL Coder, seeHDL Butterworth过滤器(过滤器设计HDL编码器).

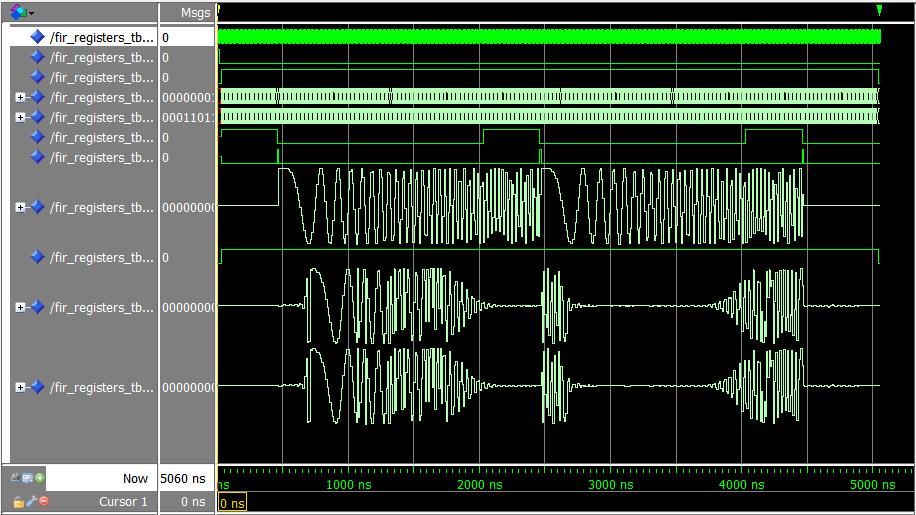

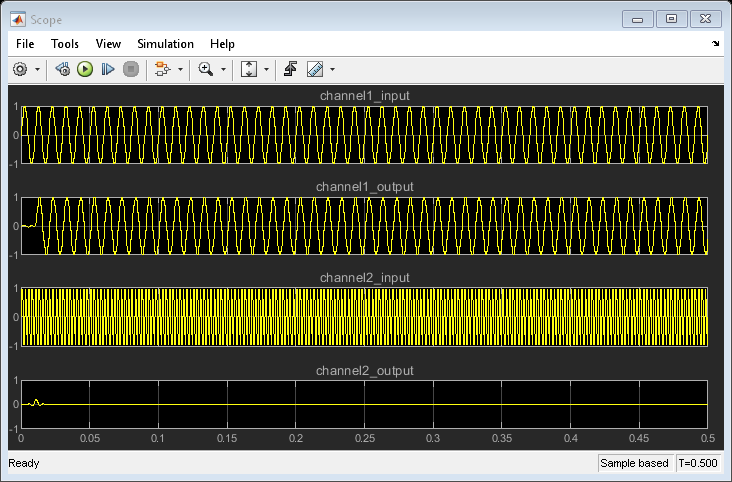

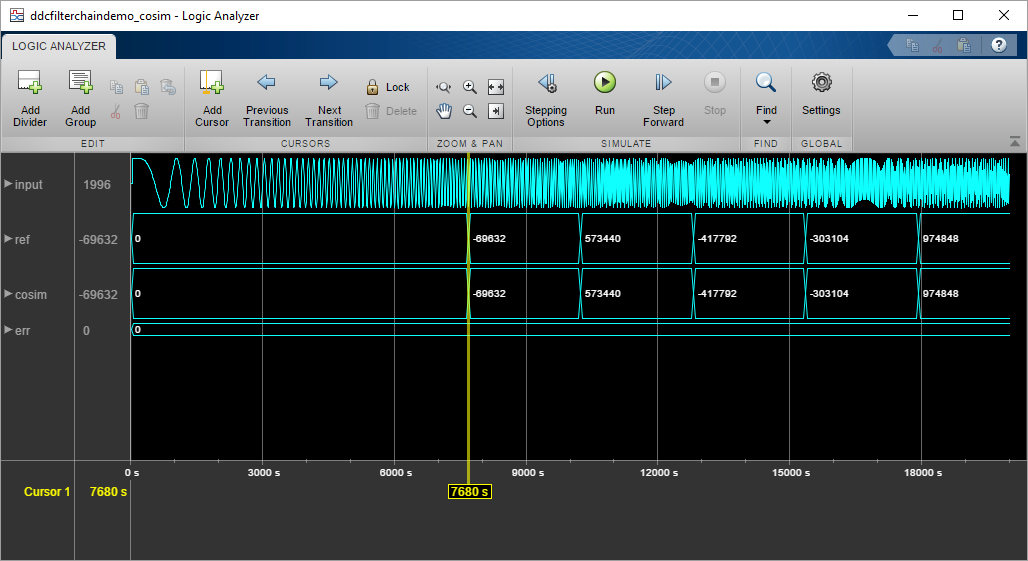

要在Simulink或Matlab中调试您的设计,金宝app请使用逻辑分析仪波形查看器。

金宝app模拟可视化工具

| 逻辑分析仪 | Visualize, measure, and analyze transitions and states over time |

Functions

GenerateHDL |

Generate HDL code for quantized DSP filter (requiresFilter Design HDL Coder) |

Topics

Find Blocks That Support HDL Code Generation

滤波器的过滤器,该块支持Simulink库浏览金宝app器和文档中的HDL代码生成。金宝app

Generate HDL Code for Filter System Objects(过滤器设计HDL编码器)

从过滤系统对象了解HDL代码生成的细节。

Select HDL code generation parameters to control speed vs. area tradeoffs in filter architectures.

Subsystem Optimizations for Filters

Select resource sharing and pipeline optimization options.

High Throughput HDL Algorithms

选择一个支持HDL代码生成基于帧的输入的金宝app块。

Visualize multiple signals of a programmable FIR filter by using a logic analyzer.