使用Zynq Board在实时音频输入上运行音频滤波器

This example shows how to model an audio system and implement it on a Zynq® board using an audio reference design.

Introduction

在这个例子中,你:

Model an audio system with Low pass, Band pass and High pass filters

使用音频参考设计在zynq板上实现它

The objective of this example is to receive audio input through Zedboard or Zybo board's line input, process it on the FPGA and transmit the processed audio to a speaker. The above figure shows the high-level architecture of such a system. It uses an audio codec to interface to the peripherals and to convert analog to digital signals and vice-versa. The Audio Codec IPs are used to configure the audio codec and for transferring audio data between Zynq Soc and audio codec. The Filter IP is used for audio processing. ARM processor is used to control the type of filter to be used i.e. low pass, band pass or high pass.

在你开始之前

To run this example, you must have the following software and hardware installed and set up:

HDL编码器Support Package for Xilinx Zynq Platform

Xilinx Zynq平台的嵌金宝app入式编码器支持包

Xilinx Vivado版本2019.1

Zedboard或Zybo Board

要设置Zedboard Lob,请参阅设置Zynq硬件和工具章节Getting Started with Targeting Xilinx Zynq Platform例。从移动或MP3播放器连接音频输入线路jack and either earphones or speakers toHPHO出来如下所示的Zedboard上的插孔。类似的设置可以在Zybo板上完成。对于Zybo Board设置,请参阅设置Zybo Board章节定义自定义板和Zynq工作流程的参考设计例。

Introduction

在以下模型中,音频文件用作DUT子系统的输入,Audio_Filter.。在Simulink中模拟此模型,可以通过处理后的音频效果金宝appAudio Device Writer块频谱分析仪块显示滤波音频输出的频谱图。

modelname =.'hdlcoder_audio_filter_biquad';Open_System(ModelName);

模型具有低通,带通和高通滤波器的系统

可以使用MATLAB®功能或在Simulink®中生成滤波器系数。金宝app在此模型中,FilterDesigner工具用于为每种类型的滤波器生成滤波器系数。然后将这些滤波器系数导出并作为MATLAB文件存储。这些系数将用于在Simulink中设计过滤器。金宝app在该模型中,根据相应的滤波器系数,来自Simulink的离散IIR滤波器块用作各种频带,带通或金宝app高通滤波器。

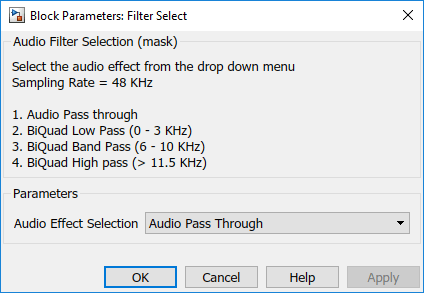

您可以通过在Simulink中模拟模型来测试此模型。金宝app在频谱分析仪上看到的频率范围和通过音频设备编写器块听到的音频效果应根据所选滤波器的类型而变化。过滤器选择块用于选择要在音频输入上完成的过滤类型。

自定义Zynq Board的模型

为了在Zedboard上实现此模型,您必须首先在Vivado中创建参考设计,该参考设计在Zedboard上接收音频输入,并将处理后的音频数据传输出ZedBoard。有关如何创建参考设计的详细信息,该设计集成了音频过滤器模型,请参阅创作Zynq板上的音频系统参考设计例。

For Zybo board, refer to创作Zybo板上的音频系统参考设计。

在参考设计中,左和右声道音频数据组合在一起以形成单个通道。它们被连接,使得较低的24位是左声道,上部24位是右声道。在上面所示的S金宝appimulink模型中,Data_in被分成2个通道即,因此左右。它们的幅度除以2,并且将2个通道添加在一起以形成单个通道。过滤在此频道上完成。

data_in.andvigw_in.是AXI4流信号。要了解如何使用AXI4-Stream接口,请参阅具有简化流式协议的模型流算法section in在Zynq工作流程中使用AXI4-Stream接口入门例。data_in.包含要处理的音频数据和vigw_in.acts as the enable signal. Each filter is mapped to an LED on Zedboard or Zybo board to visually indicate whether the filter is on or off.

filterselect.输入通过AXI4 Lite接口控制。

使用AXI4-Stream接口生成HDL IP核心

接下来,您可以启动HDL Workflow Advisor并使用Zynq硬件 - 软件共同设计工作流程来部署Zynq硬件上的此设计。有关更详细的逐步指南,您可以参考Getting Started with Targeting Xilinx Zynq Platform例。

1.使用MATLAB命令窗口中的以下命令设置Xilinx Vivado Synthesis Tool Path。运行命令时使用自己的Vivado安装路径。

hdl setuptoolpath('toolname'那'Xilinx Vivado'那'工具路径'那'C:\ Xilinx \ Vivado \ 2019.1 \ Bin \ Vivado.bat');

2。使用以下命令将IP存储库文件夹和zedboard文件夹和zedboard注册文件添加到MATLAB路径:

AddPath(FullFile(MatlaBroot,'toolbox'那'hdlcoder'那'hdlcoderdemos'那'监视'那'ipcore'));AddPath(FullFile(MatlaBroot,'toolbox'那'hdlcoder'那'hdlcoderdemos'那'监视'那'zedboard'));

对于Zybo Board使用以下命令。

AddPath(FullFile(MatlaBroot,'toolbox'那'hdlcoder'那'hdlcoderdemos'那'监视'那'ipcore'));AddPath(FullFile(MatlaBroot,'toolbox'那'hdlcoder'那'hdlcoderdemos'那'监视'那'ZYBO'));

3.从DUT子系统启动HDL工作流程顾问,hdlcoder_audio_filter_biquad / audio_filter.或者通过双击模型中的启动HDL工作流程顾问框。

目标接口设置已保存在此示例模型中为Zedboard,因此任务1.1至1.3中的设置会自动加载。要了解有关在模型中保存目标接口设置的更多信息,可以参考在型号中保存目标硬件设置例。

在任务1.1中,IP核心生成is selected for目标工作流程那andZedboard.is selected forTarget platform。If you are using Zybo board then selectZYBO如Target Platform而不是zedboard。

在任务1.2中,带AXI4流接口的音频系统is selected for参考设计。

AXI4流接口用于在参考设计和过滤算法IP之间传输音频数据。AXI4-Stream接口包含数据(Data)和控制信号,如数据有效(有效), back pressure (准备), and data boundary (Tlast.)。至少Dataand有效signals are required for AXI4-Stream IP core generation. In Task 1.3, the目标平台接口表如下图所示加载。音频数据流端口,vigw_in.那data_in.那vigw_out.andData_out,映射到AXI4流界面,pass_through_led,biquad_lpf_led,biquad_bpf_led,biquad_hpf_ledare mapped to the LEDs on Zedboard and the control parameter portFilter_select映射到AXI4-Lite界面。如果您使用的是Zybo Board,请通过选择将LED映射到过滤器LED通用[0:4]。

The AXI4-Stream interface communicates in master/slave mode, where the master device sends data to the slave device. Therefore, if a data port is an input port, assign it to anAXI4流奴隶interface, and if a data port is output port, assign it to anAXI4-Stream Master接口。

3.右键单击任务3.2,生成RTL代码和IP核心,选择跑到选定的任务生成IP核心。您可以在生成的IP核心报告中找到寄存器地址映射和IP核心的其他文档。

将IP集成到AXI4-Stream兼容的参考设计中

接下来,在HDL工作流程顾问中,您运行嵌入式系统集成在zynq硬件上部署生成的HDL IP核心的任务。

1.运行任务4.1,Create Project。This task inserts the generated IP core into the带AXI4流接口的音频系统参考设计。如第一个图所示,该参考设计包含IP,用于处理ZedBoard中的音频数据。生成的项目是完整的Zynq设计,包括算法部分(生成的DUT算法IP)和平台部分(参考设计)。有关如何创建参考设计的详细信息,该设计集成了音频过滤器模型,请参阅创作Zynq板上的音频系统参考设计or创作Zybo板上的音频系统参考设计例。

2。单击结果窗格中的链接以打开生成的Vivado项目。在Vivado工具中,单击开放式块设计要查看Zynq设计图,包括生成的HDL IP内核,其他音频处理IP和Zynq处理器。

3.在HDL Workflow Advisor中,运行其余任务以生成软件界面模型,并构建和下载FPGA比特流。选择下载任务中的编程方法程序目标设备要将FPGA比特流下载到Zynq板上的SD卡上,因此在电源循环Zynq板时,您的设计将自动重新加载。

Generate ARM executable to Tune Parameters on the FPGA Fabric

任务4.2生成软件界面模型,生成软件界面模型。

1.在生成代码的软件强度rface model, comment out the audio input source and audio output sink i.e From Multimedia File, Data Type Conversion, Buffer, Audio Device Writer and Spectrum Analyzer Blocks. These blocks do not need to be run on the ARM processor. The Audio_filter IP is running as *Filtering_Algorithm" on FPGA fabric. The ARM processor is using AXI4-Lite interface for selecting the filter type i.e. Biquad Low pass, band pass, High pass or Pass Through.

在生成的模型中,单击“硬件”窗格并转至硬件设置打开Configuration Parameter对话框。

选择Solver并将“停止时间”设置为“INF”,然后单击“确定”。

从硬件窗格中,单击监控和曲调按钮。

点击跑模型工具串上的按钮。嵌入式编码器构建模型,将可执行文件下载到zynq板硬件,执行它,并将模型连接到zynq板硬件上的可执行文件。

可以使用下拉液选项选择要使用的过滤器类型过滤器选择块

可以通过封堵耳机或扬声器来听到滤波后的音频输出HPHO出来jack on the Zynq board. Depending on the filter selected, the corresponding LED on the Zynq board turns on. In this example, LD0 turns on when Pass through (No filter used) option is selected, LD1 turns on when Biquad Low pass filter is selected, LD2 turns on when Biquad Band pass filter is selected and LD3 turns on when Biquad High pass filter is selected.