为英特尔SoC工作流定义自定义板和参考设计

这个例子展示了如何在HDL Coder™Intel SoC工作流中定义和注册自定义板和参考设计。

介绍

使用这个示例,您将能够在Intel SoC工作流的HDL Workflow Advisor中注册Terasic DE1-SoC开发工具包和自定义参考设计。

本例使用Terasic DE-1 SoC,但以同样的方式,您可以为其他Intel SoC设备定义和注册自定义板或自定义参考设计。

需求

中列出的支持版本金宝appHDL编码文档

英特尔SoC嵌入式设计套件

Terasic DE1-SoC开发试剂盒

Intel SoC设金宝app备的HDL编码器支持包

英特尔SoC设备的嵌入式编码器金宝app支持包

建立英特尔SoC硬件和工具

1.通过阅读板参考手册,了解Terasic DE1-SoC的可用特性。

2.搭建Terasic DE1-SoC,如下图所示:

3.请确保已正确安装USB COM端口设备驱动程序。

4.将Terasic DE1-SoC上的UART和USB爆破端口连接到您的计算机。

5.使用以太网线将Terasic DE1-SoC连接到您的计算机。Terasic DE1-SoC的默认IP地址为192.168.1.101.

6.下载Terasic DE1-SoC Linux映像文件,解压缩GZ归档文件,然后将原始磁盘映像文件写入microSD卡。将micro - sd卡插入连接器J11.

7.使用如下命令设置Intel Quartus工具路径:

(C:\intelFPGA\17.1\ Quartus \bin64\ Quartus .exe');

在执行该命令时,请使用您自己的Intel Quartus安装路径。

8.使用以下命令建立Terasic DE1-SoC硬件连接:

h = alterasoc (“192.168.1.101”,“根”,“cyclonevsoc”);

使用英特尔Quartus Prime创建参考设计

参考设计捕获了SoC设计的完整结构,定义了不同的组件及其相互连接。HDL Coder SoC工作流生成与参考设计集成的IP核,然后用于对SoC板编程。下图描述了参考设计、HDL IP核和SoC板之间的关系

在本节中,我们概述了使用英特尔Quartus和QSys环境创建和导出简单参考设计所需的基本步骤。有关QSys系统集成工具的更多信息,请参阅Altera/Intel文档。

1.使用带有设备部件号的新建项目向导创建一个空的Quartus项目,如下图所示

2.在Quartus中通过导航初始化Qsys工具- >转换频率如图所示

3.选择Cyclone-V硬处理器系统(HPS)&阿尔特拉锁相环从IP目录到创建的Qsys项目的IP。使能hps到fpga的用户0时钟(h2f_user0_clock),并将其与refclk的锁相环,如下图所示

完成硬处理器系统所需的其他设置,如外设引脚设置和模式设置。

4.保持h2f_axi_master在工作流IP集成过程中,打开端口连接,以便连接到DUT IP。完成其余的连接Altera PLL IP和HPS IP如下图所示

5.保存Qsys文件。这个文件将在您创建参考设计插件时使用。

在HDL Workflow Advisor中注册DE1-SoC板

在本节中,我们概述了在HDL Workflow Advisor中注册Terasic DE1-SoC开发工具包所需的步骤。

1.使用该名称创建单板注册文件hdlcoder_board_customization.m并将其添加到MATLAB路径中。

单板注册文件包含单板插件列表。一个板插件是一个MATLAB包文件夹包含板定义文件和所有参考设计插件与板。

下面的代码描述了包含板插件的板注册文件的内容DE1SoCRegistration在HDL Workflow Advisor中注册Terasic DE1-SoC开发工具包。

函数r = hdlcoder_board_customization%单板插件注册文件% 1。MATLAB路径上任何具有此名称的注册文件都将被选中% 2。的位置返回单元格数组%板插件% 3。板插件必须是一个包文件夹可从MATLAB路径,%,并包含一个单板定义文件

r = {…“DE1SoCRegistration.plugin_board”,…};结束

2.创建单板定义文件。

单板定义文件包含了关于SoC单板的信息。

下面的代码描述了DE1-SoC板定义文件的内容plugin_board.m它驻留在板插件内DE1SoCRegistration.

FPGA I/O引脚位置信息(“FPGAPin”)及标准(“IOSTANDARD”)是从Intel Quartus-II的Pin Planner中获得的。

房地产BoardName定义DE-1 SoC板的名称为Terasic DE1-SoC开发试剂盒在HDL Workflow Advisor中。

函数hB = plugin_board ()%板定义

%构造板对象hB = hdlcoder.Board;

hB。BoardName =Terasic DE1-SoC开发试剂盒;

% FPGA设备信息hB。FPGAVendor =“阿尔特拉”;hB。FPGAFamily =“气旋V”;hB。FPGADevice =“5 csema5f31c6”;hB。FPGAPackage ='';hB。FPGASpeed ='';

%的工具信息hB。金宝appSupportedTool = {“阿尔特拉第四的二世”};

% FPGA JTAG链位置hB。JTAGChainPosition = 2;

% %添加接口%标准“外部端口”接口hB.addExternalPortInterface (…“IOPadConstraint”, {”IO_STANDARD 2.5 v”});

%自定义单板外部I/O接口hB.addExternalIOInterface (…“InterfaceID”,led通用的,…“InterfaceType”,“出”,…“PortName”,gpl授权的,…“PortWidth”10…“FPGAPin”, {“V16”,“W16”,“15,17”,“V18”,“W17”,“W19”,“Y19”,“W20”,“21”,“Y21”},…“IOPadConstraint”, {”IO_STANDARD 3.3 - v LVTTL”});

hB.addExternalIOInterface (…“InterfaceID”,“开关”,…“InterfaceType”,“在”,…“PortName”,“西南”,…“PortWidth”10…“FPGAPin”, {“AB12”,“AC12”,“AF9”,“AF10”,“AD11”,“AD12”,“AE11”,“AC9”,“AD10”,“AE12”},…“IOPadConstraint”, {”IO_STANDARD 3.3 - v LVTTL”});

hB.addExternalIOInterface (…“InterfaceID”,“按钮”,…“InterfaceType”,“在”,…“PortName”,“关键”,…“PortWidth”4…“FPGAPin”, {“AA14”,“AA15”,“W15”,“造成”},…“IOPadConstraint”, {”IO_STANDARD 3.3 - v LVTTL”});

在HDL Workflow Advisor中注册自定义参考设计

在本节中,我们概述了在HDL Workflow Advisor中注册自定义参考设计所需的步骤。

1.创建一个参考设计注册文件hdlcoder_ref_design_customization.m包含与SoC板相关的参考设计插件列表。

参考设计插件是一个MATLAB包文件夹,包含参考设计定义文件和与SoC设计项目相关的所有文件。参考设计注册文件还必须包含相关板的名称。

下面的代码描述了包含参考设计插件的DE1-SoC参考设计注册文件的内容DE1SoCRegistration.qsys_base_170与董事会有联系Terasic DE1-SoC开发试剂盒.

函数[rd, boardName] = hdlcoder_ref_design_customization . txt文件%参考设计插件注册文件% 1。注册文件与此名称在一个板插件文件夹内%将被拾取% 2。在MATLAB路径上使用此名称的任何注册文件也将被选中% 3。注册文件返回指向的位置的单元格数组%参考设计插件% 4。注册文件还返回其关联的板名% 5。参考设计插件必须是可访问的包文件夹% MATLAB路径,并包含一个参考设计定义文件

rd = {“DE1SoCRegistration.qsys_base_170.plugin_rd”,…};

boardName =Terasic DE1-SoC开发试剂盒;结束

2.创建参考设计定义文件。

参考设计定义文件定义了自定义参考设计和将由HDL Coder SoC工作流生成的HDL IP核之间的接口。

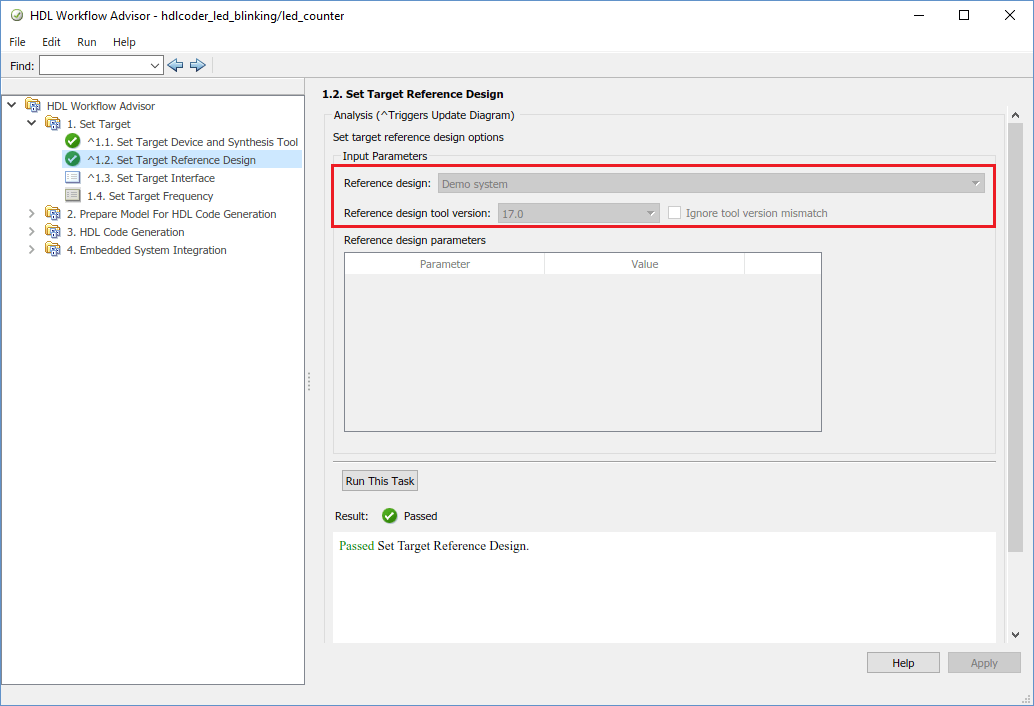

以下代码描述了DE1-SoC参考设计定义文件的内容plugin_rd.m与董事会有联系Terasic DE1-SoC开发试剂盒它驻留在参考设计插件中DE1SoCRegistration.qsys_base_170.房地产ReferenceDesignName将参考设计的名称定义为演示系统在HDL Workflow Advisor中。

函数hRD = plugin_rd ()参考设计定义

%构造参考设计对象hRD = hdlcoder。ReferenceDesign (“SynthesisTool”,“阿尔特拉第四的二世”);

hRD。ReferenceDesignName =“演示系统)”;hRD。BoardName =Terasic DE1-SoC开发试剂盒;

%的工具信息hRD。金宝appSupportedToolVersion = {“17.0”,“17.1”};

%%添加自定义设计文件%添加自定义Qsys设计hRD.addCustomQsysDesign (…“CustomQsysPrjFile”,“system_soc.qsys”);

% %添加接口添加时钟接口hRD.addClockInterface (…“ClockConnection”,“pll_0.outclk0”,…“ResetConnection”,“hps_0.h2f_reset”,…“DefaultFrequencyMHz”, 50岁,…“MinFrequencyMHz”5,…“MaxFrequencyMHz”, 500,…“ClockModuleInstance”,“pll_0”,…“ClockNumber”, 0);

%添加AXI4和AXI4- lite从接口hRD.addAXI4SlaveInterface (…“InterfaceConnection”,“hps_0.h2f_axi_master”,…“BaseAddress”,“0 x0000”);

DE1-SoC参考设计插件文件夹DE1SoCRegistration.qsys_base_170必须包含Qsys文件system_soc.qsys从英特尔Quartus Prime项目中保存的。DE1-SoC参考设计定义文件plugin_rd.m通过以下声明确定SoC设计项目文件:

hRD.addCustomQsysDesign (“CustomQsysPrjFile”,“system_soc.qsys”);

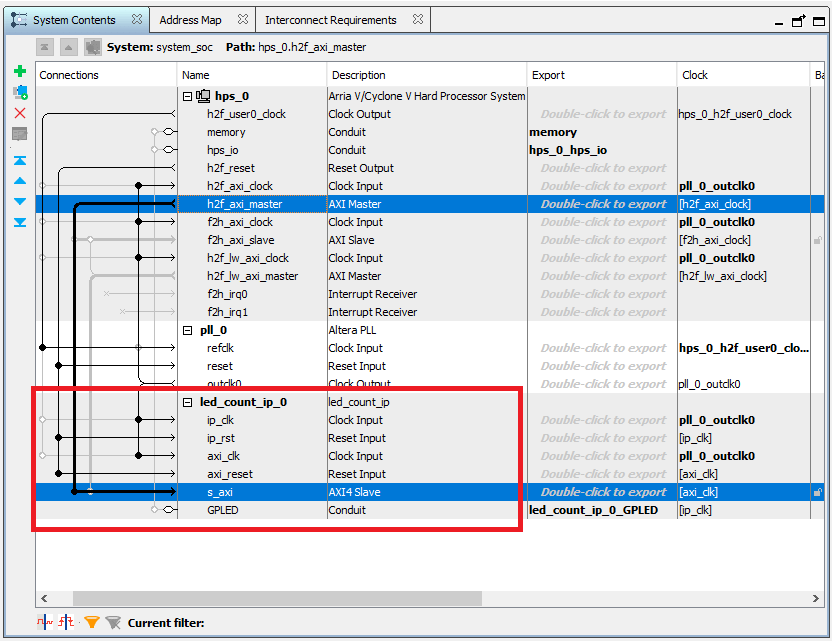

除了SoC设计项目文件,plugin_rd.m还通过语句定义了自定义参考设计和HDL IP核之间的接口连接,如下图所示:

hRD.addClockInterface (…“ClockConnection”,“pll_0.outclk0”,…“ResetConnection”,“hps_0.h2f_reset”,…“DefaultFrequencyMHz”, 50岁,…“MinFrequencyMHz”5,…“MaxFrequencyMHz”, 500,…“ClockModuleInstance”,“pll_0”,…“ClockNumber”, 0);hRD.addAXI4SlaveInterface (…“InterfaceConnection”,“hps_0.h2f_axi_master”,…“BaseAddress”,“0 x0000”);

执行Terasic DE1-SoC的SoC工作流

前几节讨论了定义和注册Terasic DE1-SoC的步骤,以及在HDL Workflow Advisor中为SoC工作流定制参考设计的步骤。在本节中,我们使用自定义板和参考设计注册系统来生成一个在Terasic DE1-SoC上闪烁led的HDL IP核。下面演示中使用的文件位于,

matlab /工具箱/ hdlcoder / hdlcoderdemos / customboards / DE1SOC

1.使用以下命令将Terasic DE1-SoC注册文件添加到MATLAB路径中:

目录(fullfile (matlabroot,“工具箱”,“hdlcoder”,“hdlcoderdemos”,“customboards”,“DE1SOC”));

2.使用命令打开实现L金宝appED闪烁的Simulink模型,

open_system (“hdlcoder_led_blinking”);

使用HDL工作流顾问生成一个HDL IP核

1.使用HDL workflow Advisor中的IP Core Generation工作流,您可以从Simulink模型自动生成一个可共享和可重用的IP Core模块。金宝appHDL Coder从Simulink块生成HDL代码,也为连接IP核到嵌入式金宝app处理器的axis接口逻辑生成HDL代码。HDL编码器将所有生成的文件打包到一个IP核心文件夹中。然后可以在Intel Qsys环境中将生成的IP核与更大的FPGA嵌入式设计集成。

2.启动IP核生成工作流。

2.1.从。打开HDL工作流顾问hdlcoder_led_blinking / led_counter通过右键单击led_counter子系统,并选择HDL代码>高密度脂蛋白工作流顾问.

2.2。在设定目标>设置目标设备和合成工具任务,为目标工作流程中,选择IP核心代.

2.3.为目标平台中,选择Terasic DE1-SoC开发试剂盒.

2.4.点击运行这个任务运行设置目标设备和合成工具的任务。

3.在任务1.2中,选择了设置目标参考设计默认系统。点击运行这个任务.

4.配置目标接口。

将DUT中的每个端口映射到一个IP核心目标接口。在本例中,输入端口Blink_frequency和Blink_direction被映射到AXI4.的领导输出端口映射到外部接口,通用led [0:9],连接Terasic DE1-SoC开发套件上的LED硬件。

5.按照步骤3和步骤4使用HDL工作流顾问生成一个HDL IP核的部分开始瞄准英特尔SoC设备示例生成IP核,查看IP核生成报告。

6.步骤1将IP核与Intel Qsys环境集成的部分开始瞄准英特尔SoC设备示例将IP核集成到参考设计中,并创建Qsys项目。

7.现在让我们检查一下SoC工作流在完成创建项目下任务嵌入式系统集成.下图显示了我们突出显示HDL IP Core的SoC项目。将这个项目与之前在自定义参考设计插件中使用的项目进行比较,有助于更深入地理解自定义参考设计和HDL IP核之间的关系。

8.按照步骤2、3和4将IP核与Intel Qsys环境集成的部分开始瞄准英特尔SoC设备示例生成软件接口模型,分别生成FPGA位流和程序目标设备。

9.Terasic DE1-SoC上的led在加载比特流后开始闪烁。此外,您还可以通过执行软件接口模型来控制LED闪烁频率和方向。指生成软件界面模型的部分开始瞄准英特尔SoC设备实例从生成的软件界面模型控制LED闪烁频率和方向。