为Zynq工作流定义定制板和参考设计

这个例子展示了如何在Zynq®工作流中定义和注册定制板和参考设计。

简介

使用这个例子,你将能够注册Digilent®Zybo Zynq开发板和定制参考设计在HDL工作流顾问的Zynq工作流。

本例使用的是Zybo Zynq板,但同样地,你也可以为其他Zynq平台定义和注册定制板或定制参考设计。

需求

Xilinx Vivado设计套件,其支持版本列在金宝appHDL编码器文档

Digilent®Zybo Zynq™开发板与附件套件

Xilinx Zyn金宝appq平台的HDL Coder支持包

Xilinx Zynq平台的嵌金宝app入式编码器支持包

注意:本例使用Digilent®Zybo Zynq-7000 ARM/FPGA SoC训练板。此示例不适用于Digilent®Zybo Z7: Zynq-7000 ARM/FPGA SoC开发板,该开发板有两个变体Zybo Z7-10和Zybo Z7-20。

设置Zybo板

1.通过阅读Zybo板参考手册,了解Zybo板上可用的功能。

2.设置Zybo板,如下图所示:

3.确保已在计算机上正确安装USB COM端口设备驱动程序。

4.配置JP5引导模式跳线,以允许从连接到连接器的microSD卡加载Zynq Linux映像阁下如下图所示。

5.配置JP7电源选择跳线使用USB作为电源,如下图所示。

6.将Zybo板上的共享UART/JTAG USB端口连接到您的计算机。

7.使用以太网线将Zybo板连接到计算机。Zybo默认IP地址为192.168.1.110.

8.下载Zybo Zynq Linux映像,提取Zip档案,并将内容复制到microSD卡。将microSD卡插入连接器阁下.

9.使用以下命令设置Xilinx Vivado工具路径:

hdlsetuptoolpath (“ToolName”,“Xilinx Vivado”,“路径”,“C: \ Xilinx \ Vivado \ 2017.4 \ bin \ vivado.bat ');

执行该命令时,请使用您自己的Xilinx Vivado安装路径。

10.使用以下命令建立Zynq硬件连接:

H = zynq();

在Xilinx Vivado工具中注册Zybo板部件

默认安装,Vivado 2017.4工具将没有Zybo板部分预安装。这些文件必须从Digilent网站。因此,解压内容并导航到下面给出的Vivado安装目录,手动将更新后的Zybo板文件复制到xilinx Vivado工具中。

C: \ Xilinx \ Vivado \ 2017.4 \ \董事会\ board_files数据

作为这一步的结果,Zybo板部分被添加到开发板列表,同时创建特定于板的vivado项目。

注意:如果上述链接不可用,请从Digilent网站获取Zybo板文件。

使用Xilinx Vivado创建并导出自定义参考设计

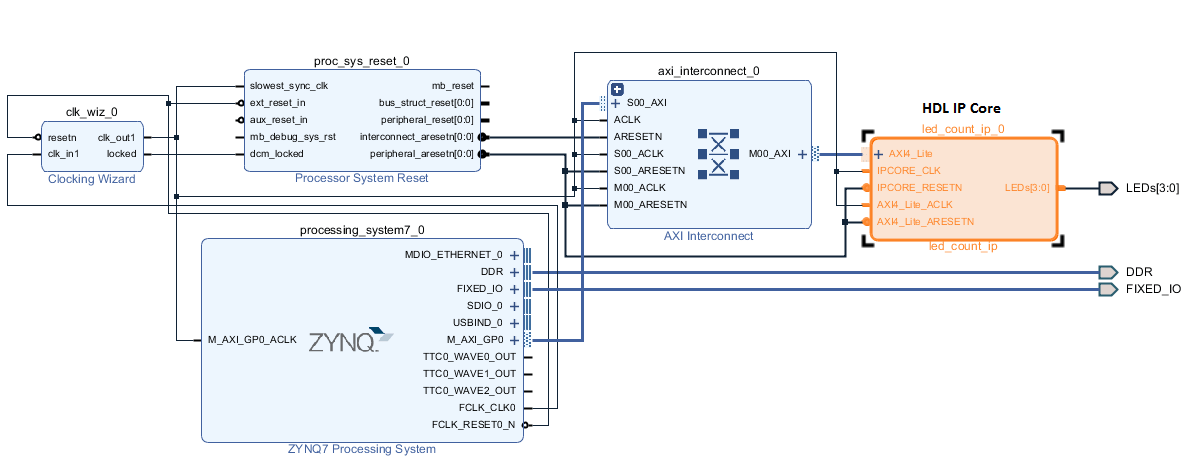

参考设计捕获了SoC设计的完整结构,定义了不同的组件及其互连。HDL Coder SoC工作流生成一个与参考设计集成的IP核,然后用于编程SoC板。下图描述了参考设计、HDL IP核和SoC板之间的关系。

在本节中,我们概述了使用Xilinx Vivado IP Integrator环境创建和导出简单参考设计所需的基本步骤。有关IP Integrator工具的更多信息,请参阅Xilinx文档。

1.使用板部件创建一个空的Xilinx Vivado RTL项目Zybo作为单板的默认部件,如下图所示:

2.创建一个空块设计并添加ZYNQ7处理系统IP块。运行block automation如图所示,设置Zybo的board预置,其中包含ZYNQ7 Processing系统IP与MIO Configuration、Clock Configuration和DDR Configuration相关的参数。

在下图中,您可以看到MIO外设是根据Zybo板定义标记的,这是应用板预置的结果。

3.完成砌块设计,如下图所示:

注意,块设计不包含有关HDL IP核的任何信息。

4.将完成的块设计导出为Tcl脚本design_led.tcl如下图所示:

导出的Tcl脚本(design_led.tcl)构成自订参考设计。Tcl脚本将在HDL Coder SoC工作流中使用,以重新创建块设计,并将生成的HDL IP核与Xilinx Vivado项目中的块设计集成在一起。

在HDL Workflow Advisor中注册Zybo板

在本节中,我们将概述在HDL Workflow Advisor中注册Zybo板所需的步骤。

1.用该名称创建一个董事会注册文件hdlcoder_board_customization.m并将其添加到MATLAB路径。

单板注册文件包含单板插件列表。板卡插件是一个MATLAB包文件夹,包含板卡定义文件和与板卡相关的所有参考设计插件。

下面的代码描述了包含单板插件的单板注册文件的内容ZyboRegistration在HDL工作流顾问中注册Zybo板。

函数R = hdlcoder_board_customization单板插件注册文件% 1。在MATLAB路径上使用此名称的任何注册文件都将被拾取% 2。的位置的单元格数组%单板插件% 3。板插件必须是可从MATLAB路径访问的包文件夹,包含一个板定义文件

R = {...“ZyboRegistration.plugin_board”,...};结束

2.创建板定义文件。

单板定义文件包含了SoC单板的相关信息。

下面的代码描述了Zybo板定义文件的内容plugin_board.m它位于板插件中ZyboRegistration.

有关FPGA I/O引脚位置的资料(“FPGAPin”)及标准(“IOSTANDARD”)是从Digilent的Zybo主约束文件中获得的。

房地产BoardName将Zybo板的名称定义为ZYBO在HDL工作流顾问。

函数hB = plugin_board()%板定义

构造板对象hB = hdlcode . board;

hB。BoardName =“ZYBO”;

% FPGA设备信息hB。FPGAVendor =“Xilinx”;hB。FPGAFamily =“Zynq”;hB。FPGADevice =“xc7z010”;hB。FPGAPackage =“clg400”;hB。FPGASpeed =' 1 ';

%工具信息hB。金宝appSupportedTool = {“Xilinx Vivado”};

% FPGA JTAG链位置hB。JTAGChainPosition = 2;

%%添加接口标准的“外部端口”接口hB.addExternalPortInterface (...“IOPadConstraint”, {' iostandard = lvcmos33 '});

自定义单板外部I/O接口hB.addExternalIOInterface (...“InterfaceID”,“led通用”,...“InterfaceType”,“出”,...“PortName”,“发光二极管”,...“PortWidth”4...“FPGAPin”, {“M14”,“M15”,“八国”,“D18”},...“IOPadConstraint”, {' iostandard = lvcmos33 '});

hB.addExternalIOInterface (...“InterfaceID”,“按钮”,...“InterfaceType”,“在”,...“PortName”,“按钮”,...“PortWidth”4...“FPGAPin”, {“R18”,P16的,“V16”,“造成”},...“IOPadConstraint”, {' iostandard = lvcmos33 '});

在HDL Workflow Advisor中注册自定义参考设计

在本节中,我们将概述在HDL Workflow Advisor中注册定制参考设计所需的步骤。

1.创建一个名为hdlcoder_ref_design_customization.m包含与SoC板相关的参考设计插件列表。

参考设计插件是一个MATLAB包文件夹,包含参考设计定义文件和与SoC设计项目相关的所有文件。参考设计注册文件还必须包含相关电路板的名称。

下面的代码描述了包含参考设计插件的Zybo参考设计注册文件的内容ZyboRegistration。Vivado2017_2与董事会关联ZYBO.

函数[rd, boardName] = hdlcoder_ref_design_customization . [d, boardName] = hdlcoder_ref_design_customization .%参考设计插件注册文件% 1。板插件文件夹中带有此名称的注册文件%会被捡起来% 2。MATLAB路径上任何具有此名称的注册文件也将被拾取% 3。的位置,注册文件返回单元格数组%参考设计插件% 4。注册文件还返回其关联的板名% 5。参考设计插件必须是可访问的包文件夹% MATLAB路径,并包含一个参考设计定义文件

Rd = {“ZyboRegistration.Vivado2017_2.plugin_rd”,...};

boardName =“ZYBO”;结束

2.创建参考设计定义文件。

参考设计定义文件定义了定制参考设计和HDL IP核之间的接口,该接口将由HDL Coder SoC工作流生成。

以下代码描述了Zybo参考设计定义文件的内容plugin_rd.m与董事会关联ZYBO它位于参考设计插件中ZyboRegistration。Vivado2017_2.房地产ReferenceDesignName将参考设计的名称定义为演示系统在HDL工作流顾问。

函数hRD = plugin_rd(%参考设计定义

构造参考设计对象hRD = hdlcoder。ReferenceDesign (“SynthesisTool”,“Xilinx Vivado”);

hRD。ReferenceDesignName =“演示系统”;hRD。BoardName =“ZYBO”;

%工具信息hRD。金宝appSupportedToolVersion = {“2017.2”,“2017.4”};

%添加自定义Vivado设计hRD.addCustomVivadoDesign (...“CustomBlockDesignTcl”,“design_led.tcl”,...“VivadoBoardPart”,“digilentinc.com: zybo: part0:1.0”);

%%添加接口%添加时钟接口hRD.addClockInterface (...“ClockConnection”,“clk_wiz_0 / clk_out1”,...“ResetConnection”,“proc_sys_reset_0 / peripheral_aresetn”);

添加AXI4和AXI4- lite从接口hRD.addAXI4SlaveInterface (...“InterfaceConnection”,“axi_interconnect_0 / M00_AXI”,...“BaseAddress”,“0 x40010000”,...“MasterAddressSpace”,“processing_system7_0 /数据”);

除了参考设计定义文件外,参考设计插件还必须包含SoC设计项目文件。

Zybo参考设计插件文件夹ZyboRegistration。Vivado2017_2必须包含Tcl脚本design_led.tcl之前从Xilinx Vivado项目导出。Zybo参考设计定义文件plugin_rd.m通过以下语句识别SoC设计项目文件:

hRD.addCustomVivadoDesign (“CustomBlockDesignTcl”,“design_led.tcl”);

除了SoC设计项目文件,plugin_rd.m还定义了自定义参考设计和HDL IP核之间的接口连接,如下图所示:

hRD.addClockInterface (...“ClockConnection”,“clk_wiz_0 / clk_out1”,...“ResetConnection”,“proc_sys_reset_0 / peripheral_aresetn”);hRD.addAXI4SlaveInterface (...“InterfaceConnection”,“axi_interconnect_0 / M00_AXI”,...“BaseAddress”,“0 x40010000”,...“MasterAddressSpace”,“processing_system7_0 /数据”);

警告:的“BaseAddress”的有效地址“MasterAddressSpace”并且不应该在自定义参考设计中与其他基于地址的外围设备产生任何地址冲突。

执行Zybo板的SoC工作流

前面的部分讨论了在HDL Workflow Advisor中为SoC工作流定义和注册Zybo板和自定义参考设计的步骤。在本节中,我们使用自定义板和参考设计注册系统来生成一个HDL IP核,在Zybo板上闪烁led。下面演示中使用的文件位于,

matlab /工具箱/ hdlcoder / hdlcoderdemos / customboards / ZYBO

1.使用以下命令将Zybo板注册文件添加到MATLAB路径,

目录(fullfile (matlabroot,“工具箱”,“hdlcoder”,“hdlcoderdemos”,“customboards”,“ZYBO”));

2.使用命令打开实现L金宝appED闪烁的Simulink模型,

open_system (“hdlcoder_led_blinking_4bit”);

3.启动HDL Workflow Advisorhdlcoder_led_blinking_4bit / led_counter的led_counter子系统和选择HDL代码>HDL工作流顾问或者点击启动HDL工作流顾问框在模型中。

在设定目标>设置目标设备和合成工具任务,选择IP核生成为目标工作流程.ZYBO现在出现在下拉列表中目标平台.选择ZYBO作为一个目标平台.

4.点击运行此任务要完成设置目标设备和合成工具的任务。

5.在设定目标>设定目标参考设计任务,自定义参考设计演示系统现在出现在参考设计字段。选择演示系统点击运行此任务.

6.任务1.3设置目标接口,选择如下图所示的连接,然后单击运行此任务.

7.遵循步骤3和步骤4使用HDL工作流顾问生成HDL IP核的部分着眼于Xilinx Zynq平台示例,生成IP核,并查看IP核生成报表。

8.遵循以下步骤的第一步将IP核与Xilinx Vivado环境集成的部分着眼于Xilinx Zynq平台在参考设计中集成IP核并创建vivado项目的示例。

9.现在,让我们来研究一下由SoC工作流创建的Xilinx Vivado项目创建项目下任务嵌入式系统集成.下图显示了SoC项目的块设计,其中我们突出显示了HDL IP核。将此块设计与以前用于导出自定义参考设计的块设计进行比较,以便更深入地理解自定义参考设计和HDL IP核之间的关系,这是有指导意义的。

10.的步骤2、3和4将IP核与Xilinx Vivado环境集成的部分着眼于Xilinx Zynq平台以生成软件接口模型为例,分别生成FPGA位流和编程目标设备。

11.Zybo板上的led现在将在加载比特流后开始闪烁。此外,您将能够通过在Zynq ARM处理器上执行软件接口模型来控制LED闪烁频率和方向。指生成软件接口模型的部分着眼于Xilinx Zynq平台实例从生成的软件界面模型中控制LED闪烁频率和方向。