开始使用HDL工作流命令行界面

这个例子展示了如何使用高密度脂蛋白HDL工作流运行工作流顾问从命令行和出口到脚本的功能。

介绍

这个例子是一个循序渐进的指南,帮助介绍高密度脂蛋白工作流命令行接口。

使用高密度脂蛋白工作流命令行接口,您可以运行相同的一系列步骤和控制相同的配置设置可用在高密度脂蛋白工作流顾问以下工作流程:

通用ASIC / FPGA

FPGA交钥匙

IP核心代

金宝app仿真软件实时FPGA的I / O

打开模型

在这个例子中,我们将使用hdlcoder_sfir_fixed_stream模型,但高密度脂蛋白工作流命令行接口可用于任何与上面列出的工作流模型。

open_system (“hdlcoder_sfir_fixed_stream”)

确保所需的第三方工具包含路径。例如,包括其默认windows Vivado安装在本地位置,使用以下命令:

> > hdlsetuptoolpath (“ToolName”、“Xilinx Vivado”、“路径”,“C: \ Xilinx \ Vivado \ 2017.4 \ bin \ vivado.bat ');

接下来,启动工作流DUT顾问和选择适当的子系统。

设置工作流

使用高密度脂蛋白工作流顾问设置您的项目你想要设置,如合成工具和设备。开始通过改变工作流“通用ASIC / FPGA”这样我们就可以标注模型合成的结果。

您还可以指定合成高水平目标的工具。例如,尝试“速度优化”的设置工具。

同时,改变“跳过这个任务”复选框运行实现这样导出的脚本运行此步骤

出口到脚本

毕竟已经进入初始设置,工作流程导出到一个脚本,可以直接从命令行运行更快的设计迭代。

保存文件和任何你喜欢的名字。默认将“hdlworkflow.m”。导出的脚本如下所示:

% - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -% HDL工作流脚本采用MATLAB生成% 9.0 (R2016b预映)在31/12/2015 10:40:45%这个脚本生成使用以下参数值:%文件名:“/ mathworks /猛击/沙盒/ cberry /工作/演示/ hdlworkflow.m '%覆盖:真%的评论:真%的标题:真% DUT:“hdlcoder_sfir_fixed_stream / DUT”%查看更改,修改工作流程之后,运行以下命令:% > > hWC.export (DUT, hdlcoder_sfir_fixed_stream / DUT);% - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -% 2018年版权MathWorks公司。% %加载模型load_system (“hdlcoder_sfir_fixed_stream”);% %恢复默认HDL的模型参数% hdlrestoreparams (hdlcoder_sfir_fixed_stream / DUT的);% % HDL参数模型% %集模型的hdlcoder_sfir_fixed_stream HDL参数hdlset_param (“hdlcoder_sfir_fixed_stream”,“HDLSubsystem”,“hdlcoder_sfir_fixed_stream / DUT”);hdlset_param (“hdlcoder_sfir_fixed_stream”,“ReferenceDesign”,“默认系统与AXI4-Stream接口”);hdlset_param (“hdlcoder_sfir_fixed_stream”,“ResetType”,“同步”);hdlset_param (“hdlcoder_sfir_fixed_stream”,“SynthesisTool”,“Xilinx Vivado”);hdlset_param (“hdlcoder_sfir_fixed_stream”,“SynthesisToolChipFamily”,“Zynq”);hdlset_param (“hdlcoder_sfir_fixed_stream”,“SynthesisToolDeviceName”,“xc7z020”);hdlset_param (“hdlcoder_sfir_fixed_stream”,“SynthesisToolPackageName”,“clg484”);hdlset_param (“hdlcoder_sfir_fixed_stream”,“SynthesisToolSpeedValue”,' 1 ');hdlset_param (“hdlcoder_sfir_fixed_stream”,“TargetDirectory”,“hdl_prj / hdlsrc”);% %工作流配置设置%构建工作流配置对象的默认设置中国= hdlcoder.WorkflowConfig (“SynthesisTool”,“Xilinx Vivado”,“TargetWorkflow”,“通用ASIC / FPGA”);%指定顶级项目目录中国。ProjectFolder =“hdl_prj”;%设置工作流任务运行中国。RunTaskGenerateRTLCodeAndTestbench = true;中国。RunTaskCreateProject = true;中国。RunTaskRunSynthesis = true;中国。RunTaskRunImplementation = false;中国。RunTaskAnnotateModelWithSynthesisResult = true;%设置属性“RunTaskGenerateRTLCodeAndTestbench”相关的任务中国。GenerateRTLCode = true;中国。GenerateRTLTestbench = false;中国。GenerateCosimulationModel = false;中国。CosimulationModelForUseWith =“导师图形ModelSim”;中国。GenerateValidationModel = false;%设置属性“RunTaskCreateProject”相关的任务中国。目标= hdlcoder.Objective.None;中国。AdditionalProjectCreationTclFiles =”;%设置属性“RunTaskRunSynthesis”相关的任务中国。SkipPreRouteTimingAnalysis = false;%设置属性“RunTaskRunImplementation”相关的任务中国。IgnorePlaceAndRouteErrors = false;%设置属性“RunTaskAnnotateModelWithSynthesisResult”相关的任务中国。CriticalPathSource =“pre-route”;中国。CriticalPathNumber = 1;中国。ShowAllPaths = false;中国。ShowDelayData = true;中国。ShowUniquePaths = false;中国。ShowEndsOnly = false;%验证工作流配置对象hWC.validate;% %运行工作流hdlcoder.runWorkflow (“hdlcoder_sfir_fixed_stream / DUT”、中国);

从脚本运行工作流

直接运行脚本将执行您的工作流和输出一组简洁的cmd窗口运行时消息。如果你想看到详细的合成工具输出信息,点击相应的“合成工具日志:”超链接在所需的任务标题在MATLAB编辑器中打开这个文件。

> > hdlworkflow # # #工作流程开始。# # # + + + + + + + + + + + + + +任务生成RTL代码和Testbench+ + + + + + + + + + + + + +# # #生成高密度脂蛋白为“hdlcoder_sfir_fixed_stream / DUT”。# # #开始高密度脂蛋白检查。# # #开始硬件描述语言(VHDL)代码一代为“hdlcoder_sfir_fixed_stream”。# # #工作在hdlcoder_sfir_fixed_stream / DUT / symmetric_fir作为hdl_prj \ hdlsrc \ hdlcoder_sfir_fixed_stream \ symmetric_fir.vhd。# # #工作在hdlcoder_sfir_fixed_stream / DUT作为hdl_prj \ hdlsrc \ hdlcoder_sfir_fixed_stream \ DUT.vhd。# # #创建高密度脂蛋白代码一代检查报告DUT_report.html# # #高密度脂蛋白检查为“hdlcoder_sfir_fixed_stream”完整的与0错误,0警告,0消息。# # #高密度脂蛋白代码一代完成了。# # # + + + + + + + + + + + + + +任务创建项目+ + + + + + + + + + + + + +# # #生成赛灵思公司Vivado2014.4项目:hdl_prj \ vivado_prj \ DUT_vivado.xpr# # #合成工具日志:hdl_prj \ hdlsrc \ hdlcoder_sfir_fixed_stream \ workflow_task_CreateProject.log# # #任务“创建项目”成功的。# # # + + + + + + + + + + + + + +任务运行合成+ + + + + + + + + + + + + +# # #合成工具日志:hdl_prj \ hdlsrc \ hdlcoder_sfir_fixed_stream \ workflow_task_RunSynthesis.log# # #任务“快跑合成”成功的。# # # + + + + + + + + + + + + + +任务运行实现+ + + + + + + + + + + + + +# # #合成工具日志:hdl_prj \ hdlsrc \ hdlcoder_sfir_fixed_stream \ workflow_task_RunImplementation.log# # #任务“快跑实现”成功的。# # # + + + + + + + + + + + + + +注释的任务模型与合成结果+ + + + + + + + + + + + + +# # #解析的时机文件…# # #匹配源=“hdlcoder_sfir_fixed_stream / DUT symmetric_fir / m3_out1 '# # #匹配目的地=“hdlcoder_sfir_fixed_stream / DUT / y_out_data”# # #高亮显示CP1从“hdlcoder_sfir_fixed_stream / DUT symmetric_fir / m3_out1 '来“hdlcoder_sfir_fixed_stream / DUT / y_out_data”…# # #点击在这里来重置突出显示。# # #的工作流程完成了。

运行工作流交互

高密度脂蛋白工作流也可以使用命令行界面交互。例如,在运行整个脚本或只是“工作流配置设置”部分,WorkflowConfig对象,中国,将在工作区中填充:

> >中国=

GenericTurnkeyConfig属性:

SynthesisTool:“Xilinx Vivado TargetWorkflow:“通用ASIC / FPGA”ProjectFolder:“hdl_prj”

RunTaskGenerateRTLCodeAndTestbench:真RunTaskCreateProject:真RunTaskRunSynthesis:真RunTaskRunImplementation:真的RunTaskAnnotateModelWithSynthesisResult:真的

TaskGenerateRTLCodeAndTestbench GenerateRTLCode:真GenerateRTLTestbench:假GenerateCosimulationModel:假CosimulationModelForUseWith:“导师图形ModelSim”GenerateValidationModel:假的

TaskCreateProject目标:hdlcoder.Objective。SpeedOptimized AdditionalProjectCreationTclFiles:“

TaskRunSynthesis SkipPreRouteTimingAnalysis:假

TaskRunImplementation IgnorePlaceAndRouteErrors:假

TaskAnnotateModelWithSynthesisResult CriticalPathSource:“pre-route”CriticalPathNumber: 1 ShowAllPaths:假ShowDelayData:真正的ShowUniquePaths:假ShowEndsOnly:假

您可以编辑此配置对象,然后运行工作流与修改后的设置。例如,由于任务启用“运行实现”是在前面跑,我们可以改变关键路径源“支应”并重新运行就标注模型的任务:

> > hWC.clearAllTasks;> >中国。RunTaskAnnotateModelWithSynthesisResult = true;> >中国。CriticalPathSource =“可支应”;

然后运行修改后的工作流配置直接使用hdlcoder.runWorkflow命令:

> > hdlcoder.runWorkflow (“hdlcoder_led_blinking / led_counter”,中国)

脚本导入HDL工作流顾问

你做任何更改导出的脚本也可以进口回HDL工作流顾问在任何时间。要做到这一点,确保模型加载是一样的模型中使用的脚本,并选择“导入脚本”从文件菜单。

导入后,所有的脚本设置将填充高密度脂蛋白工作流顾问。

保存HDL工作流命令行界面编程脚本供以后使用

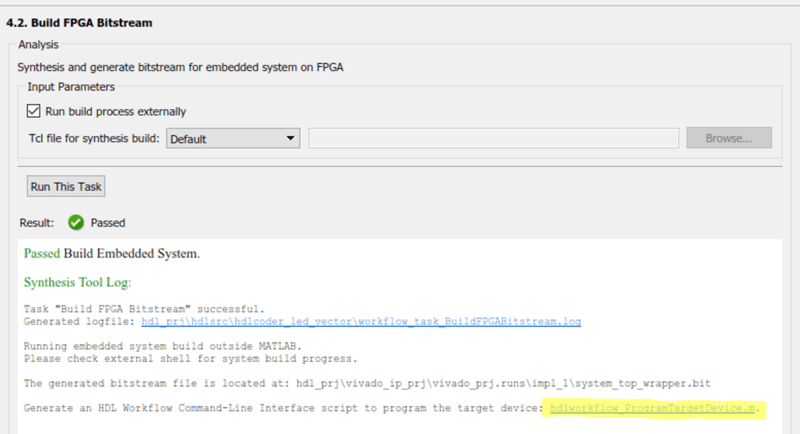

在某些情况下,你可以避免重新运行的所有步骤的HDL工作流顾问顾问来执行特定的任务。例如,当运行的IP核心代工作流,在您生成的FPGA比特流构建FPGA比特流任务,顾问提供了一个链接,生成一个脚本运行项目目标设备的任务。

点击的链接hdlworkflow_ProgramTargetDevice.m在构建FPGA比特流任务生成一个高密度脂蛋白工作流将只执行脚本命令行界面项目目标设备任务从现有hdl_prj目录。因此,您可以避免在工作流运行的所有步骤re-program目标设备。

生成的脚本是一个标准的HDL工作流CLI脚本。在命令行界面HDL工作流运行时,项目目标设备任务可以独立运行之前的任务,只要FPGA比特流已经生成。

作为一个相关的注意,如果您正在使用下载编程方法项目目标设备任务,高密度脂蛋白工作流顾问生成的位流文件拷贝到SD卡Zynq或英特尔SoC,所以您不需要重新运行项目目标设备任务下载比特流。FPGA比特流将从SD卡自动重新加载Linux启动过程中。

总结

高密度脂蛋白工作流命令行界面提供了一个容易照本宣科替代图形HDL工作流顾问。工作流可以使用HDL工作流设置最初顾问然后出口到脚本迭代或自动使用。