SoC平台软硬件协同设计工作流

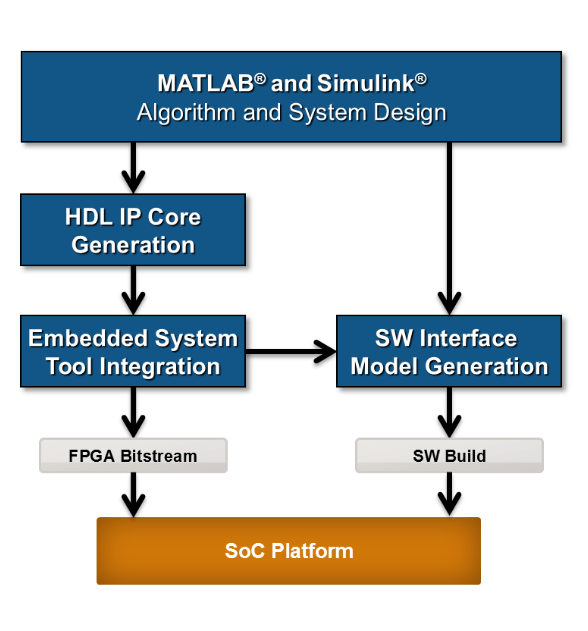

HDL Coder™硬件-软件协同设计工作流有助于自动部署MATLAB®和仿真软金宝app件®设计Zynq®-7000平台或Intel®SoC的平台。通过迭代以下工作流,您可以探索划分和部署设计的最佳方法。

MATLAB与Simu金宝applink算法与系统设计你首先在MATLAB或Simulink中实现你的设计。金宝app当设计行为满足您的需求时,决定如何划分设计:哪些部分希望在硬件中运行,哪些部分希望在嵌入式软件中运行。

您想要在硬件中运行的设计部分必须使用MATLAB语法或Simulink块,它们支持并配置为用于HDL代码生成。金宝app金宝app看到的:

HDL IP核生成:将设计的硬件部分封装在原子中子系统块或MATLAB函数,并使用HDL Workflow Advisor定义和生成一个HDL IP核。

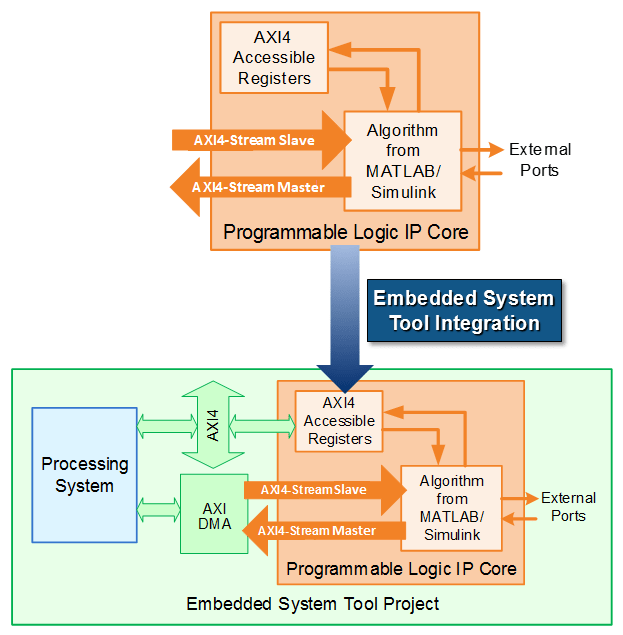

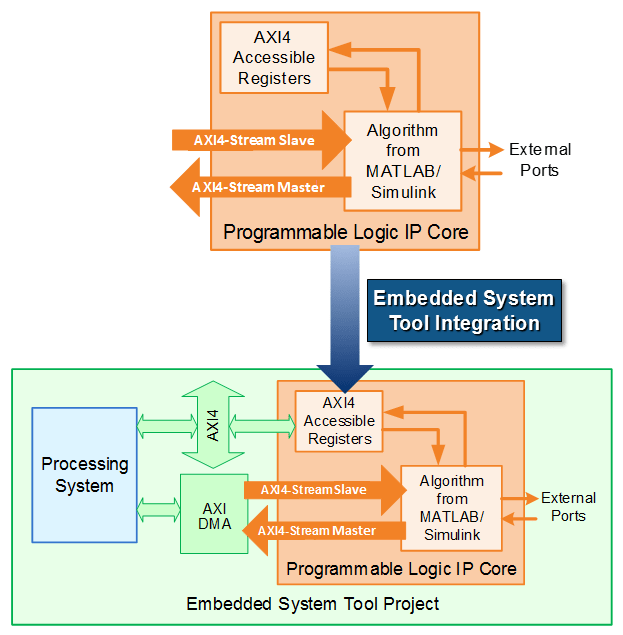

下图显示了被划分为橙色的硬件部分和蓝色的软件部分的设计。HDL IP核生成从模型的硬件部分创建一个IP核。IP核心包括硬件接口组件,如AXI4可访问寄存器、AXI4或AXI4- lite接口、AXI4- stream或AXI4- stream视频接口、AXI4主接口和外部端口。

嵌入式系统工具集成作为HDL Workflow Advisor IP核生成工作流的一部分,您可以将生成的IP核插入到参考设计,并为SoC硬件生成FPGA位流。

的参考设计是一个预定义的嵌入式系统集成项目。它包含英特尔或Xilinx的所有元素®软件需要将您的设计部署到SoC平台,除了您生成的自定义IP核和嵌入式软件。

下图说明了参考设计(绿色)和生成的IP核(橙色)之间的关系。

软件界面生成(需要Simulink许金宝app可证和嵌入式编码器®在HDL Workflow Advisor中,当您生成IP核并将其插入到参考设计中后,您可以选择生成一个软件接口模型和一个软件接口脚本。软件接口模型是您原来的模型,用AXI驱动块替换了硬件部分。该脚本是基于参考设计和Target平台接口表设置而生成的MATLAB文件。它包含命令,使您能够连接到目标硬件,并通过使用AXI驱动程序块对生成的IP核进行读写操作。

如果您有Embedded Coder许可证,您可以自动生成软件接口模型和脚本,从中生成嵌入式代码,并在Linux上构建和运行可执行文件®ARM上的内核®处理器。生成的嵌入式软件包括由控制HDL IP核的AXI驱动块生成的AXI驱动代码。

如果您没有Embedded Coder许可证或Simulink许可证,您可以编写嵌入式软件,并手金宝app动为ARM处理器构建它。看到生成软件接口脚本探测和快速原型HDL IP核

下图展示了原始模型与软件界面模型的区别。

SoC平台和外部模式公益诉讼:使用HDL Workflow Advisor,可以将FPGA位流编程到SoC平台。然后,您可以在外部模式或环中处理器(PIL)模式下运行软件接口模型,以测试已部署的设计。

如果您部署的设计不能满足您的设计需求,您可以使用修改过的模型或不同的硬件-软件分区重复工作流。