没有嵌入式臂处理器的IP核心生成工作流程:箭头Deca Max 10 FPGA评估套件

此示例显示了如何使用HDL Coder™IP核心生成工作流程为没有嵌入式ARM®处理器的Intel®零件开发参考设计,但仍然利用HDL Coder™生成的AXI接口来控制DUT。此示例使用MATLAB作为AXI Master IP从HDL Verifer™通过启用参考设计参数选项来访问HDL Coder™生成的DUT寄存器将JTAG MATLAB插入AXI Master。然后,您可以直接从Matlab访问DUT寄存器。或者,您可以将Intel Qsys(TM)JTAG使用到Avalon Master Bridge IP,以在Qsys系统控制台中使用TCL命令访问FPGA寄存器。对于英特尔JTAG AXI Master,您需要创建自定义参考设计。FPGA设计在箭头Deca Max 10 FPGA评估套件上实现。

要求

英特尔Quartus Prime,其中包含了支持的版金宝app本HDL编码器文档

arrow deca max 10 fpga评估套件

英特尔FPGA板的HD金宝appL编码器™支持包

HDL Verifier™支金宝app持套装用于英特尔FPGA板(可选)

HDL Coder™支金宝app持英特尔SOC设备的支持包(可选:将IP内核集成到您自己的自定义参考设计中。)

arrow deca max 10 fpga评估套件

示例参考设计

有许多设计将受益于使用HDL Coder™IP核心生成工作流程,而无需使用嵌入式ARM®处理器或嵌入式编码器™支持包,但仍然利用HDL Coder™生成的AXI4寄存器。金宝app这些设计包括:

HDL Verifier™MATLAB作为AXI Master + HDL Coder™IP核心

JTAG Master + HDL Coder™IP核心

NIOS®II+ HDL编码器™IP核心

PCIe®终点+ HDL Coder™IP核心

此示例中包含两个参考设计:

这

默认系统参考设计使用MathWorks IP和MATLAB命令行界面来通过启用参考设计参数选项“将JTAG MATLAB作为AXI Master插入JTAG MATLAB”来发出读写命令。请注意,要使用此参数,必须安装HDL Verifier™。

这

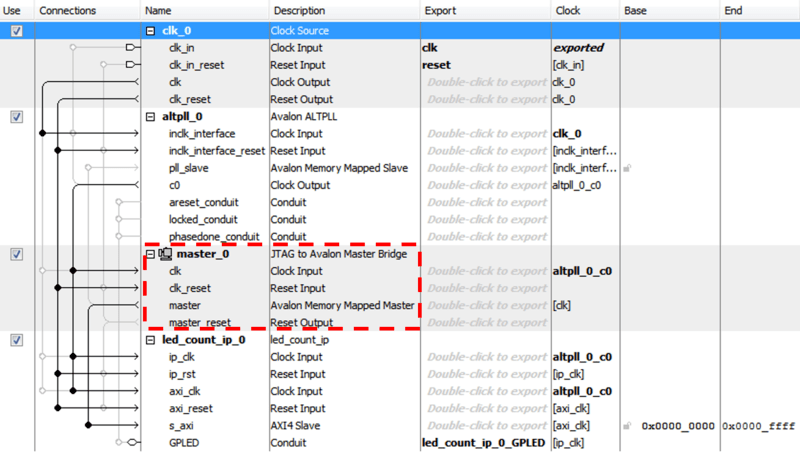

英特尔JTAG到AXI Master参考设计使用JTAG的Quartus IP到Axi Master,因此需要使用Quartus TCL控制台来发出读写。

除了框图中显示的JTAG主IP,两个参考设计几乎相同。

参考设计“Altera JTAG到Axi Master”,使用QSYS™IP为JTAG到AXI Master,因此需要使用英特尔®系统控制台来发出读取和写入:

1. HDL Verifer™MATLAB作为AXI主参考设计

指定将JTAG MATLAB插入AXI主站(需要HDL验证器)到在在里面设置目标参考设计任务IP核心生成工作流程。这将Matlab Axi Master IP自动添加到参考设计中,并使用Axi4从接口连接到DUT IP。在以下部分讨论了在参考设计中自动插入MATLAB JTAG AXI主站的详细步骤。

执行IP核心工作流程

本节中的以下说明适用于默认系统参考设计使用Matlab JTAG作为AXI Master。使用此参考设计,您可以生成闪烁Deca Loard上的LED的HDL IP核心。

1.设置Intel Quartus™工具路径。使用本地安装替换Quartus™安装路径

hdl setuptoolpath('toolname'那'Altera Quartus II'那'工具路径'那'C:\ intelfpga \ 18.1 \ quartus \ bin64 \ quartus.exe');

2.打开使用命令实现LE金宝appD闪烁的Simulink模型:

Open_System('hdlcoder_led_blinking')

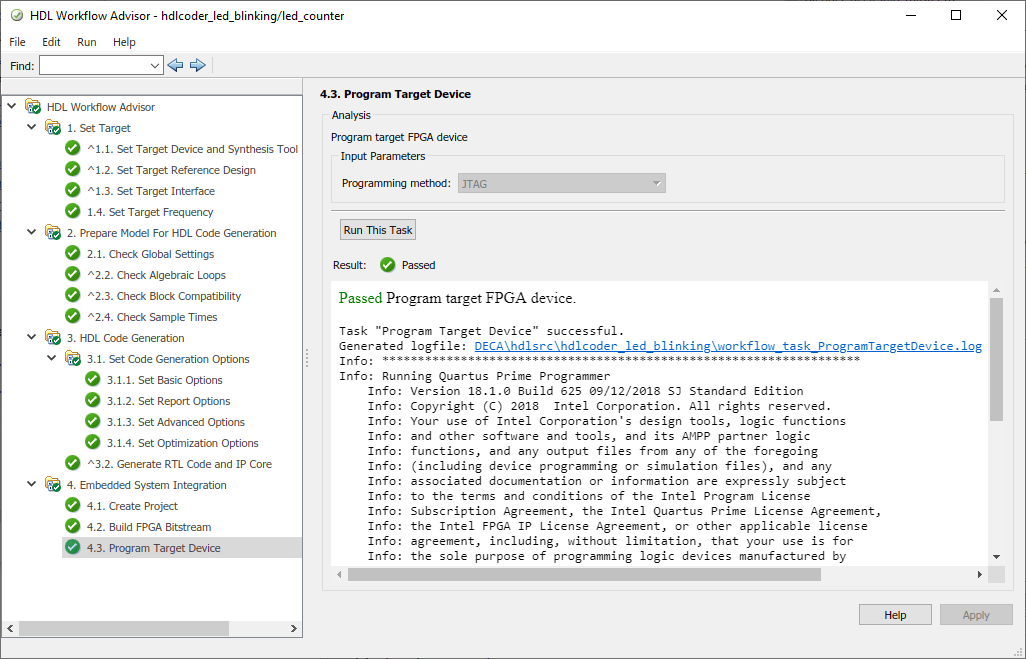

3.启动HDL工作流程顾问hdlcoder_led_blinking / led_counter.右键单击子系统LED_COUNTER.子系统,选择HDL码>HDL工作流程顾问。

4.在设定目标>设置目标设备和合成工具任务,for.目标工作流程, 选择IP核心生成, 为了目标平台, 选择arrow deca max 10 fpga评估套件然后点击运行此任务运行设置目标设备和合成工具任务

5.在设定目标>设置目标参考设计任务,选择默认系统作为参考设计和设置将JTAG MATLAB插入AXI Master下拉选择在其中存在于参考设计参数选项中。

6.在设定目标>设置目标接口任务,选择AXI4.为了blink_frquency那blink_direction., 和回过头再读。选择LED通用[0:7]为了引领。

7.在工作流中运行剩余步骤以生成比特流并编程目标设备。

请注意,与英特尔SOC的参考设计不同,没有“生成软件界面模型”任务。这在下图中示出。

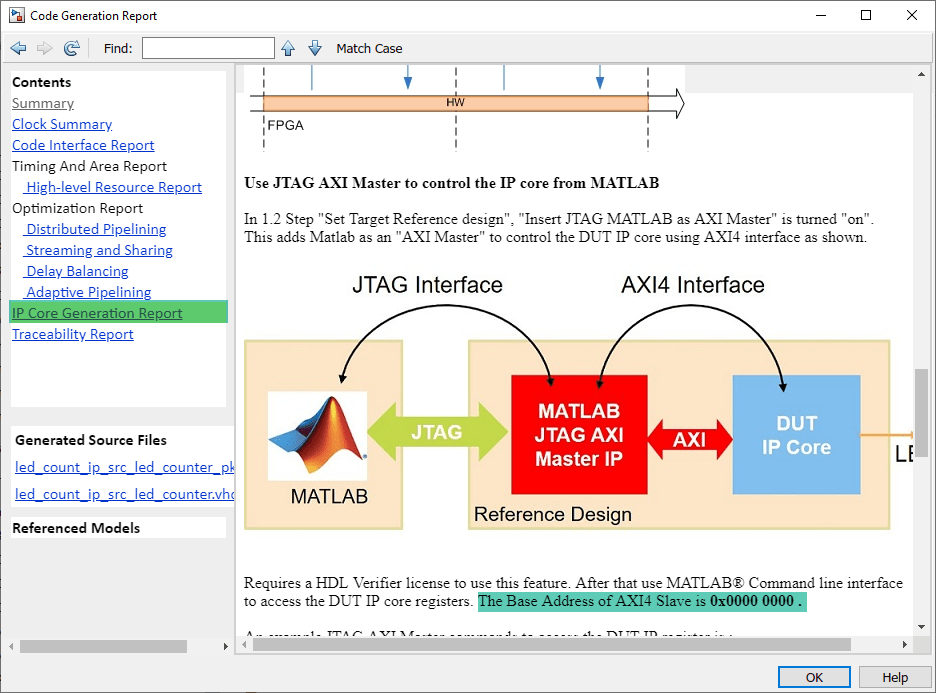

确定IP核心报告的地址

HDL Coder™IP内核的基础地址定义为0x00000000为了默认系统参考设计使用MATLAB AXI Master IP。您可以在生成的IP核心报告中看到此,如下图所示。

可以在IP核心报告寄存器地址映射表中找到偏移量:

HDL验证程序命令行界面

如果安装了英特尔FPGA板的HD金宝appL验证器支持包,并且选择了“MATLAB作为AXI主站”参考设计,则可以使用简单的MATLAB命令行界面来访问HDL编码器生成的IP内核。

1.创建AXI主对象

h = aximaster('Altera')

2.发出简单的写命令。例如,禁用DUT

H.WriteMemory('4',0)

3.要重新启用DUT,请使用以下写命令

H.WriteMemory('4'1)

4.读取当前计数器值

h.readmemory('108'1)

5.删除对象以释放JTAG资源。如果未删除对象,则其他JTAG操作(例如编程FPGA)将失败。

删除(h)

英特尔JTAG AXI主参考设计

您需要创建要使用的自定义参考设计英特尔JTAG AXI Master在参考设计中,然后将参考设计文件添加到MATLAB路径addpath.命令。

要使用Intel JTAG AXI Master访问HDL Coder™IP核心寄存器,基地址在参考设计插件文件中定义。

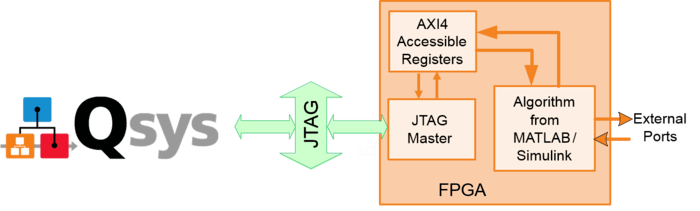

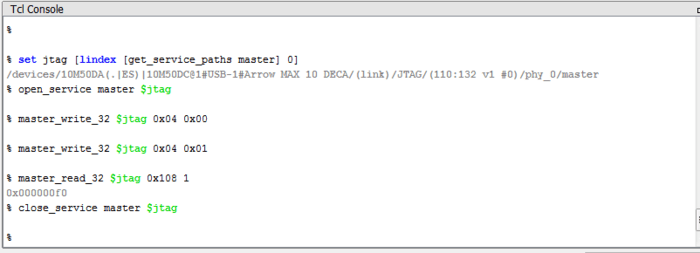

QSYS系统控制台TCL用于AXI读写的命令

在我们打开系统控制台之前,请允许查看发出读写的基本命令。有许多QSYS读写方法的口味,但我们将使用以下内容,因为所有HDL Coder™生成的IP核心寄存器都是32位:

%master_write_32%master_read_32

例如,假设我们希望将32位十六进制值'0x12345678'编写到由偏移'0x100'定义的IP核心寄存器,使用以前定义的服务路径存储在变量中$ JTAG.:

%master_write_32 $ jtag 0x100 0x12345678

在生成读取和写入之前,必须首先启动系统控制台并打开与JTAG Master的连接,该主机将发出寄存器读写。再次参考下面的系统图:

要打开与JTAG Master的连接,请先设置存储服务路径的变量(在这种情况下,只有一个主设备):

%set jtag [lindex [get_service_path master] 0]

然后使用变量以在主模式下打开JTAG主站。

%Open_Service Master $ JTAG

现在启动Altera®系统控制台并输入打开JTAG Master的命令:

>>系统('c:\ intelfpga \ 17.1 \ quartus \ sopc_builder \ bin \ system-console&')

使用JTAG Master完成后,请务必使用以下TCL命令关闭连接:

close_service master $ jtag

概括

使用JTAG到AXI Master是一种简单的方法,可以在没有嵌入式ARM®处理器的系统中与HDL Coder™IP内核寄存器接口,例如最大10.这可以用作调试独立HDL的第一步Coder™IP核心,在手动编码软件之前用于软处理器,例如Nios®II,或作为运行系统上的参数的简单方法。