入门SystemVerilog的DPI组件生成

这个例子展示了如何从在Simulink®中模型比例 - 积分 - 微分(PID)控制器的SystemVerilog一个DPI成分,其导出到HDL仿真。金宝app

要求和先决条件

下载188bet金宝搏在这个例子中所需的产品:

MATLAB®

金宝app的Simulink

金宝appSimulink的Coder®

一种支持HDL仿真器:金宝app导师Graphics®的ModelSim®/QuestaSim®或Cadence的精辟

一种支持的C编译器:微金宝app软的Visual C ++或GNU GCC

建立模型的代码生成

打开从svdpi_金宝apppid模型Simulink模型配置参数面板。设置以下参数:

选择代码生成 - >系统目标文件。单击浏览按钮,选择“systemverilog_dpi_grt.tlc”。

如果你已经嵌入式编码所以您可以选择的“叔”的目标文件,如下图所示的图。

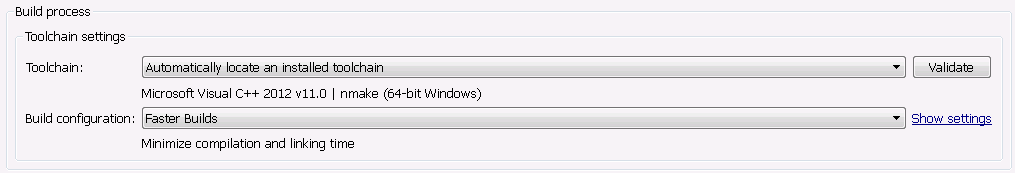

在工具链的设定,选择Visual Studio的版本之一,如果你使用的是Windows,或者如果您使用的是Linux的GCC工具链中的一个。

请确保选择“生成代码只有”未选中。

选择代码生成 - > SystemVerilog的DPI,并勾选“生成试验台”

现在,我们正在与配置参数面板来完成。点击“确定”按钮将其关闭。

选择测试点记录内部信号(可选)

如果你有兴趣在访问中的SystemVerilog环境DPI-C成分的内部信号,那么你可以使用DPI-C测试点记录功能。

第一步是选择要访问的信号。您可以通过右击做到这一点的兴趣,并选择“属性”的信号。

在该对话框中选择标记为“测试点”复选框,并发出信号的标签在“信号名称”。注:建议给出信号名称中的“信号名称”每一个测试点,否则这将是很难的信号映射到生成的代码。

如果你也有兴趣在获取内部信号的测试向量,并播放所生成的测试平台,然后选择“考试”和“日志信号数据”复选框。

第二个步骤是使由嵌入式编码提供的C API。要做到这一点去的配置参数窗格和代码生成 - >接口确保至少“信号”复选框被选中。

第三步骤是选择的将被用于访问测试点的SystemVerilog功能的接口。- > SystemVerilog的DPI - >测试点接入功能代码生成:这是通过选择从下拉下完成的下拉菜单

如果您选择“无”则标志着测试点都将被忽略,并没有接入功能将会产生。

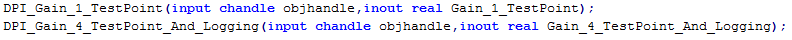

选择“每个测试点一个功能”将允许你独立访问每个测试点。如果选择了这个选项,对于本例所产生的界面被示出如下:

选择“为所有测试点的一个功能”将让你与一个函数调用访问所有的测试点。如果选择了这个选项,对于本例所产生的界面被示出如下:

运行生成的测试台后,你可以看到波形信号。

请注意,对于“Gain_1_TestPoint”有没有参考值与比较,因为我们只检查了“考试”复选框前面。在本作除了接入功能“Gain_4_TestPoint_And_Logging”对比也有参考值与比较。

生成的SystemVerilog DPI组件

在“svdpi_pid”模式,右键单击控制器块,并选择C / C ++代码 - >构建这个子系统。

在对话框出现单击生成。

所述的SystemVerilog部件作为“Controller_build / Controller_dpi.sv”生成。当完成代码生成,检查新的组件。

运行生成的试验台

对于的ModelSim / QuestaSim,

开始的ModelSim / QuestaSim在GUI模式。

更改你的HDL仿真器的代码生成目录下的当前目录切换到“dpi_tb”。

输入以下命令来启动你的模拟

做run_tb_mq.do

对于精辟模拟器:

启动终端外壳

将当前目录更改为“dpi_tb”代码生成目录下

在你的shell中输入以下命令。

SH run_tb_incisive.sh

对于VCS模拟器:

启动终端外壳

将当前目录更改为“dpi_tb”代码生成目录下

在你的shell中输入以下命令。

SH run_tb_vcs.sh

当模拟完成后,你应该看到在控制台打印以下文字:

**************测试已完成(通过)**************