仿真时间尺度

概述模拟时间的表示

HDL模拟器和Simulink之间的模拟时间表示明显不同金宝app®。Each application has its own timing engine and the verification software must synchronize the simulation times between the two.

在HDL模拟器中,模拟时间单位称为tick。这duration of a tick is defined by the HDL simulator分辨率限制。默认的分辨率限制为1 ns,但根据模拟器的不同。

ModelSim®用户:

要确定当前模型限制限制,请输入

回声$分辨率or报告模拟器状态at the ModelSim prompt. You can override the default resolution limit by specifying the-toption on the ModelSim command line, or by selecting a different Simulator Resolution in the ModelSim Simulate dialog box. Available resolutions in ModelSim are 1x, 10x, or 100x in units of fs, ps, ns, us, ms, or sec. See the ModelSim documentation for further information.Incisive®用户:

To determine the current HDL simulator resolution limit, enter

Echo $ $时间尺度at the HDL simulator prompt. See the HDL simulator documentation for further information.

金宝appSimulink将仿真时间保持为缩放到秒的双精度值。该表示形式适合连续和离散系统的建模。

Simulink与HDL模拟器时机之间的关系影响了金宝app以下各个方面:

Total simulation time

输入端口样本时间

输出端口样本时间

Clock periods

During a simulation run, Simulink communicates the current simulation time to the HDL simulator at each intermediate step. (An intermediate step corresponds to a Simulink sample time hit. Upon each intermediate step, new values are applied at input ports, or output ports are sampled.)

To bring the HDL simulator up-to-date with Simulink during cosimulation, you must convert sampled Simulink time to HDL simulator time (ticks) and allow the HDL simulator to run for the computed number of ticks.

Defining the金宝app和HDL模拟器正时关系

这differences in the representation of simulation time can be reconciled in one of two ways using the HDL Verifier™ interface:

By defining the timing relationship manually (with时间尺度pane)

当您手动定义关系时,您会确定HDL Simulator中的数量,毫秒,微秒,毫秒,秒,秒或tick s代表Simulink 1秒的数量。金宝app

通过允许HDL验证者定义时间表(使用时间尺度pane)

When you allow the software to define the timing relationship, it attempts to set the timescale factor between the HDL simulator and Simulink to be as close as possible to 1 second in the HDL simulator = 1 second in Simulink. If this setting is not possible, HDL Verifier attempts to set the signal rate on the Simulink model port to the lowest possible number of HDL simulator ticks.

设置定时模式HDL验证者

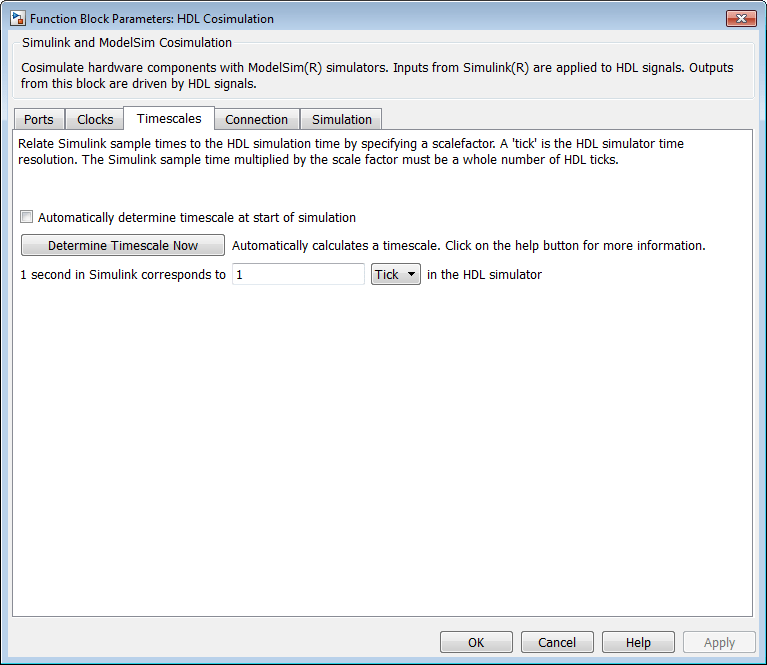

这时间尺度窗格HDL Cosimulation块参数对话框定义了Simulink时间的一秒钟和一定数量的HDL模拟器时间之间的对应关系。金宝app这一数量的HDL模拟器时间可以通过以下方式表示:

In相对的术语(即,作为一定数量的HDL模拟器滴答)。在这种情况下,据说共拟合在相对计时模式。这HDL Cosimulation block defaults to relative timing mode for cosimulation. For more on relative timing mode, seeRelative Timing Mode。

In绝对单位(例如毫秒或纳秒)。在这种情况下,据说共拟合在绝对定时模式。有关绝对计时模式的更多信息,请参阅Absolute Timing Mode。

这时间尺度窗格使您可以通过输入HDL模拟器等效或让HDL验证器为您计算一个时间表,从而选择Simulink和HDL模拟器之间的最佳金宝app定时关系。

You can choose to have HDL Verifier calculate a timescale while you are setting the parameters on the block dialog by clicking the时间尺度选项然后单击Determine Timescale Now或者,您可以让HDL验证者计算模拟开始时计算时间表在仿真开始时自动确定时间尺度。

下图显示了时间尺度窗格(显示的示例用于与Modelsim一起使用)。

For instructions on setting the timing mode either manually or with the时间尺度对话框,查看时间尺度pane in theHDL Cosimulationblock reference.

自动指定定时关系

To have the HDL Verifier software calculate the timing relationship for you:

Start the HDL simulator. HDL Verifier software can obtain the resolution limit of the HDL simulator only when that simulator is running.

Choose to have HDL Verifier software suggest a timescale, immediately, or calculate the timescale when you start the Simulink simulation.

To have the calculation performed while you are configuring the block, on the时间尺度选项卡,单击Determine Timescale Now。这software connects Simulink with the HDL simulator so that Simulink can use the HDL simulator resolution to calculate the best timescale. The link then displays those results to you in the时间尺度Details对话框。

笔记

For the results to display, make sure that the HDL simulator is running and the design is loaded for cosimulation. The simulation does not have to be running.

您可以接受建议的时间表,或直接更改端口列表:

要恢复最初计算的设置,请单击使用建议的时间尺度。

要查看HDL设计中所有端口的样本时间,请选择Show all ports and clocks。

To have the calculation performed when the simulation begins, select在仿真开始时自动确定时间尺度,然后单击申请。You obtain the same时间尺度Details对话框当模拟从Simulink开始时。金宝app

笔记

For the results to display, make sure that the HDL simulator is running and the design is loaded for cosimulation. The simulation does not have to be running.

HDL验证者software analyzes all the clock and port signal rates from the HDL Cosimulation block when the software calculates the scale factor.

笔记

HDL验证器软件无法根据通过TCL命令或HDL模拟器中驱动的任何信号自动计算样本时间尺度。链接软件无法执行此类计算,因为它无法知道这些信号的速率。

这link software returns the sample rate in either seconds or ticks:

If the results are in seconds, then the link software was able to resolve the timing differences in favor of fidelity (absolute time).

如果结果在刻度中,则链接软件最好能够解决定时差异,以支持效率(相对时间)。

每次选择Determine Timescale Nowor在仿真开始时自动确定时间尺度,交互式显示打开。此显示说明了时间尺度计算的结果。如果链接软件无法计算给定的采样时间的时间尺度,请调整您的样本时间端口列表。

点击申请to commit your changes.

笔记

HDL验证者does not support timescales calculated automatically from frame-based signals.

Relative Timing Mode

Relative timing mode defines the following one-to-one correspondence between simulation time in Simulink and the HDL simulator:

One secondin Simulink corresponds tonticksin the HDL simulator, wherenis a scale factor. |

无论HDL模拟器时序分辨率如何,此对应关系都具有。

以下伪代码显示了如何将Simulink时间单元转换为HDL Simul金宝appator Tick:

inticks = n * tinsecs

在哪里插件是tick中的HDL模拟器时间吗?tInSecsis the Simulink time in seconds, andnis a scale factor.

相对计时模式的操作

这HDL Cosimulationblock defaults to relative timing mode, with a scale factor of 1. Thus, 1 Simulink second corresponds to 1 tick in the HDL simulator. In the default case:

如果将Simulink中的总仿真时间指定为金宝app

n秒,然后HDL模拟将完全运行nticks (i.e.,nns处于默认分辨率限制)。同样,如果Simulink计金宝app算HDL Cosimulation块输入端口为Tsiseconds, new values will be deposited on the HDL input port at exact multiples ofTsiticks. If an output port has an explicitly specified sample time ofTso秒,将从HDL模拟器读取值Tsoticks.

相对时机模式示例

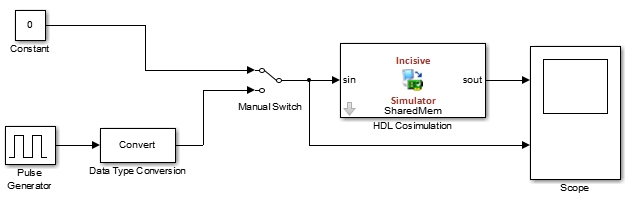

To understand how relative timing mode operates, review cosimulation results from the following example model.

Absolute Timing Mode

Absolute timing mode lets you define the timing relationship between Simulink and the HDL simulator in terms of absolute time units and a scale factor:

| One secondin Simulink corresponds to(N * Tu) secondsin the HDL simulator, wheretu是绝对时间单元(例如,MS,NS等)和nis a scale factor. |

In absolute timing mode, all sample times and clock periods in Simulink are quantized to HDL simulator ticks. The following pseudocode illustrates the conversion:

tInTicks = tInSecs * (tScale / tRL)

在哪里:

tInTicks是tick中的HDL模拟器时间。tInSecs是几秒钟内的模金宝app拟时间。tScale是在时间尺度窗格HDL Cosimulation堵塞。tRLis the HDL simulator resolution limit.

For example, given a时间尺度窗格设置为1 s,HDL模拟器分辨率限制为1 ns,输出端口样本时间为12 ns,将转换为tick,如下:

tInTicks = 12ns * (1s / 1ns) = 12

绝对计时模式的操作

To configure the Timescales parameters for absolute timing mode, you select a unit of absolute time that corresponds to a Simulink second, rather than selectingTick。

绝对计时模式示例

To understand the operation of absolute timing mode, you will again consider the example model discussed in相对计时模式的操作。Suppose that the model is reconfigured as follows:

Simulink中的仿真参数:金宝app

时间尺度参数:

1 sof Simulink time corresponds to1 sof HDL simulator time.Total simulation time:

60e-9 s(60ns)输入端口(

/逆变器/INPORT)sample time:24e-9 s (24 ns)Output port (

/inverter/outport)sample time:12e-9 s (12 ns)钟 (

逆变器/clk)period:10e-9 s (10 ns)

HDL模拟器分辨率限制:

1 ns

Given these simulation parameters, the Simulink software will cosimulate with the HDL simulator for 60 ns, during which Simulink will sample inputs at a intervals of 24 ns, update outputs at intervals of 12 ns, and drive clocks at intervals of 10 ns.

下图显示了模型海浪共同模拟后的窗口。

定时模式使用率注意事项

设置时间尺度模式时,您可能需要根据以下注意事项选择设置。

时序模式使用限制

这following restrictions apply to the use of absolute and relative timing modes:

当多个HDL Cosimulation模型中的块正在与HDL模拟器的单个实例进行通信,HDL Cosimulation块必须具有相同的时间尺度窗格设置。

If you change the时间尺度窗格设置HDL Cosimulation块之间的连续cosimulation运行,你米ust restart the simulation in the HDL simulator.

如果您指定无法表示为全数HDL t金宝appick的simulink示例时间,则会遇到错误。

非企业时间段

当使用非智能时间段时,HDL模拟器不能代表这种无限重复值。因此,模拟器会截断时间段,但其确实与模拟截断值的方式不同,两个时间段不再匹配。金宝app

以下示例演示了如何在以下情况下设置定时关系: 在Si金宝appmulink中,对应于非企业时间段。

这key idea here is that you must always be able to relate a Simulink time with an HDL tick. The HDL tick is the finest time slice the HDL simulator recognizes; for ModelSim, the default tick is 1 ns, but it can be made as precise as 1 fs.

但是,3 Hz信号实际上具有333.33333333333 ... MS的周期,这对于HDL模拟器而言不是有效的刻度周期。HDL模拟器将截断此类数字。但是Si金宝appmulink并没有做出相同的决定;因此,对于您试图使两个独立的模拟器同步的共同模拟,您不应假设任何事情。相反,您必须确定是否方便截断或围成数字。

这refore, the solution is to "snap" either the Simulink sample time or the HDL sample time (via the timescale) to valid numbers. There are infinite possibilities, but here are some possible ways to perform a snap:

将SIMULI金宝appNK样本时间从1/3秒更改为0.33333 sec,并将“ simulink in simulink in simulink = 1秒”中的“ 1秒”设置为HDL模拟器中的“ 1秒”。如果您在HDL Cosimulationblock时钟pane, its period should be 0.33333 sec.

Keep Simulink sample times at 1/3 sec. and 1 second in Simulink = 6 ticks in the HDL simulator.

如果您在HDL Cosimulationblock时钟窗格,其周期应为1/3。简而言之,该规范告诉Simulink使每个Simulink样本时间对金宝app应于每个(1/3*6)= 2个滴答,而不论HDL时间分辨率如何。

If your default HDL simulator resolution is 1 ns, that means your HDL sample times are every 2 ns. This sample time will work in a way so that for every Simulink sample time there is a corresponding HDL sample time.

但是,Simuli金宝appnk以1/3秒的时间和HDL思考2 NS时期。因此,在调试期间,您可能会感到困惑。如果您希望它匹配真实时期(例如5个位置,即333.33毫秒),则可以按照列出的下一个选项。

将SIMU金宝appLINK样品时间保持在1/3秒,在Simulink中保持1秒钟的= 0.999999E9在HDL模拟器中滴答作响。如果您在HDL Cosimulationblock时钟窗格,其周期应为1/3。

SettingHDL Cosimulation块端口样本时间

通常,Simulink处金宝app理一个端口的样本时间HDL Cosimulation块如下:

如果将输入端口连接到具有显式示例时间的信号,则基于正向传播,Simulink将该速率应用于该输入端口。金宝app

If an input port is connected to a signal thatdoes not havean explicit sample time, Simulink assigns a sample time that is equal to the least common multiple (LCM) of all identified input port sample times for the model.

After Simulink sets the input port sample periods, it applies user-specified output sample times to all output ports. Sample times must be explicitly defined for all output ports.

如果您正在开发用于共同拟议的模型相对的timing mode, consider the following sample time guideline:

指定输出样本时间HDL Cosimulation块作为HDL模拟器中定义的分辨率限制的整数倍数。使用HDL模拟器命令报告模拟器状态to check the resolution limit of the loaded model. If the HDL simulator resolution limit is 1 ns and you specify a block's output sample time as 20, Simulink interacts with the HDL simulator every 20 ns. |