生成图像锐化的HDL代码

此示例显示如何使用Vision HDL Toolbox™来实现基于FPGA的模块以进行图像锐化。

Vision HDL Toolbox提供旨在在VHDL和Verilog中生成可读,可合成的代码的图像和视频处理算法(使用HDL编码器™)。在FPGA上运行时的生成的HDL代码(例如,Xilinx XC7Z045)可以在每秒60帧的60帧中处理1920x1080全分辨率图像。

此示例显示如何使用Vision HDL Toolbox生成锐化模糊图像的HDL代码。由于Vision HDL Toolbox算法可用作Matlab®System对象™和Simulink®块,因此可以从Matlab或Simulink生成HDL代码。金宝app此示例显示了两个工作流程。

FPGA目标设计的工作流程是:

1.创建一个行为模型以表示设计目标;

2.使用适合FPGA的算法,接口和数据类型复制设计并支持HDL代码生成。金宝app

3.模拟两种设计,并比较结果确认HDL优化的设计符合目标。

4.从步骤2中创建的设计生成HDL代码。

对于MATLAB中的步骤2和3,您必须有MATLAB、Vision HDL工具箱和Fixed-Point Designer™。在Si金宝appmulink中,您需要Simulink、Vision HDL工具箱和定点设计器。在这两种情况下,您都必须使用HDL Coder来生成HDL代码。

行为模型

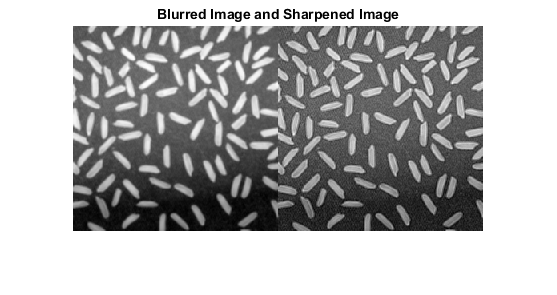

输入图像imgBlur如下图的左侧所示。在右侧,使用image Processing Toolbox™函数锐化图像Imfilter..

模拟时间被打印为未来比较的台式标记。

imgblur = imread(“riceblurred.png”);sharpcoeff = [0 0 0; 0 1 0; 0 0 0] -fspecial(的拉普拉斯算子,0.2);f = @()imfilter(imgblur,sharpcoeff,'对称');流('经过时间是%.6f秒。\ n',Timeit(f));imgsharp = imfilter(imgblur,sharpcoeff,'对称');图imshowpair(Imgblur,Imgsharp,“蒙太奇”) 标题('模糊图像和锐化的图像')

经过时间为0.000557秒。

HDL-Optimized设计注意事项

要启用HDL代码生成,需要进行三个关键的更改。

使用流媒体像素接口:从图像处理工具箱模型处于高级抽象的功能。它们执行全帧处理,一次在一个图像帧上运行。然而,FPGA和ASIC实现执行像素流处理,一次在一个图像像素上操作。Vision HDL工具箱块和系统对象使用流媒体像素接口。用

Visionhdl.frametopixels.MATLAB中的系统对象或帧像素块,以将全帧图像或金宝app视频转换为像素流。流像素接口包括指示帧中每个像素位置的控制信号。在像素邻域上操作的算法使用内部存储器来存储最少的行数。Vision HDL工具箱提供了流式像素接口和自动内存实现,以解决针对fpga和asic的常见设计问题。有关Vision HDL工具箱中系统对象使用的流式像素协议的更多信息,请参见流媒体像素接口(Vision HDL工具箱).

使用定点数据表示:来自图像处理工具箱的功能在浮点或整数域中执行视频处理算法。来自Vision HDL Toolbox的系统对象和块需要固定点数据以生成HDL代码来定位FPGA和ASIC。将设计转换为固定点可以引入量化误差。因此,HDL友好的模型可能产生与从行为模型中获得的输出略有不同。对于大多数应用,公差内的小量化误差是可接受的。您可以调整固定点设置以满足您的要求。

在本例中,我们使用静态图像作为源。该模型还能处理连续视频输入。

从Matlab生成HDL代码

要从MATLAB生成HDL,您的代码需要分成两个文件:测试台和设计。设计文件用于在FPGA或ASIC中实现算法。测试台文件向设计文件提供输入数据并接收设计输出。

步骤1:创建设计文件

功能Imagesharpeninghdldesign.m.接受像素流和由五个控制信号组成的控制结构,并返回修改的像素流和控制结构。

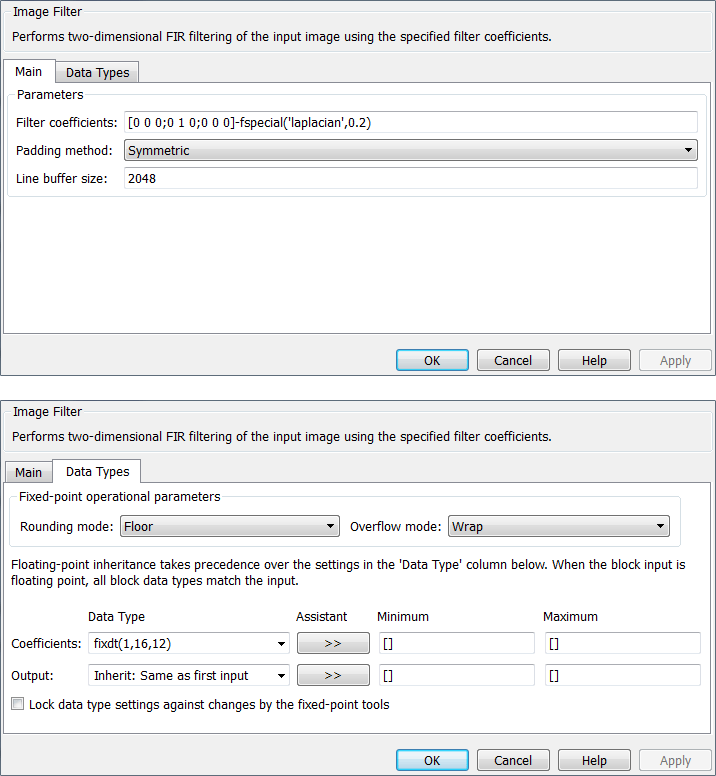

在此示例中,该设计包含一个系统对象Visionhdl.imageFilter..它是对hdl友好的Imfilter.功能。配置与相同的系数和填充方法相同Imfilter..

功能[PIXOUT,CTRLOUT] = ImagesHarpeningHDLDesign(PIXIN,CTRLIN)使用像素流实现算法Vision HDL工具箱%系统对象%版权所有2015 Mathworks,Inc。% # codegen持续的锐化熏肉;如果isempty(sharpingfilter)sharpcoeff = [0 0 0; 0 1 0; 0 0 0] -fspecial(的拉普拉斯算子,0.2);SharpingFilter = Visionhdl.imageFilter(...“系数”sharpCoeff,...'paddingmethod','对称',...“CoefficientsDataType”,'风俗',...“CustomCoefficientsDataType”12) numerictype(16日);结尾[PIXOUT,CTRLOUT] =步骤(SHARPONINGFILTER,PIXIN,CTRLIN);

第2步:创建测试台文件

测试台ImageSharpeningHDLTestBench.m在模糊的图像中读取。的frm2pix对象将完整图像帧转换为像素流和控制结构。测试台呼叫设计功能ImageSharpeningHDLDesign一次处理一个像素。处理整个像素流后,PIX2FRM.将输出像素流转换为全帧图像。测试台将输出图像与参考输出进行比较imgSharp.

...[pixInVec, ctrlInVec] = (frm2pix imgBlur)步;为了p = 1:numpixperfrm [pixoutvec(p),ctrloutvec(p)] = imagesharpeninghdldesign(pixinvec(p),ctrlinvec(p));结尾imgout = step(pix2frm,pixoutvec,ctrloutvec);

%比较结果imgdiff = imabsdiff(imgsharp,imgout);流(“相应像素之间的最大差异为%d。\ n'马克斯(imgDiff (:)));流('总%D像素是不同的。\ n',nnz(imgdiff));...

第3步:模拟设计和验证结果

在HDL代码生成之前使用测试台模拟设计,以确保没有运行时错误。

Imagesharpeninghdltestbench.

相应像素之间的最大差异为1.总共4124个像素是不同的。模拟花了107.544594秒完成。

实验台显示了对比结果和仿真时间。由于量化误差和舍入误差,在总共256*256=65536像素中,imgOut的38554个像素与imgSharp.然而,强度的最大差值是1。在0到255的范围内,这种差异在视觉上是不明显的。

如我们所能看到的,通过将Matlab的模拟时间与行为模型的比较,像素流协议引入了大量的开销。您可以使用Matlab Coder™加快MATLAB中的像素流仿真。看使用MATLAB编码器加速像素流设计(Vision HDL工具箱).

第4步:生成HDL代码

满足FPGA目标模型的结果,您可以使用HDL编码器从设计中生成HDL代码。您可以在HDL模拟器中运行生成的HDL代码,或将其加载到FPGA中并在物理系统中运行它。

确保设计和测试台文件位于相同的可写目录中。要生成HDL代码,使用以下命令:

hdlcfg = coder.config ('hdl');hdlcfg.testbenchname =.'appressharpeninghdltestbench';hdlcfg.targetlanguage ='Verilog';hdlcfg。GenerateHDLTestBench = false;codegen配置hdlcfgImageSharpeningHDLDesign

有关如何创建和配置MATLAB到HDL项目的更多细节,请参阅HDL编码器文档中的“入门MATLAB到HDL工作流”教程。

从Simulink生成HDL代码金宝app

步骤1:创建优化的hdl模型

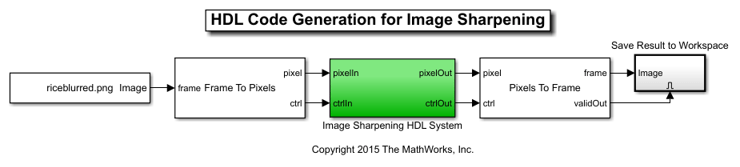

的Imagesharpeninghdlmodel.模型如下所示。

modelname =“ImageSharpeningHDLModel”;open_system (modelname);set_param (modelname“开放”,'在');

模型在模糊图像中读取。帧到像素块将全帧图像转换为像素流,并且对帧块的像素将像素流转换回全帧图像。图像锐化HDL系统包含图像过滤器块,它是Vision HDL工具箱中的HDL友好的对应物Imfilter.在行为模型中呈现的功能。

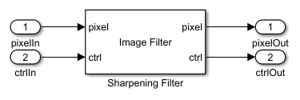

set_param (modelname“开放”,'离开');set_param([modelname'/图像锐化HDL系统'],“开放”,'在');

使用与行为模型相同的锐化系数和填充方法配置图像过滤器块,如下面的掩码所示。

第2步:模拟设计和验证结果

抽搐sim (modelname);toc

运行时间为32.122551秒。

金宝appSimulink利用C代码生成来加速仿真。因此,它比MATLAB仿真快得多,尽管仍然比行为模型慢。

模拟在工作区中创建一个名为imgout的新变量。使用以下命令进行比较ingout.和imSharp由行为模型生成。

imgdiff = imabsdiff(imgsharp,imgout);流(“相应像素之间的最大差异为%d。\ n'马克斯(imgDiff (:)));流('总%D像素是不同的。\ n',nnz(imgdiff));

相应像素之间的最大差异为1.总共4124个像素是不同的。

由于量化误差和舍入误差,总共256 * 256 = 65536像素,38554ingout.不同于imgSharp.然而,强度的最大差值是1。在0到255的范围内,这种差异在视觉上是不明显的。(这与“从MATLAB生成HDL代码”一节的步骤3中给出的解释相同。)

第3步:生成HDL代码

满足FPGA目标模型的结果,您可以使用HDL编码器从设计中生成HDL代码。您可以在HDL模拟器中运行生成的HDL代码,或将其加载到FPGA中并在物理系统中运行它。

使用下面的命令从图像锐化HDL系统生成HDL代码:

makehdl ('AmotionHeningHDLModel /图像锐化HDL系统')

set_param([modelname'/图像锐化HDL系统'],“开放”,'离开');close_system(modelname,0);关闭全部;