PLL输出的相位噪声

该示例说明了如何预测锁相环(PLL)输出处的相位噪声,使用PLL测试窗模拟PLL,并将模拟结果与理论预测进行比较。

此示例演示了三相噪波效果(单独或组合),具体取决于您选择的配置:

参考调制或相位噪声

VCO相位噪声

反馈预分频器对VCO相位噪声进行二次采样

打开模型PllPhaseNoiseExample.slx。

开放式系统(“PllPhaseNoiseExample.slx”);

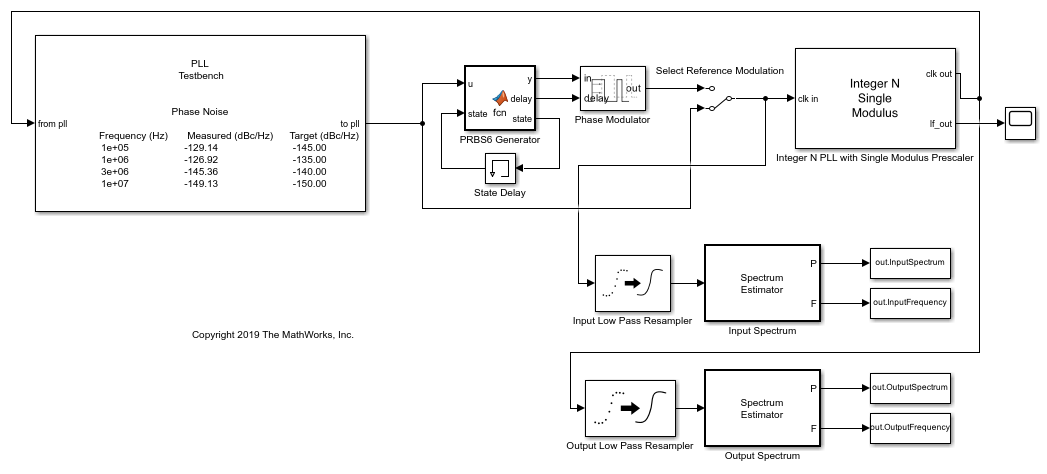

这个例子使用了整数N锁相环单模预分频器来自混合信号块集™。

PLL测试台生成PLL的参考输入信号,并测量PLL输出处的相位谱密度。

该模型中的可选PRBS6参考相位调制用于对比参考相位变化响应与VCO相位噪声响应。

输入到频谱估计器的低通重采样器是抗锯齿滤波器。这些滤波器将变量步长信号转换为频谱估计器所需的固定步骤离散信号。

PLL输入和输出信号的频谱被估计并记录在基本工作空间中,以便您可以将仿真结果与理论计算结果进行比较。

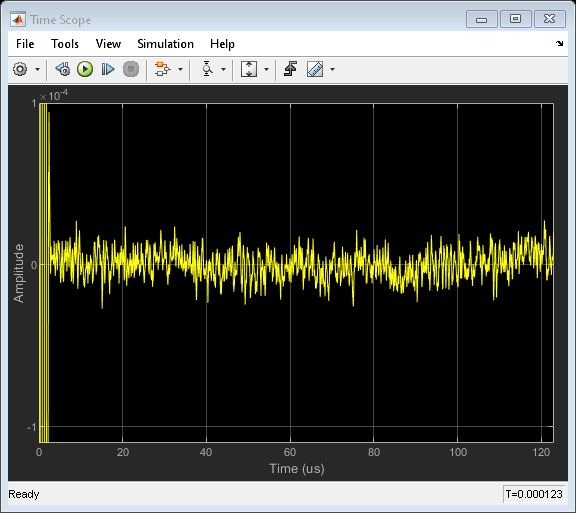

示例模型中的示波器提供了模拟的进度指示符。

要评估PLL在各种条件下的行为,请为每一组不同的条件使用单独的工作区文件。此示例提供了五个这样的支持.mat文件。所有这些文件都产生相同的环路瞬态响应。金宝app

基线.垫-尽可能接近理想。用于评价模型和模拟器引入的数值噪声。ReferenceModulation.mat- 引入参考相位调制。用于评估PLL的相位传递函数。vcophasenoise.mat-引入VCO相位噪声和预分频比等于1。用于评估锁相环控制回路的误差功能。带内相位噪声- 引入VCO相位噪声和大于1的预分频器比例。用于评估预分频器比对PLL控制回路的误差功能的影响。TotalPhaseNoise.mat-所有相位噪声源均已启用,且预分频器比率大于1。

理论计算

本节将演示如何计算锁相环的期望响应。

PLL的目标环路带宽是2 MHz,具有45度相位余量。环路滤波器组件缩放到实际水平,电荷泵输出电流由相同的因素缩放以保持相同的循环动态。

功能getPllLoopResponse计算环路增益作为频率的函数,然后计算从锁相环外部或内部信号的预期响应。定义输入参数,如电荷泵输出电流,VCO灵敏度,预分压器比和无源环路滤波器的分量值getPllLoopResponse函数使用。

PllKphi = 5 e - 3;%电荷泵输出电流pllkvco = 100e6;% VCO的敏感性PllN = 70;%预分频器比率PLLR2 = 1.33E3;%二阶响应回路滤波器电阻(欧姆)PllR3=1.7e4;用于三阶响应的%环形滤波器电阻(欧姆)PllR4 = 0;%四阶响应回路滤波器电阻(欧姆)PllC1 = 1.31 e-11;%环路滤波器直接电容(F)PllC2 = 1.44平台以及;%二阶响应环路滤波器电容(F)PLLC3 = 9.41E-13;三阶响应环路滤波器电容(F)PllC4 = 0;第四阶响应的%环路滤波器电容(f)

这个脚本prepareexpectedspectra计算参考相位调制和VCO输出相位噪声的谱密度。脚本还将结果与锁相环响应相结合,以获得在锁相环输出的相位噪声谱密度。参考相位调制是一个确定的过程,频谱分量的振幅表示为载波振幅(dBc)的一个分数。相比之下,VCO相位噪声是一个随机过程,其谱密度以dBc/Hz表示。

定义的输入参数prepareexpectedspectra脚本,例如参考输入频率、PRBS6相位调制数据模式的每个符号的参考周期数、PRBS6参考相位调制的单个光谱分量的振幅、用相位噪声评估光谱的分辨率带宽、频率偏移矢量、,和指定频率偏移处的相位噪声谱密度。

PllAddPhaseNoise=“上”;%启用VCO相位噪声PLLFOFFSET = [30E3 100E3 1E6 3E6 10E6];%VCO偏移频率(Hz)PllPhaseNoise = [-56 -106 -132 -143 -152];%VCO输出相位噪声(dBc/Hz)cfgselectrefmod ='0';%启用参考相位噪声调制CfgRef = 30 e6;%参考频率cfgcyclespersymbol = 2;每PRBS6调制符号%参考周期CfgModLevel = -110;%基准相位调制电平(dBc/Hz)cfgresbandwidth = 100e3;%PLL测试台分辨率带宽CfgTargetSpectrum = [100e3 -145;1e6 -135;3e6 -140;%PLL Testbench目标相位噪声(DBC / Hz)

如果变量工作空间文件存在并指向可以加载的文件,将该文件加载到工作区中。要使用此示例提供的配置,请设置值工作空间文件到该配置的文件的名称。

如果存在('workspacefile'那“var”)&&exist(工作空间文件,'文件')负载(工作空间文件);结束

用软件分析锁相环控制回路getPllLoopResponse功能。此功能的输出是:

环路频率-计算预期响应的频率点。LoopZofs- 作为频率的函数的环路滤波器的传输阻抗。LoopGofs- 从预分频器的输出到VCO输入的环路增益,包括VCO电压灵敏度。请注意,预分频器比例不包括在此输出中,但包含在闭环传输功能中。浮胶- 从PLL参考输入到PLL输出的闭环相位传递函数。LoopEofs-关于VCO输出的闭环相位误差传递函数。

[LoopFrequency,Loopzofs,Loopgofs,Loophofs,Loopeofs,Loopphstep] =......getPllLoopResponse ([0 PllR2 PllR3 PllR4], [PllC1、PllC2 PllC3, PllC4),......PllKphi、PllKvco、PllN);

组织期望谱密度的计算,将谱分量直接放入频率箱中。

期望光谱密度的工作空间变量为:

输出频率-计算期望输入频谱的频率向量(Hz)。输出频谱-在PLL的参考输入(dBm到一个1欧姆负载的分辨率带宽的期望频谱值的向量CfgResBandwidth)。expRuitptrequency-计算期望输出频谱的频率向量(Hz)。expReptpectrum.-将PLL输出(dBm)处的预期频谱值矢量转换为分辨率带宽为1欧姆的负载CfgResBandwidth)。

prepareExpectedSpectra;

研究预期结果

在本节中,检查预期的PLL行为。

从锁相环的闭环响应开始,考虑三个基本响应:瞬态响应、传递函数和误差函数。

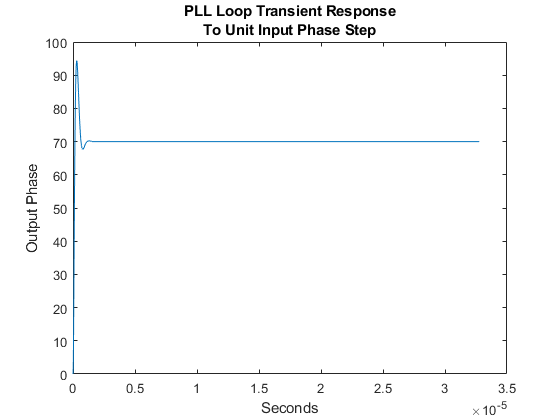

瞬态反应

在大多数PLL应用中,环路初始获取锁相时,环路瞬态响应最为重要。对于非常小的初始频率偏移或相对较高的闭环带宽,瞬态响应可以合理准确地预测环路获取时间。然而,在许多情况下,环路瞬态响应仅代表在频率采集完成后,在相位采集期间重新显示响应。本示例仅说明相位采集时间。

绘制锁相环的瞬态响应。

图(1);情节(LoopPhStep.Time LoopPhStep.Data);标题({“PLL环路瞬态响应”;“至单元输入相位步进”});Xlabel('秒');ylabel(“输出阶段”);

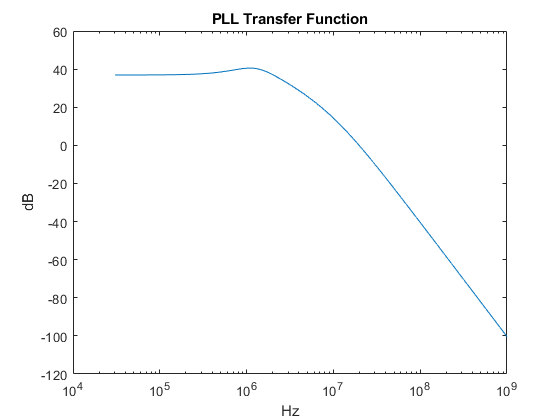

传递函数

当期望PLL非常精确地跟踪调制输入或期望它从噪声输入中滤除噪声时,从参考输入到PLL输出的传递函数可能很重要。

创建锁相环传递函数的对数-对数图。

图(2);半对数x(循环频率,20*log10(abs(循环频率));标题(锁相环传递函数的);Xlabel(“赫兹”);ylabel('D b');

误差函数

PLL控制回路预计将拒绝在PLL本身内产生的相位噪声,例如VCO相位噪声。VCO相位噪声和PLL输出之间的传递函数有时称为环路错误功能。检查此传输功能有助于在将循环错误应用于另一个噪声源之前进行补偿。

创建锁相环错误函数的日志-日志图。

图(3);semilogx(Loopfrequency,20 * log10(ABS(LOOPEOFS)));标题('PLL循环错误功能');Xlabel(“赫兹”);ylabel('D b');

在锁相环输出处绘制总期望相位噪声。

图(4);绘图(expRutputfrequency,expRutpectrum);标题(锁相环输出光谱的);Xlabel(“赫兹”);ylabel('dbm成1欧姆');xlim ([PllN * CfgRef-2 * PllFoffset(结束),PllN * CfgRef + 2 * PllFoffset(结束)]);

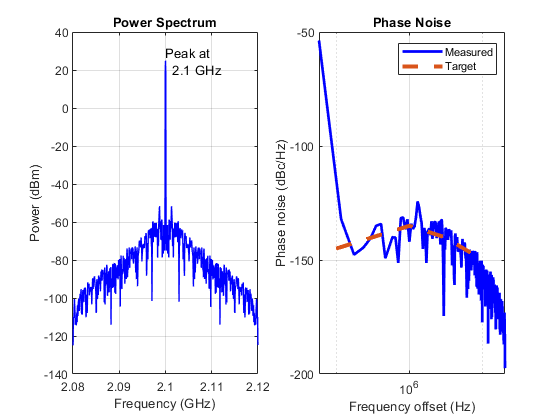

这phaseNoiseMeasurefunction是PLL Testbench使用的回调函数。它显示目标输出相位噪声谱密度以及模拟的或预期的相位噪声谱密度。

要将预期输出相位噪波与特定设计目标进行比较,请定义工作空间变量目标光谱。目标光谱由两个列数阵列组成,可在PLL的输出端指定目标相位噪声。第一个列指定Hz中的频率偏移,第二列指定如果DBC / Hz,则指定相应的相位噪声谱密度。PLL TestBench使用回调函数phaseNoiseMeasure显示预期和模拟的相位噪声谱密度。

查看以dBc/Hz为单位的预期PLL输出相位噪声。

(~) = phaseNoiseMeasure (ExpOutputFrequency ExpOutputSpectrum,......CfgResBandwidth,CfgTargetSpectrum(:,1)。”,“上”那“5”那......CfgTargetSpectrum(:,2)。”;

如果环路响应不令人满意,您可以查看更详细的结果,如环路滤波器跨越阻抗(LoopZofs)获得额外的见解,可以帮助您提高PLL设计。

运行模拟

虽然配置过程很简单,但有许多参数需要配置configureexamplepll.脚本配置PLL Simulink®模型,然后执行模型。金宝app

configureexamplepll;simout = sim(“PllPhaseNoiseExample”);

为了简化打印,请将结果转换为以下四个工作空间变量:

SimInputFrequency—存储模拟的输入频谱的频率向量(Hz)。相似谱- 在PLL的参考输入处的光谱值向量(DBM进入一个欧姆负载的分辨率带宽CfgResBandwidth)。SimOutputFrequency- 计算模拟的输出频谱的频率向量(Hz)。SimOutputSpectrum-PLL输出(dBm)处的模拟频谱值矢量,以1欧姆的分辨率带宽转换为1欧姆的负载CfgResBandwidth)。

使结果更容易从工作区绘制。

SimInputFrequency =重塑(SimOut.InputFrequency.Data(:,结束),1,[]);SimInputSpectrum =重塑(SimOut.InputSpectrum.Data(:,结束),1,[]);SimOutputFrequency =重塑(SimOut.OutputFrequency.Data(:,结束),1,[]);SimOutputSpectrum =重塑(SimOut.OutputSpectrum.Data(:,结束),1,[]);

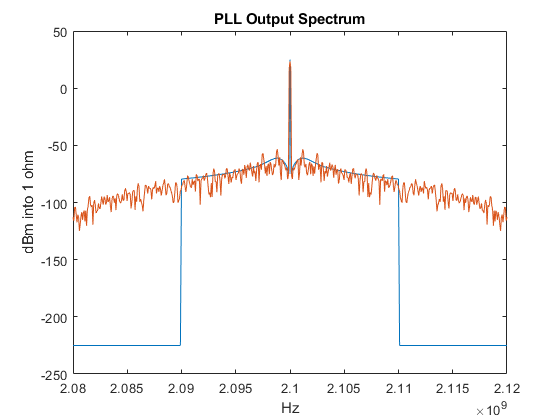

比较预期结果和模拟结果

比较锁相环输出的预期和模拟相位噪声。

图(4);绘图(expRutputfrequency,expRutpectrum);标题(锁相环输出光谱的);Xlabel(“赫兹”);ylabel('dbm成1欧姆');xlim([PllN*CfgRef-2*PllFoffset(结束),PllN*CfgRef+2*PllFoffset(结束)];保持在…上;情节(SimOutputFrequency SimOutputSpectrum);持有关;

查看以dBc/Hz为单位的预期PLL输出相位噪声。

(~) = phaseNoiseMeasure (SimOutputFrequency SimOutputSpectrum,......Simoutputprequency(2)-SimOutputFrequency(1),......CfgTargetSpectrum(:,1)。”,“上”那“5”CfgTargetSpectrum(: 2)。');

保存配置和结果

保存整个工作空间,包括当前状态的系统配置和结果,到文件。如果是工作空间文件变量已经存在,则可以将当前状态保存到该文件。若要保存到新文件,请更改工作空间文件。

如果存在('workspacefile'那“var”)保存(Workspacefile);结束

另请参阅

整数N锁相环单模预分频器|PLL Testbench.|可变脉冲延迟