Half-Bridge Driver

Behavioral model of half-bridge driver integrated circuit

- Library:

Simscape / Electrical / Semiconductors & Converters

Description

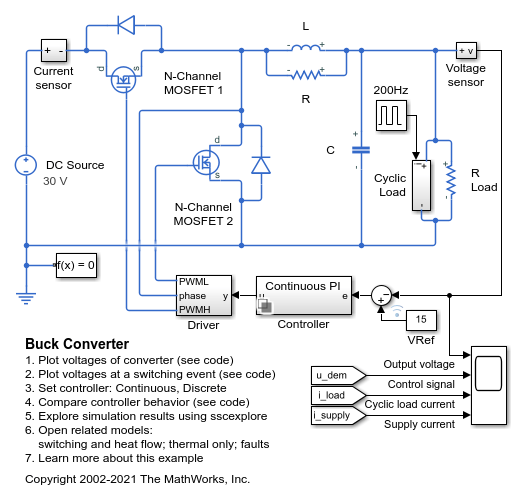

TheHalf-Bridge Driverblock provides an abstracted representation of an integrated circuit for driving MOSFET and IGBT half-bridges. The block models input hysteresis, propagation delay, and turn-on/turn-off dynamics. Unless modeling a gate driver circuit explicitly, always use this block or theGate Driverblock to set gate-source voltage on a MOSFET block or gate-emitter voltage on an IGBT block. Do not connect a controlled voltage source directly to a semiconductor gate, because this omits the gate driver output impedance that determines switching dynamics.

You can model electrical or physical signal input ports by setting theModeling optionparameter to either:

PS input— The driver output state is controlled by a physical signal input u. Use this modeling option if all of your controller, including PWM waveform generation, is determined by Simulink®blocks. This modeling option is the default.Electrical input ports— The driver output state is controlled by two electrical input connections, PWM and REF. Use this option if your model has upstream analog components, such as theControlled PWM Voltagesource.

The first pair of output electrical ports, HO and HS, behave in the same way as the G and S ports of theGate Driverblock. Connect these ports to the high-side MOSFET or IGBT of the half-bridge. The second pair of ports, LO and LS, connect to the low-side MOSFET or IGBT of the half-bridge. They behave in a similar way, except that their logic is inverted with respect to that of the high side.

The diagram shows the timing properties for the half-bridge driver, where:

tpLHis low-side propagation delay when the input logic goes from 0 to 1.

tdLHis high-side dead time when the input logic goes from 0 to 1.

tpHLis high-side propagation delay when the input logic goes from 1 to 0.

tdHLis low-side dead time when the input logic goes from 1 to 0.

Faults

You can insert a fault into one or both of the outputs at a specified simulation time. The fault options are:

失败在lo输入固定gic 0

不能输入固定的逻辑1

Fail high side off

Fail high side on

Fail low side off

Fail low side on

Fail high and low sides off

Fail high and low sides on