主要内容

并行链接设计

设计并行链路,如DDR

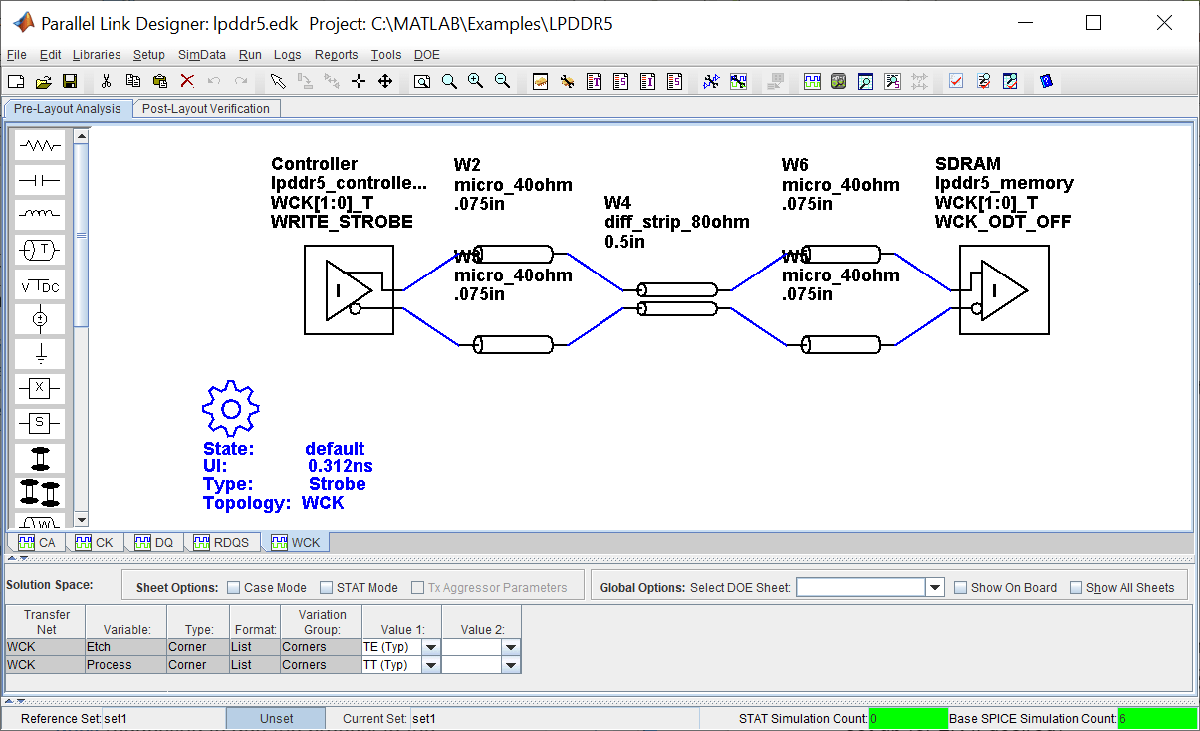

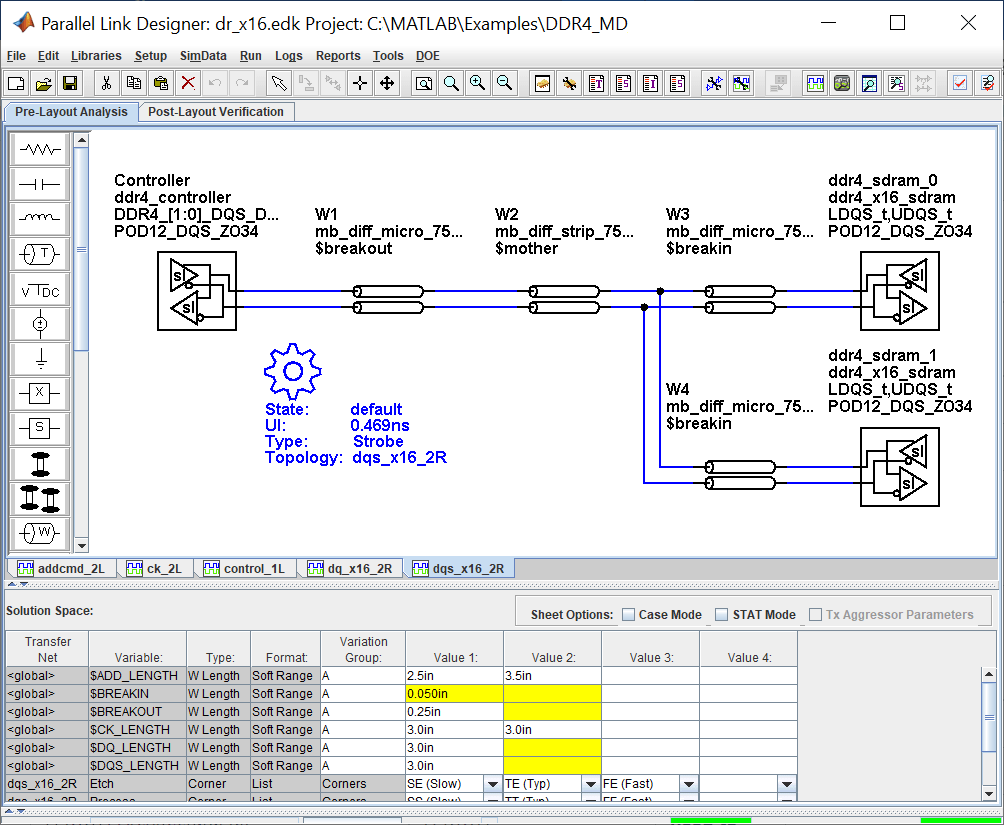

的并行链接设计师App为并行链接提供了一个专用的系统级设计和分析环境。捕捉你的平行链接设计图形和实验不同的物理布局和参数扫描,以确定设置/保持时间和电压的高速平行链接。分析并行接口是否符合时序和信号完整性约束。

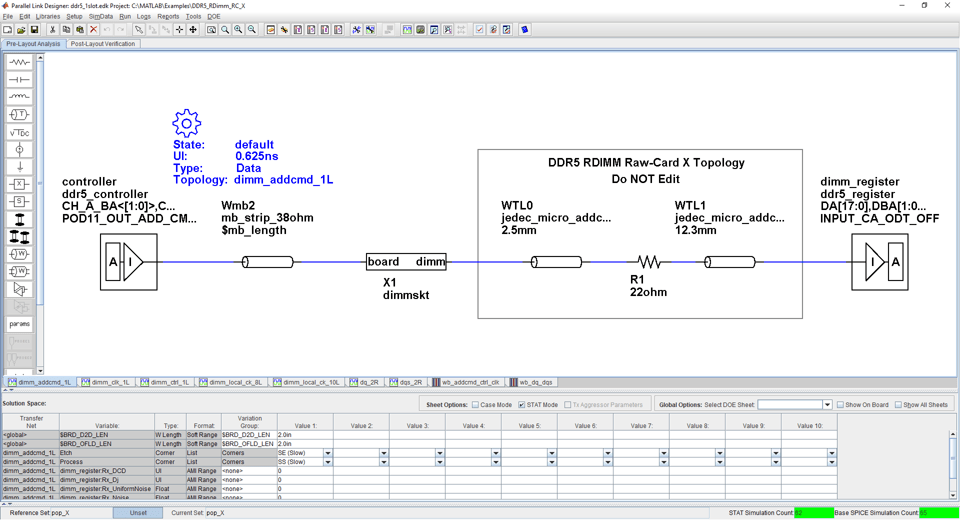

使用并行链接设计师应用程序配置并行链接。设置模拟参数,指定拐角条件,定义刺激模式。设置预布局分析以运行SPICE,并进行波形和时序数据分析以分析自定义并行链接。视图和解释结果使用信号完整性的观众如果您有RF PCB Toolbox™的许可证,您也可以设置和分析并行链路设计的后布局PCB数据库。您可以修改堆栈和面板堆栈模型,并自定义通道,并查看更改如何影响您的设计。

主题

并行链接项目

设置参数控制SPICE仿真和统计,时域,波形分析。

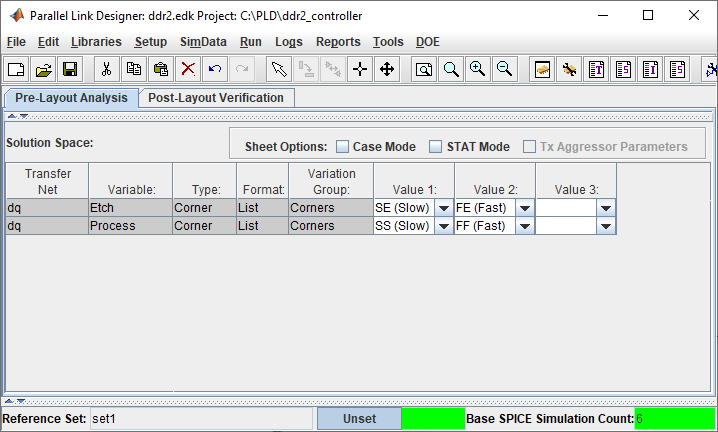

指定要在并行链接项目中模拟的过程角和刻蚀角。

定义并行链路项目时域分析的刺激模式。

增加TX时钟抖动,RX时钟抖动,RX时钟恢复抖动和噪声。

Pre-Layout分析

学习预布局分析的基础知识。

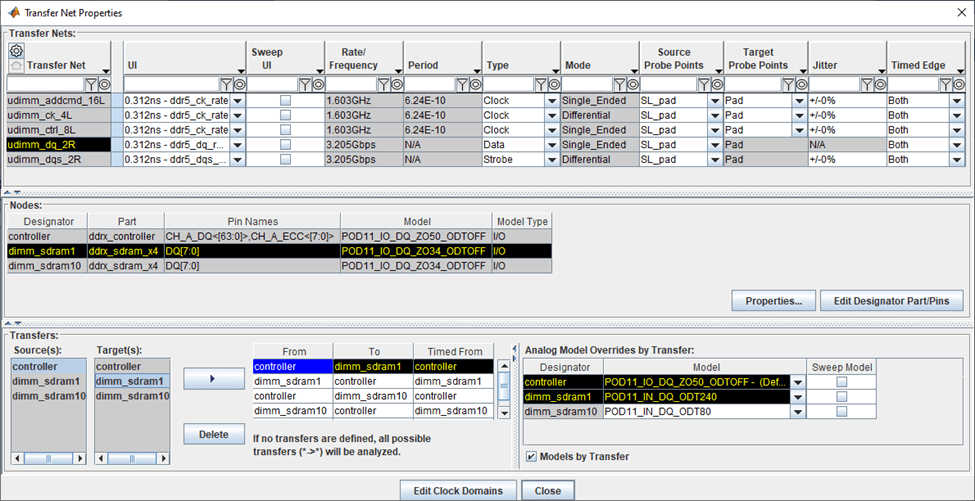

编辑传输线模型、指示器、s -参数和IBIS文件来定制预布局分析。

查看、解释和调试预布局分析结果。

通过使用parallel Computing Toolbox™并行运行模拟,减少运行完整模拟集所需的时间。

布线后的验证(需要射频PCB工具箱)

验证系统级集成电路和PCB设计数据库的时间裕度。

编辑堆栈和控制面板模型。

使用Stackup编辑器和PadStack编辑器管理通道和堆栈。