主要内容

中断通道

从硬件发送中断到处理器

- 库:

SoC块集/内存

描述

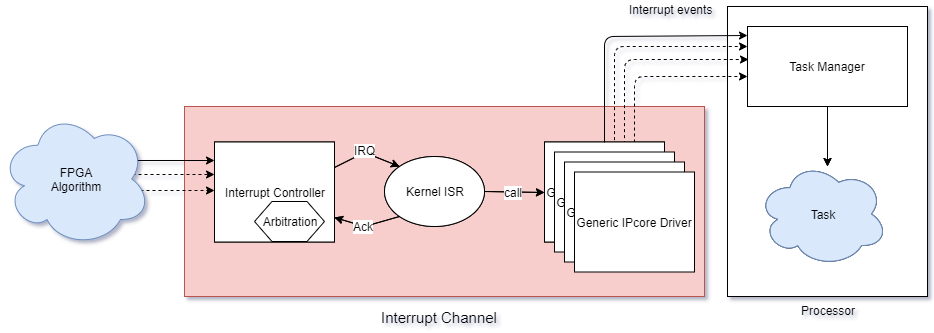

的中断通道模块接收来自FPGA逻辑的中断请求内存通道块,仲裁请求,并触发事件驱动的软件任务到任务管理器块。最多可以连接16个设备到中断控制器,每个设备有一个中断。该区块由以下三个部分组成:

中断控制器——这个部分接受中断请求(irq),并根据用户指定的优先级对它们进行仲裁。当对中断控制器的并发请求存在时,优先级高的请求会在优先级低的请求之前处理。

内核中断服务程序(ISR)——该部分从中断控制器接收中断请求,处理中断,并向中断控制器发送确认信号,以便它可以处理下一个IRQ。

IPCore Driver(每个中断一个)——这个部分接收来自内核ISR的请求,并在处理器中触发一个事件驱动的任务。

尽管中断通道可以有多个对处理器的中断输出,但它在任何给定时间向处理器发送的活动中断事件都不超过一个。

这幅图显示了一个概念性的视图中断通道块,它接受来自FPGA算法的中断请求。在仲裁之后,内核为请求提供服务,并向处理器算法触发事件。

港口

输入

输出

参数

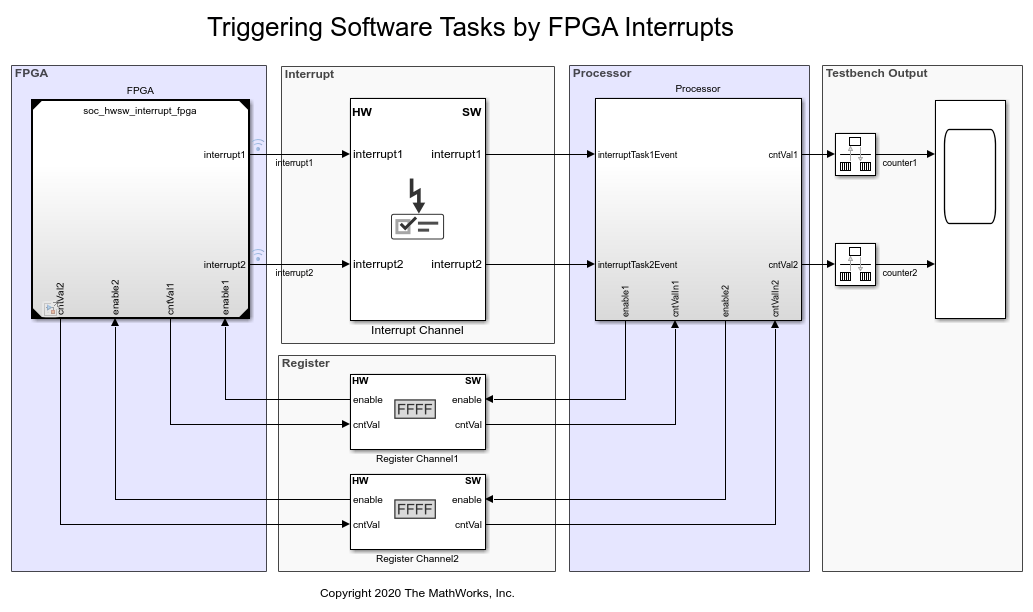

模型的例子

扩展功能

在R2020b中引入