访问DUT寄存器英特尔纯FPGA板使用IP核生成工作流

这个例子展示了如何使用HDL编码器™IP核心代工作流为英特尔®开发参考设计部分不使用嵌入式ARM®处理器出席,但仍然利用高密度脂蛋白编码器生成AXI接口控制设计测试(DUT)。下面的例子使用了高密度脂蛋白校验™AXI经理IP访问HDL编码器生成从MATLAB®DUT寄存器。或者,您可以使用英特尔转换频率JTAG阿瓦隆®主桥FPGA IP访问寄存器使用Tcl命令转换频率系统控制台。对于英特尔JTAG AXI大师,您必须创建一个自定义的参考设计。箭头上的FPGA设计实现®十马克斯®10 FPGA评估工具。

需求

第四的英特尔®'标准,支持版本中列出金宝appHDL语言支持,支持第三方金宝app工具和硬件

箭十马克斯10 FPGA评估工具

高密度脂蛋白编码器支金宝app持英特尔FPGA板包

高密度脂蛋白校验支持英特尔金宝appFPGA板包

高密度脂蛋白编码器为金宝app英特尔SoC设备支持包(只需要当你想将IP核心集成到您自己的自定义参考设计)

箭十马克斯10 FPGA评估工具

这图显示了箭十马克斯10 FPGA评估工具。

例子参考设计

设计,可以受益于使用HDL编码器IP核生成工作流不使用嵌入式ARM处理器或嵌入式编码器™支持包但仍利用高密度脂蛋白编码器生成AXI4寄存器可以包括一个IP组。金宝app

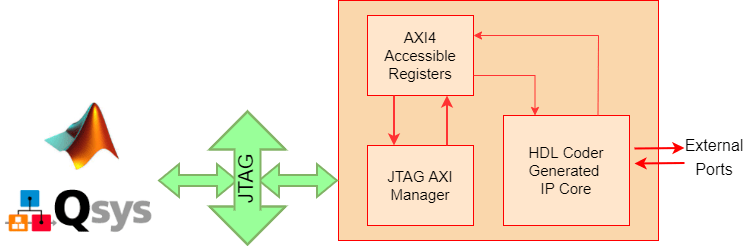

+高密度脂蛋白HDL校验AXI经理编码器IP核心

JTAG主控+高密度脂蛋白编码器IP核心

nio®II +高密度脂蛋白编码器IP核心

作为PCIe®端点+高密度脂蛋白编码器IP核心

这个例子包含两个参考设计。

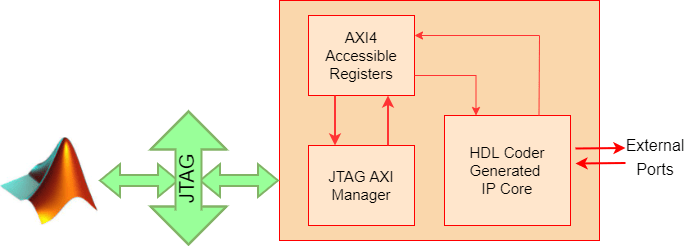

默认系统参考设计使用MathWorks IP和MATLAB®发出读写命令的命令行接口。使用这个设计,你必须有高密度脂蛋白验证器产品。

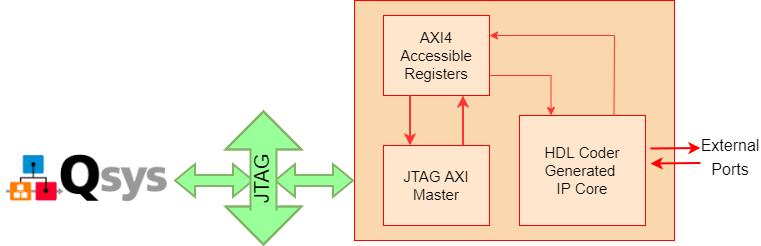

英特尔JTAG AXI主参考设计使用第四的IP JTAG AXI主,需要使用第四的Tcl控制台发出读写命令。

这两个参考设计相差只有JTAG经理他们使用的IP。

高密度脂蛋白校验AXI经理参考设计

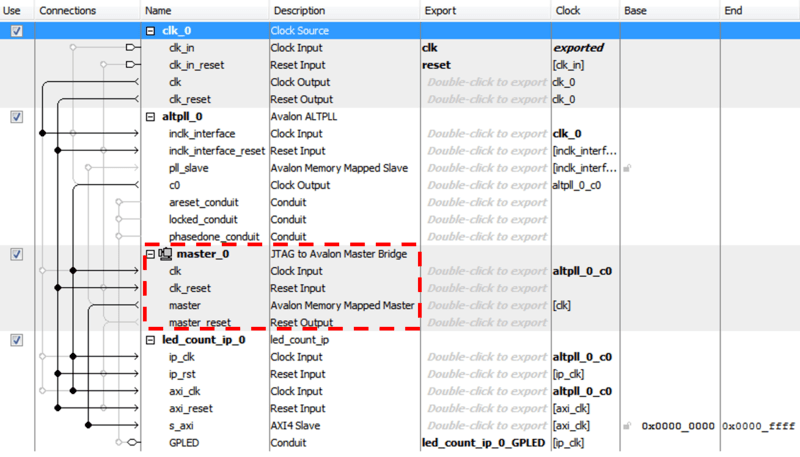

IP核代工作流的HDL工作流顾问设置目标参考设计一步,使需要插入AXI经理(HDL校验)参数。这个选项将AXI经理IP自动添加到参考设计和连接IP添加到DUT IP使用AXI4-slave接口。在下一节中详细的步骤自动JTAG AXI经理IP参考设计。

执行IP核心工作流

按照以下步骤执行IP核心工作流系统默认的参考设计,它使用JTAG AXI经理IP。使用此参考设计,您可以生成一个高密度脂蛋白IP核心闪烁led十董事会。生成HDL IP核心,遵循这些步骤。

1。建立了英特尔第四的®工具路径。使用自己的英特尔第四的安装路径通过执行这个命令在MATLAB。

hdlsetuptoolpath (“ToolName”,“阿尔特拉第四的二世”,…“路径”,“C: \ intelFPGA \ 20.1 \第四的\ bin64 \ quartus.exe);

2。打开模型模型,在M金宝appATLAB环境下实现LED闪烁通过执行这个命令。

open_system (“hdlcoder_led_blinking”)

3所示。发射HDL工作流的顾问hdlcoder_led_blinking / led_counter子系统通过右击led_counter子系统和选择HDL代码紧随其后的是高密度脂蛋白工作流顾问。

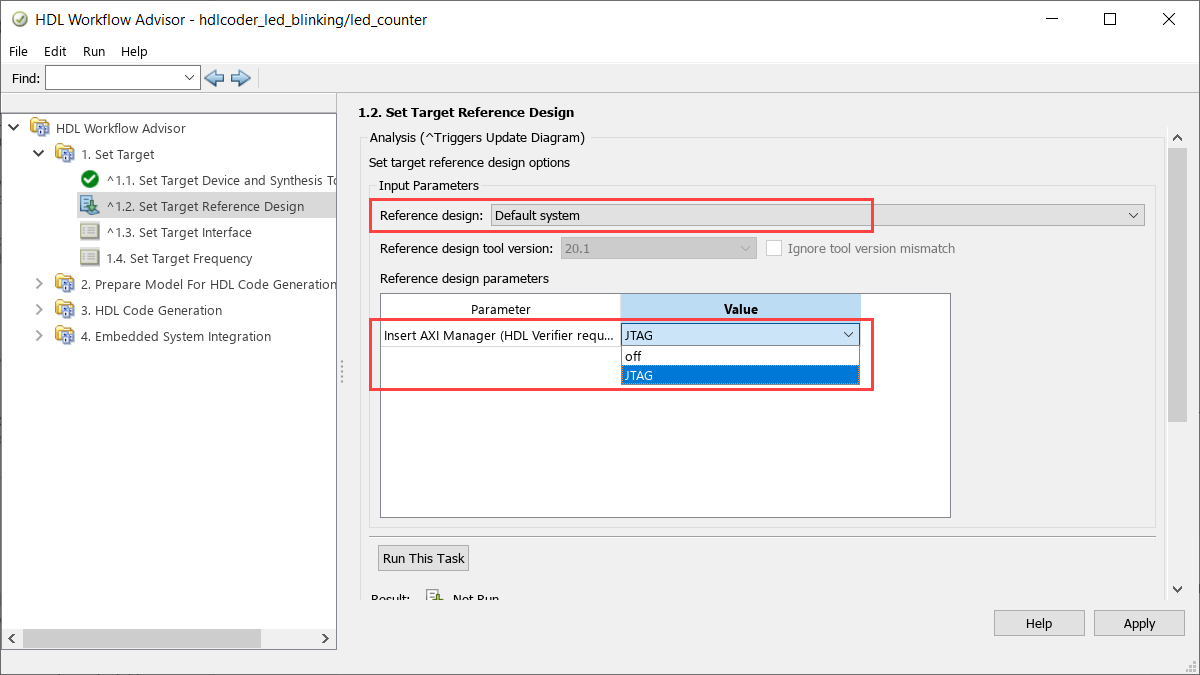

4所示。在步骤1.1中,集目标工作流程来IP核心代和目标平台来箭十马克斯10 FPGA评估工具。点击运行这个任务。

5。在步骤1.2中,集参考设计来默认的系统。下参考设计参数,设置需要插入AXI经理(HDL校验)来JTAG。

6。在步骤1.3中,设置的接口Blink_frequency,Blink_direction,Read_back港口AXI4。设置的接口领导港口led通用[0:7]。

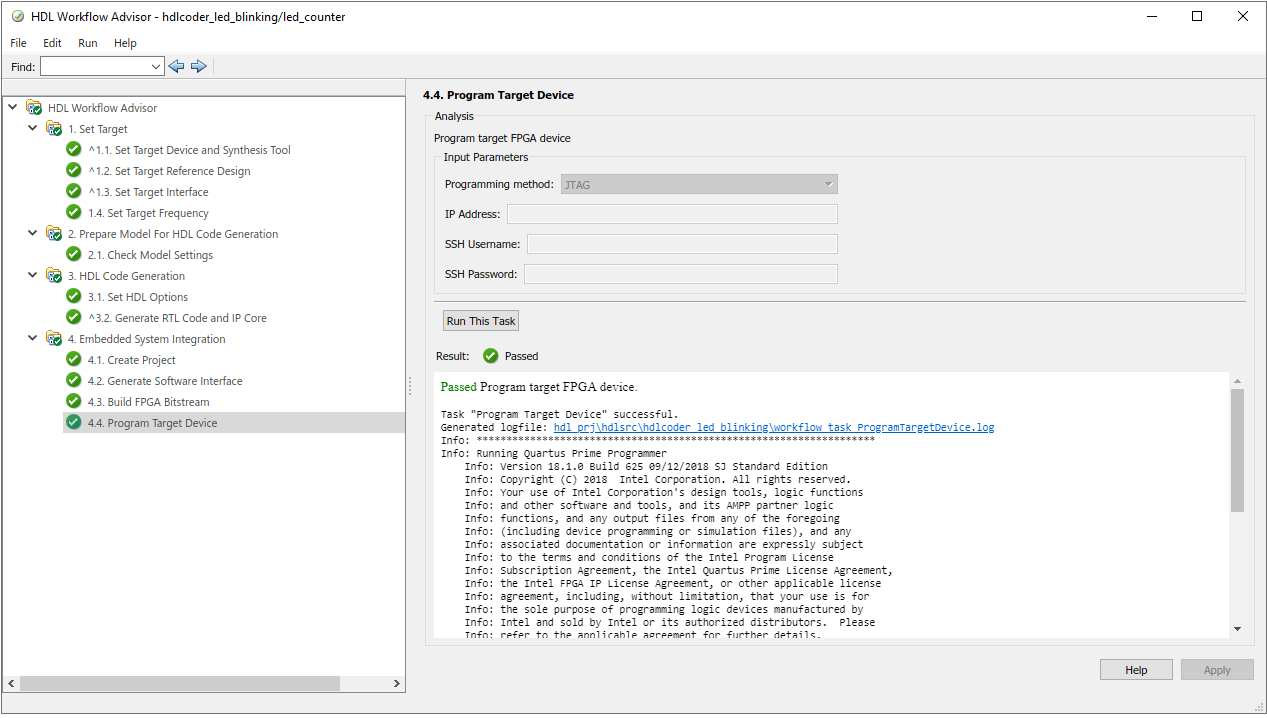

7所示。在工作流运行剩下的步骤生成一个比特流和项目目标设备。

确定地址从IP核心报告

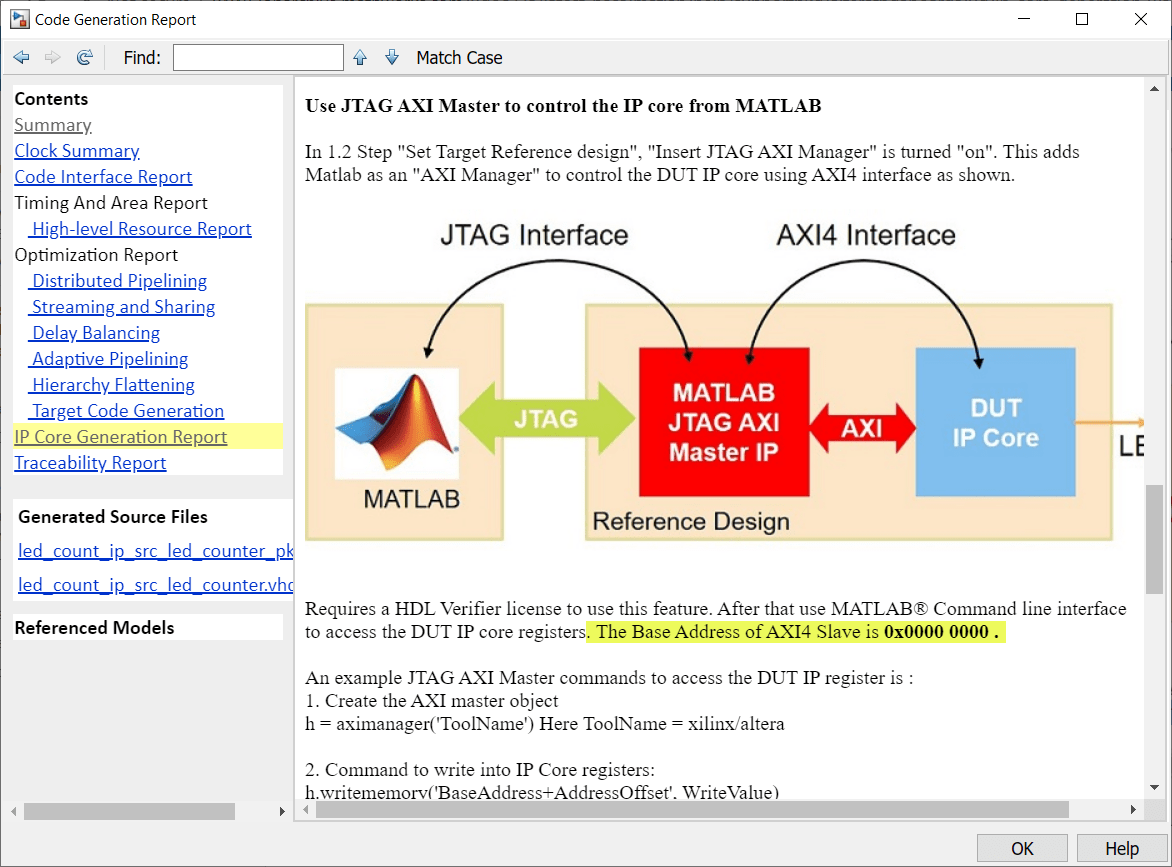

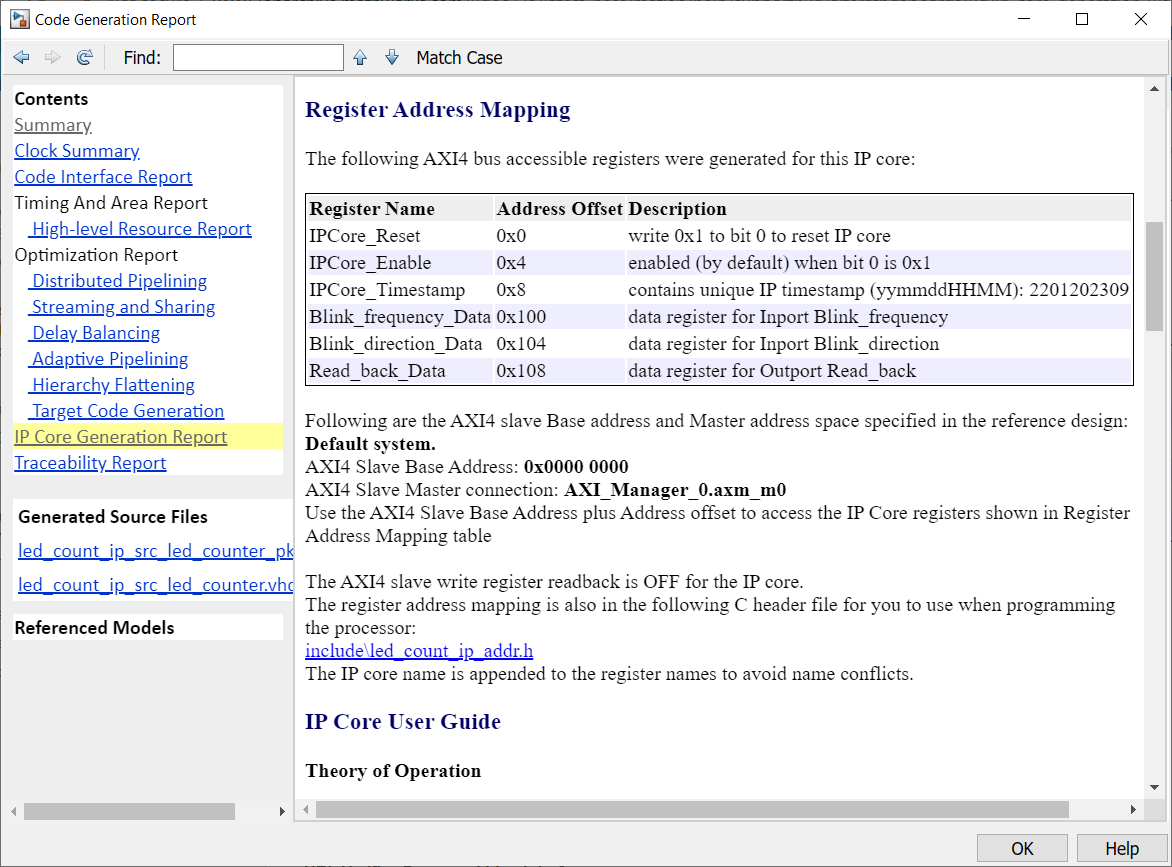

高密度脂蛋白的基地址编码器IP核心定义为0 x00000000系统默认的参考设计,它使用AXI经理IP。你可以看到地址设置在生成的IP核心报告此图所示。

IP核心报告寄存器地址映射表显示了补偿。

高密度脂蛋白验证器命令行界面

如果你有HDL校验支持英特尔FPGA板包并选择AXI经理参金宝app考设计,然后你可以使用MATLAB命令行接口来访问的IP核产生的高密度脂蛋白编码器产品。

从DDR内存读写,遵循这些步骤。

1。创建一个AXI管理器对象。

h = aximanager (“阿尔特拉”)

2。问题写命令。例如,禁用DUT。

h.writememory (“4”,0)

3所示。启用DUT。

h.writememory (“4”,1)

4所示。读当前的计数器值。

h.readmemory (“108”,1)

5。删除对象释放JTAG资源。如果你不删除对象,其他JTAG操作,如编程FPGA,失败。

删除(h)

英特尔JTAG AXI主参考设计

创建一个自定义参考设计使用英特尔JTAG AXI主IP参考设计,然后添加参考设计文件使用MATLAB路径目录命令。

访问HDL编码器IP核心寄存器使用英特尔JTAG AXI主IP使用基础参考设计插件文件中定义的地址。

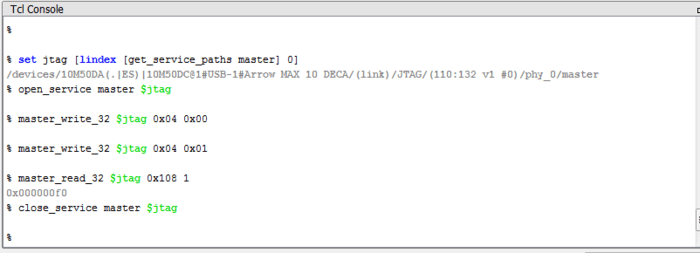

转换频率系统控制台Tcl命令阿喜读和写

之前打开系统控制台,选择适当的转换频率读写命令。对于这个示例,因为所有的HDL编码器生成IP核心寄存器目前32位,使用这些读写命令。

% master_write_32 < service-path > <起始地址> < list-of-32-bit-values > % master_read_32 < service-path > <起始地址> < size-in-multiples-of-32-bits >

例如,写32位十六进制值0 x12345678 IP核心寄存器定义为抵消0 x100使用之前定义的服务路径存储在变量中jtag美元。

% master_write_32 jtag x100 0 x12345678美元

您可以生成读写之前,您必须首先启动一个系统控制台的JTAG主控和打开一个连接寄存器读写的问题。

打开一个连接到JTAG的主人,首先设置一个变量,存储服务路径(在本例中,只有一个主存在)。

%设置jtag [lindex [get_service_paths大师]0]

使用变量来打开JTAG主在主模式。

% open_service大师jtag美元

启动阿尔特拉®系统控制台,输入命令来打开JTAG的主人。

系统(C: \ intelFPGA \ 17.1 \第四的\ sopc_builder \ bin \ system-console&”)

当你使用JTAG的主人,通过使用这个Tcl命令关闭连接。

close_service大师jtag美元

总结

您可以使用JTAG AXI经理IP与高密度脂蛋白编码器接口IP核心寄存器系统没有嵌入式ARM处理器,如马克斯10。您可以使用此IP作为第一步调试独立HDL编码器IP核,手工编码软件软处理器之前,(比如nio II),或作为一种优化参数在运行的系统。