FPGA针对工作流

您可以使用的硬件-软件(HW/SW)协同设计工作流程通讯工具箱™支持包USRP™嵌入式系列无线电金宝app只针对底层Zynq的FPGA结构®片上系统(SoC)。FPGA目标使用代码生成,将指定的子系统转换为HDL代码,并为FPGA结构创建自定义位流。这个自定义比特流然后被下载到开发板上的FPGA。通过将算法的部分或全部移动到硬件,可以加快主机的处理速度。您还可以将FPGA定位用于实际硬件上的原型设计。FPGA目标支持可用于接收路径金宝app和发送路径,一次一个。

资源利用率

FPGA资源利用率与软硬件协同设计工作流相同。有关概述,请参见USRP E310的默认FPGA资源利用率.

限制

使用双工操作发射机和接收机相同模型中的块只在针对ARM时出现®处理器采用完整的软硬件协同设计工作流程。建议发送或接收FPGA目标,但不能同时进行。

发射机FPGA瞄准和接收机FPGA瞄准不支持资源共享。金宝app

在你开始之前

为了只针对Zynq SoC的FPGA结构,您必须安装HDL Coder™和Xilinx的HDL金宝app编码器支持包®Zynq平台.

此外,还需要安装以下第三方工具:

Xilinx Vivado®开发工具,版本2019.1

要安装所有必需的软件产品,请遵循本文中列出的步骤下载188bet金宝搏软硬件协同设计的安装(跳过步骤4)。

步骤1。创建一个算法

在设计SDR算法时USRP嵌入式系列无线电,您设计的每个接收器和发射器模块必须满足以下Simulink金宝app®要求:

数量的渠道

USRP E310和E312支持两个通道。金宝app如果使用单个通道,则使用单个通道数据源。如果使用两个通道,则使用双通道数据源。在USRP E310设备上,RX2-A和TRX-A端口对应的是通道1,RX2-B和TRX-B端口对应的是通道2。

输入/输出信号的指导方针

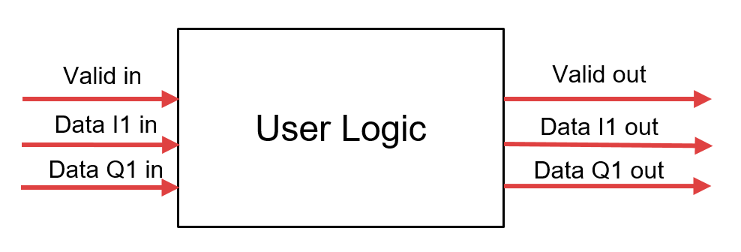

工作流对用户逻辑子系统的边界有特定的要求。下图显示了单通道用户逻辑子系统的数据和有效的用户逻辑输入和输出。多通道参考设计包括多组I和Q数据线。

每个数据输入或输出必须为16位。在HDL子系统的端口上不支持复杂的输入和输出。金宝app因此,实信号和虚信号必须在子系统边界上建模。

为给定的参考设计建模所有端口,即使端口没有被使用。

子系统的数据输入和输出使用独立的数据和有效的信号进行建模。在Si金宝appmulink中,数据和有效线必须以相同的采样率驱动。因此,各子系统的输入和输出时钟速率必须相等。

以HDL子系统中最快的速度对数据和有效信号进行时钟处理。

当有效的Tx数据输出信号被取消断言时,最后一个采样值将被保存。

当有效的Rx数据输出信号被去断言时,关联的样本不会被发送回主机。如果接收器用户逻辑中有很大的下采样因素,主机接收块就有超时的风险。

标量模式

对于HDL代码生成,您的自定义算法必须在标量模式下操作。方法可以将基于帧的输入信号转换为标量数据类型Unbuffer块。方法将输出转换回帧信号缓冲块。在这个范围内Unbuffer和缓冲块时,算法以标量模式运行,这是HDL代码生成所必需的。

步骤2。验证无线硬件连接

在将FPGA作为目标之前,主机计算机必须与无线电硬件通信。

对象创建一个无线对象

sdrdev函数。无线电= sdrdev (“E3xx”);调用。验证主机无线电通信

testConnection方法。testConnection(电台);

这个函数查询设备并返回成功或失败。

步骤3。设置第三方工具

设置系统环境,以便从MATLAB访问Xilinx Vivado®.的hdlsetuptoolpath函数使用指定的Xilinx安装文件夹,将所需的文件夹添加到MATLAB搜索路径。

例如:

在Windows中®:

hdlsetuptoolpath (“ToolName”,“Xilinx Vivado”,“路径”,...“C: \ Xilinx \ Vivado \ 2019.1 \ bin \ vivado.bat ')

在Linux中®:

hdlsetuptoolpath (“ToolName”,“Xilinx Vivado”,“路径”,...' / opt / Xilinx / Vivado / 2019.1 / bin ')

步骤4。使用HDL工作流顾问生成HDL IP核心

HDL IP核生成使您能够从Simulink模型自动生成一个可共享和可重用的IP核模块。金宝appHDL编码器从Simulink块生成HDL代码。金宝app通过使用SDR参考设计,可以创建一个集成到无线电硬件中的IP核。

在您对硬件子系统的仿真行为感到满意之后,生成HDL IP核,并将其与SDR参考设计集成。

设置

确保将HDL子系统视为一个原子单元。您可以通过右键单击包含该算法的子系统并进行选择来检查此设置块参数(子系统).

通过右键单击包含算法和选择的子系统来启动HDL Workflow AdvisorHDL代码>高密度脂蛋白工作流顾问.

答:设置目标

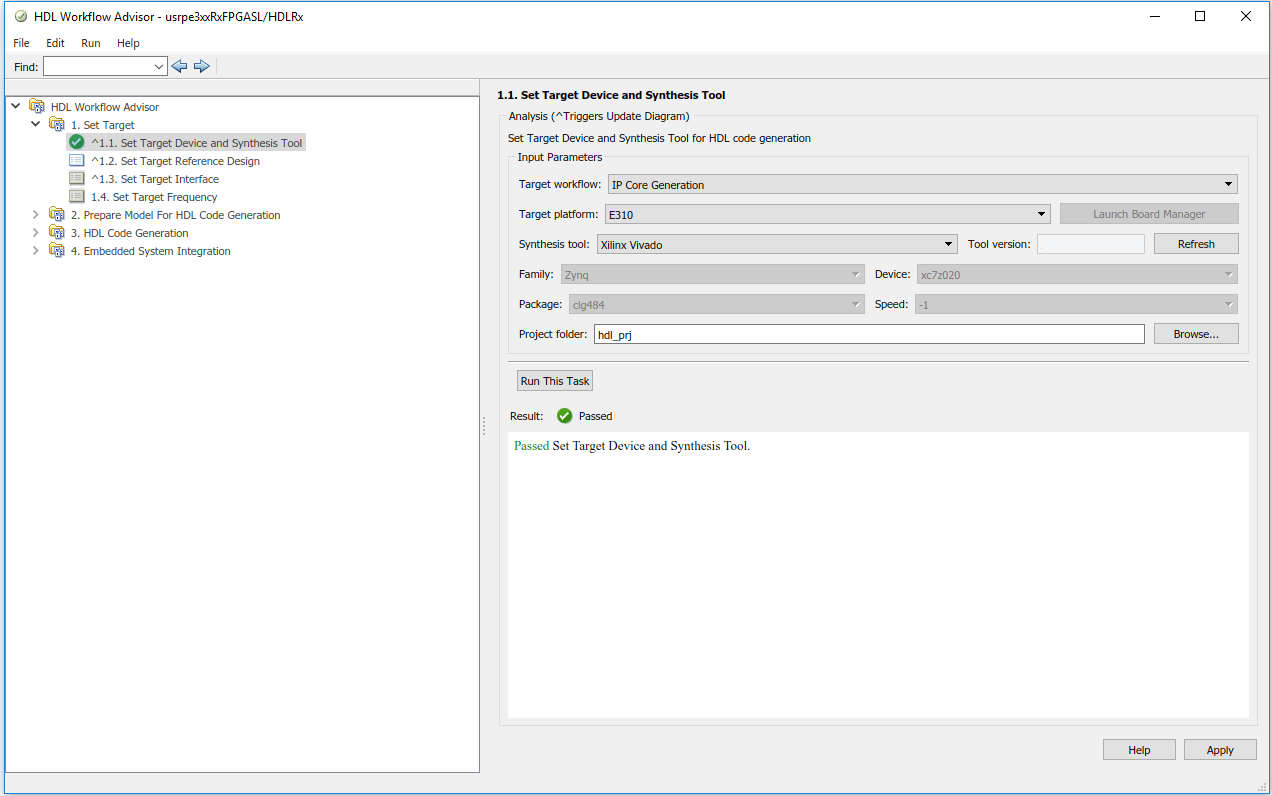

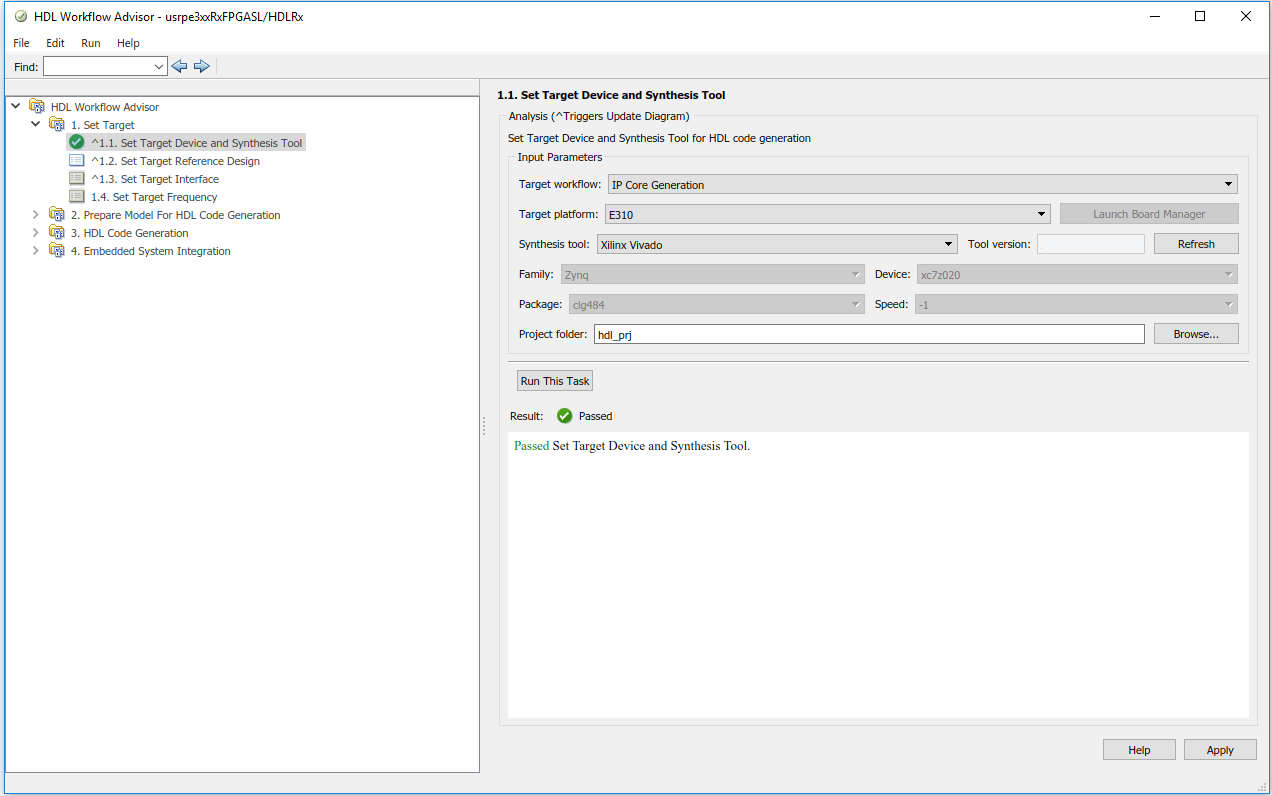

在工作流顾问步骤1.1中,选择

IP核心代为目标工作流程.然后选择E310或E312为目标平台.最后,选择

Xilinx Vivado随着合成工具.接受默认的项目文件夹,或输入项目文件夹位置的有效路径。所有其他字段将自动填充。

点击运行这个任务.

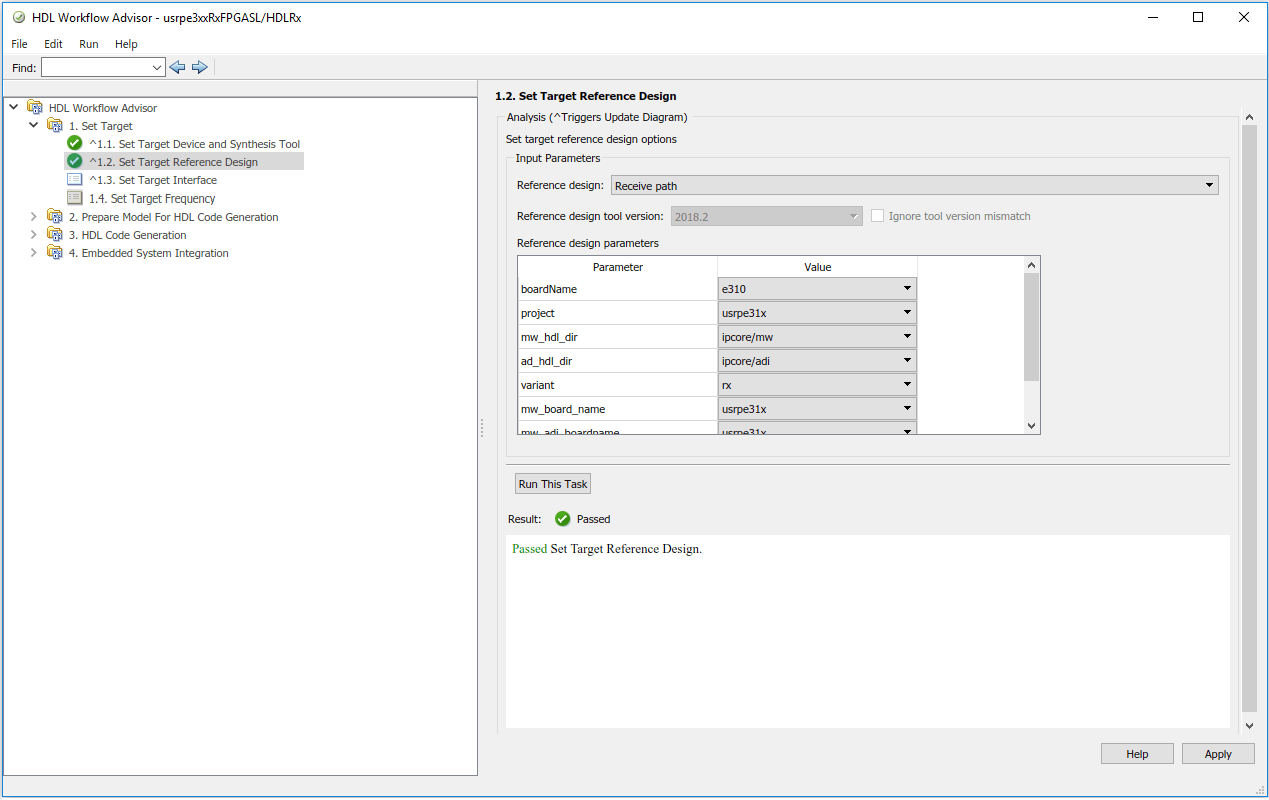

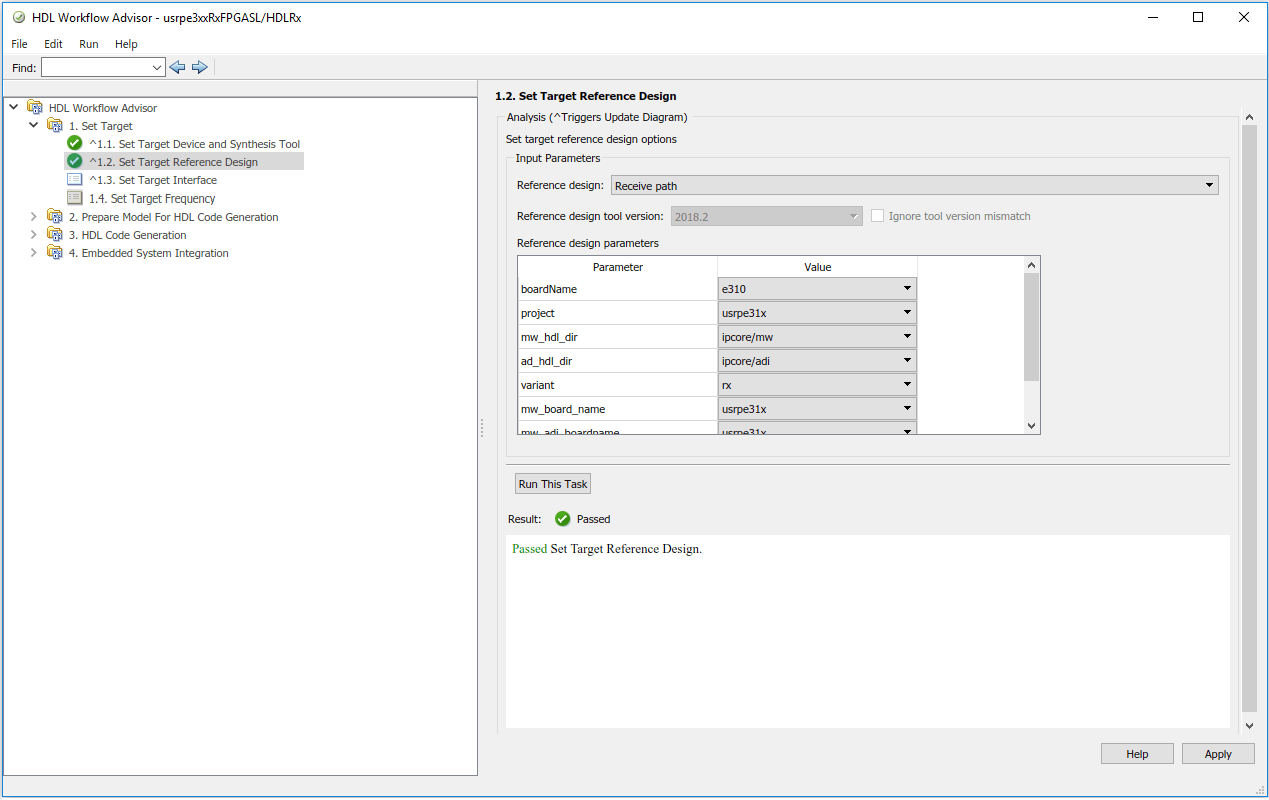

在Workflow Advisor步骤1.2中,为您的系统选择参考设计。请只选择下列选项之一:

接收路径传输路径

点击应用,然后点击运行这个任务.检查Workflow Advisor底部的日志文本区域中的警告,并在继续之前进行必要的更改。

在Workflow Advisor步骤1.3中,设置目标接口并验证处理器/ FPGA同步被设置为

自由奔跑.然后将用户逻辑映射到参考设计。当映射RF通道时,每个I和Q组件指的是用户逻辑上的16位端口。这个数字定义了通道名称。例如,基带Rx I1 In [0:15]对应射频卡上通道1的接收机实部。确保为每个端口选择了适当的目标平台接口。

点击应用,然后点击运行这个任务.

在Workflow Advisor步骤1.4中,为您的设计选择目标频率。

点击运行这个任务.

B.运行设计检查

在“工作流顾问步骤2”中,单击运行所有检查并准备HDL代码生成的设计。如果任何任务失败或发出警告,请尝试纠正该问题。在解决所有问题之前,您不能继续。

C. HDL代码生成

在“工作流顾问步骤3”中,单击运行所有为IP核生成HDL代码。

D.嵌入式系统集成

工作流顾问步骤4.1将IP核集成到SDR参考设计中,并生成Vivado项目。要创建项目,请设置合成的目标来

没有一个,然后单击运行这个任务.工作流顾问步骤4.2只需要在硬件软件合作设计工作流针对ARM处理器和FPGA结构。选择跳过这个任务,然后点击运行这个任务.

工作流顾问步骤4.3为FPGA fabric生成位流。要在外部外壳中生成比特流,请选择

在外部运行构建流程.有了这个选项,您可以在生成FPGA图像时继续使用MATLAB。点击运行这个任务.在执行了基本的项目检查之后,该步骤将在几分钟内完成,并且该步骤将被标记为绿色的复选标记。在继续之前,请在外部命令窗口中验证Vivado位流的构建是否没有打印错误。为Zynq硬件编程。

工作流顾问步骤4.4下载位流到设备。

在继续执行此步骤之前,请调用

zynq函数与以下语法,以确保MATLAB是与无线电硬件的正确物理IP地址。缺省情况下,无线硬件的物理IP地址为192.168.3.2。如果在硬件设置过程中更改无线硬件IP地址,则必须提供该地址。devzynq = zynq (“linux”,“192.168.3.2”,“根”,“根”,“/ tmp”);

在工作流顾问步骤4.4中,您有三个选项来下载位流。

与

下载时,位流在功率周期内是持久的(推荐)。与

JTAG时,比特流在电力循环中不是持久的

或者,如果要在Workflow Advisor之外加载位流,则调用

downloadImage函数。无线电= sdrdev (“E3xx”);downloadImage(广播,“FPGAImage”,...“hdl_prj \ vivado_ip_prj \ vivado_prj.runs \ impl_1 \ system_top.bit ')

这个函数调用重命名生成的文件

system_top.bit文件system.bit并通过以太网连接将文件下载到无线电硬件上。这个比特流在电力循环中是持久的。

第5步。验证硬件实现

答:取代子系统

创建一个单独的模型来测试和验证目标子系统。使用原始组件并将用于生成自定义比特流的子系统替换为向无线电硬件发送I/ o的子系统。

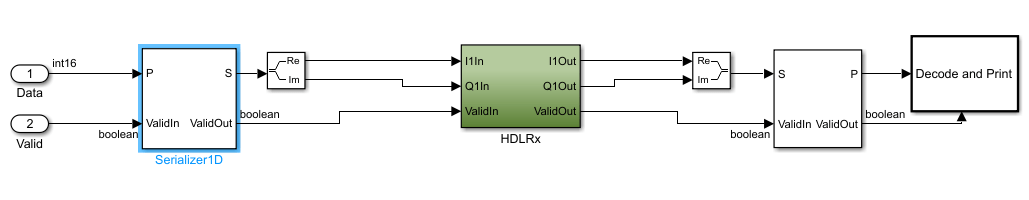

下面的例子展示了HDLRx子系统的这个过程。

HDLRx子系统的接收器

在以下重定向的hdl -优化接收机模型中,HDLRx子系统被移除。重定向模型只包含来自原始模型的解码组件。组成HDLRx子系统的组件现在在FPGA上实现。

过程模型

b .运行仿真

运行仿真。现在,该模型从算法输出生成实时数据。

另请参阅

功能

sdrdev|hdlsetuptoolpath(高密度脂蛋白编码器)|zynq(Xilinx Zynq平台的嵌金宝app入式编码器支持包)